本文转载自: Cadence楷登PCB及封装资源中心微信公众号

本文要点

BGA 封装尺寸紧凑,引脚密度高。

在 BGA 封装中,由于焊球排列和错位而导致的信号串扰被称为 BGA 串扰。

BGA 串扰取决于入侵者信号和受害者信号在球栅阵列中的位置。

在多门和引脚数量众多的集成电路中,集成度呈指数级增长。得益于球栅阵列 (ball grid array ,即BGA) 封装的发展,这些芯片变得更加可靠、稳健,使用起来也更加方便。BGA 封装的尺寸和厚度都很小,引脚数则更多。然而,BGA 串扰严重影响了信号完整性,从而限制了 BGA 封装的应用。下面我们来探讨一下 BGA 封装和 BGA 串扰的问题。

球栅阵列封装

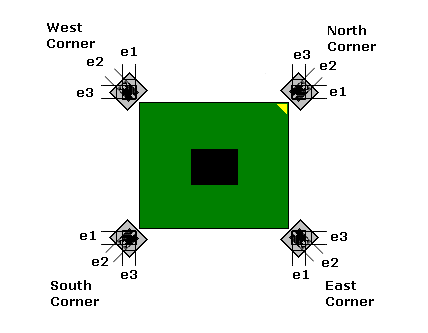

BGA 封装是一种表面贴装封装,使用细小的金属导体球来安装集成电路。这些金属球形成一个网格或矩阵图案,排列在芯片表面之下,与印刷电路板连接。

球栅阵列 (ball grid array ,即BGA) 封装。

使用 BGA 封装的器件在芯片的外围没有引脚或引线。相反,球栅阵列被放置在芯片底部。这些球栅阵列被称为焊球,充当 BGA 封装的连接器。

微处理器、WiFi 芯片和 FPGA 经常使用 BGA 封装。在 BGA 封装的芯片中,焊球令电流在 PCB 和封装之间流动。这些焊球以物理方式与电子器件的半导体基板连接。引线键合或倒装芯片用于建立与基板和晶粒的电气连接。导电的走线位于基板内,允许电信号从芯片和基板之间的接合处传输到基板和球栅阵列之间的接合处。

BGA 封装以矩阵模式在芯片下分布连接引线。与扁平式和双列式封装相比,这种排列方式在 BGA 封装中提供了更多的引线数。在有引线的封装中,引脚被安排在边界。BGA 封装的每个引脚都带有一个焊球,焊球位于芯片的下表面。这种位于下表面的排列方式提供了更多的面积,使得引脚数量增多,阻塞减少,引线短路也有所减少。与有引线的封装相比,在 BGA 封装中,焊球之间的排列距离最远。

BGA 封装的优点

BGA 封装尺寸紧凑,引脚密度高。BGA 封装电感量较低,允许使用较低的电压。球栅阵列的排列间隔合理,使 BGA 芯片更容易与 PCB 对齐。

BGA 封装的其他一些优点是:

由于封装的热阻低,散热效果好。

BGA 封装中的引线长度比有引线的封装要短。引线数多加上尺寸较小,使 BGA 封装的导电性更强,从而提高了性能。

与扁平式封装和双列式封装相比,BGA 封装在高速下的性能更高。

使用 BGA 封装的器件时,PCB 的制造速度和产量都会提高。焊接过程变得更简单、更方便,而且 BGA 封装可以方便地进行返工。

BGA 串扰

BGA 封装确实有一些缺点:焊球不能弯曲、由于封装密度高而导致的检查难度大,以及大批量生产需要使用昂贵的焊接设备。BGA 串扰是另一项限制,会影响通过 BGA 封装传输的信号完整性。

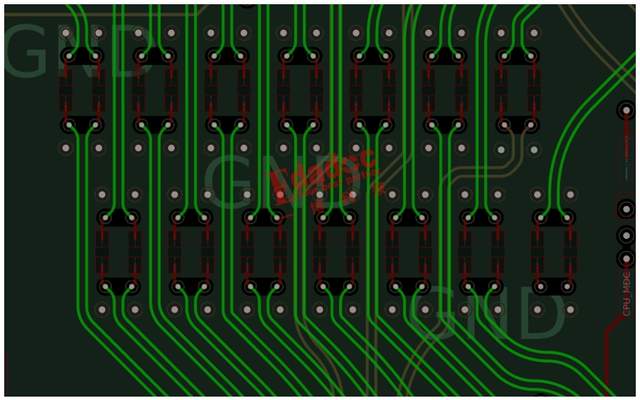

要减少 BGA 串扰,低串扰的 BGA 排列至关重要。

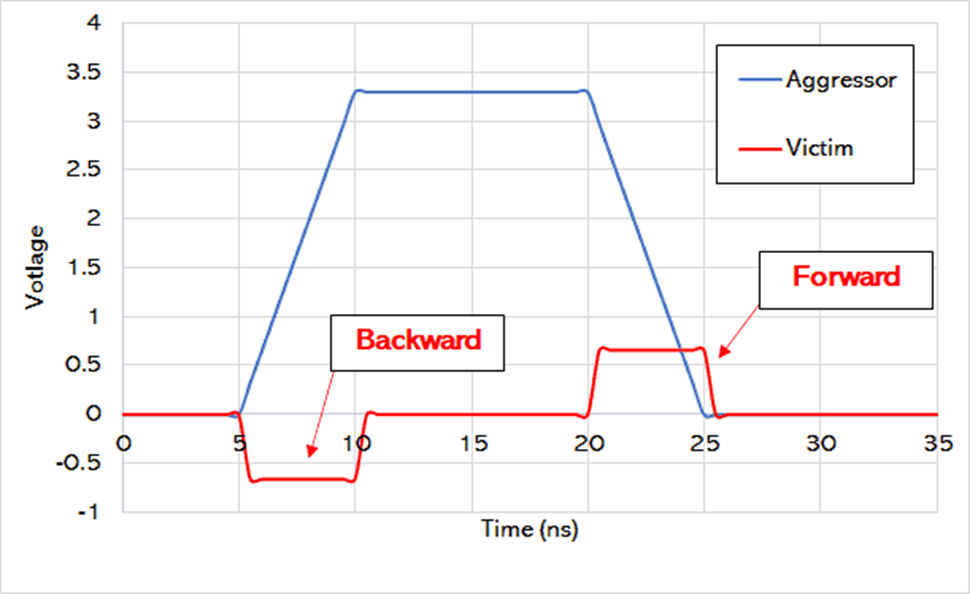

BGA 封装经常在大量 I/O 设备中使用。采用 BGA 封装的集成芯片所传输和接收的信号,可能会受到从一个引线到另一个引线的信号能量耦合的干扰。由 BGA 封装中的焊球排列和错位而导致的信号串扰被称为 BGA 串扰。球栅阵列之间的有限电感是 BGA 封装中产生串扰效应的原因之一。当 BGA 封装引线中出现高 I/O 电流瞬变(入侵信号)时,对应于信号引脚和返回引脚的球栅阵列之间的有限电感会在芯片基板上产生电压干扰。这种电压干扰导致了信号突变,并以噪音的形式从 BGA 封装中传输出去,导致串扰效应。

在网络系统等应用中,具有使用通孔的厚 PCB,如果没有采取措施屏蔽过孔,那么 BGA 串扰会十分常见。在这样的电路中,放置在 BGA 下面的长通孔会造成大量的耦合,并产生明显的串扰干扰。

BGA 串扰取决于入侵者信号和受害者信号在球栅阵列中的位置。要减少 BGA 串扰,低串扰的 BGA 封装排列至关重要。借助 Cadence Allegro Package Designer Plus 软件,设计师能够优化复杂的单裸片和多裸片引线键合(wirebond)以及倒装芯片(flip-chip)设计;径向、全角度推挤式布线可解决 BGA/LGA 基板设计的独特布线挑战;特定的 DRC/DFM/DFA 检查,更可保障BGA/LGA设计一次成功;同时提供详细的互连提取、3D 封装建模以及兼顾电源影响的信号完整性和热分析。

审核编辑 黄宇

-

封装

+关注

关注

128文章

9329浏览量

149039 -

Cadence

+关注

关注

68文章

1026浏览量

147311 -

BGA

+关注

关注

5文章

586浏览量

51947 -

串扰

+关注

关注

4文章

196浏览量

27872

发布评论请先 登录

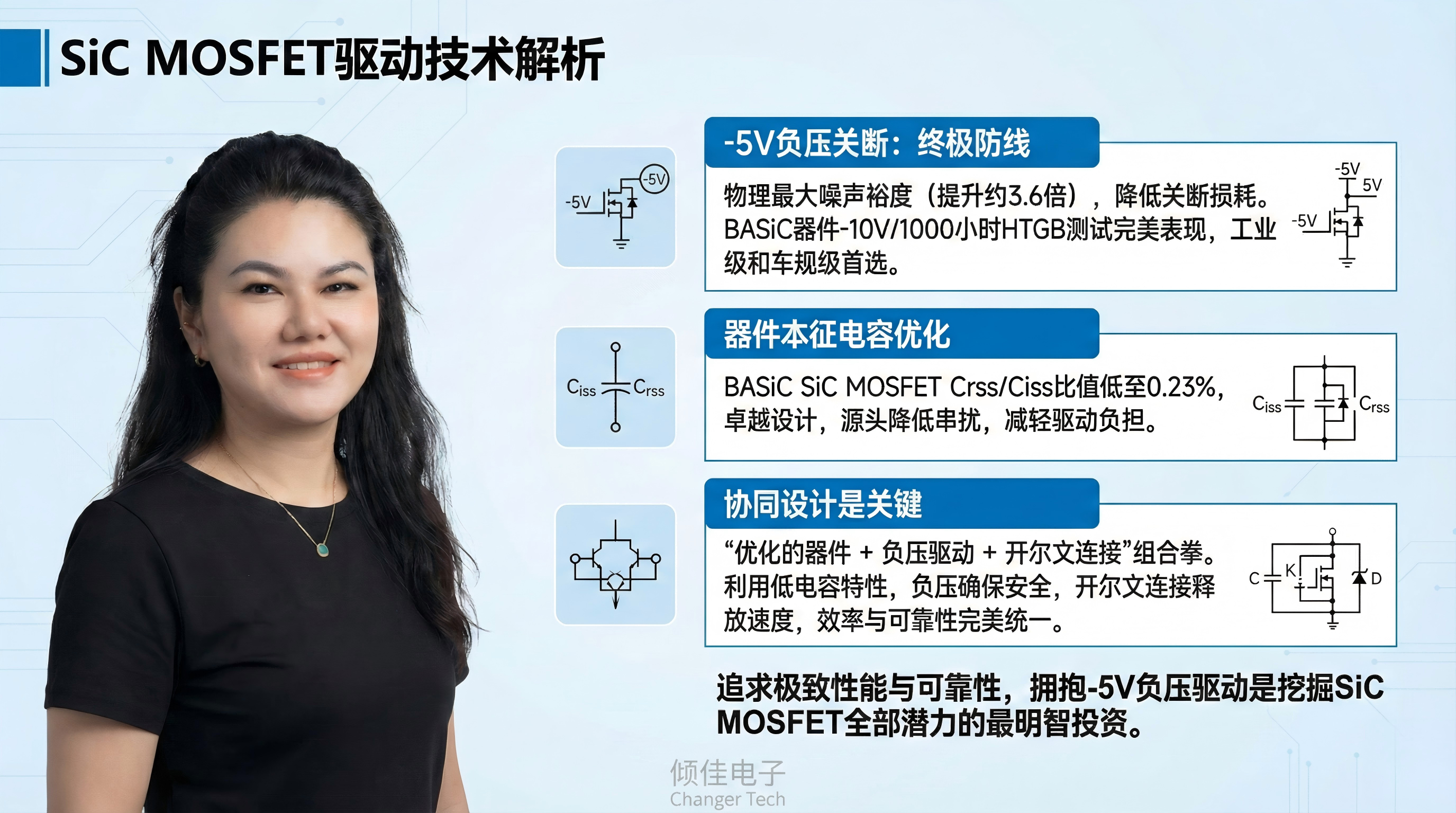

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势

GT-BGA-2002高性能BGA测试插座

EXCUSE ME,表层的AC耦合电容和PCB内层的高速线会有串扰?

PWM停止输出,什么原因会导致这种现象发生?

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

昊衡科技全新推出——偏振串扰分析仪OLI-P助力保偏光纤系统性能跃升

技术资讯 I 哪些原因会导致近端和远端串扰?

高速AC耦合电容挨得很近,PCB串扰会不会很大……

高速AC耦合电容挨得很近,PCB串扰会不会很大……

你知道什么原因会导致安规电容损坏吗?

NEXT(Near-End Crosstalk,近端串扰)

BGA失效分析原因-PCB机械应力是罪魁祸首

哪些原因会导致 BGA 串扰?

哪些原因会导致 BGA 串扰?

评论