一般我们在进行PCB设计时可能会留意到有些信号会串联一个电阻,那么大家是否有想过所串联的电阻是有什么作用呢?

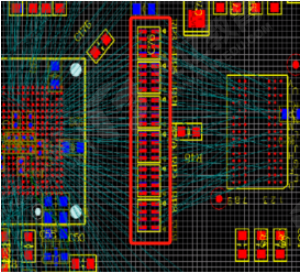

大家可以看一下下面图示的案例,信号是从CPU处出来再接到DDR颗粒的,每一个DDR数据线都有串联一个电阻,其实这个串联电阻的作用是进行阻抗匹配的,防止信号发生反射。

我们接下来用allegro软件自带的sigxplorer软件进行仿真验证一下,我们主要分析验证一下这个电阻他是如何进行阻抗匹配以及电阻阻值应该如何选取!

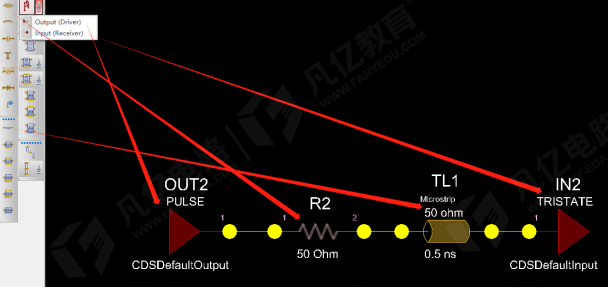

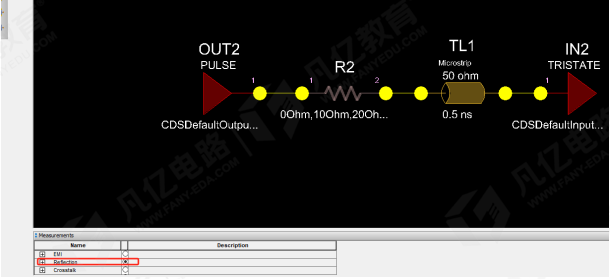

首先我们需要按照下图先对链路进行搭建,并且把传输线阻抗改为常规的单端50ohm,

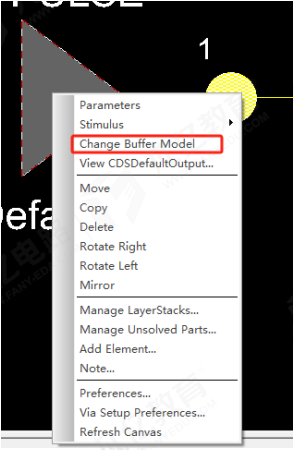

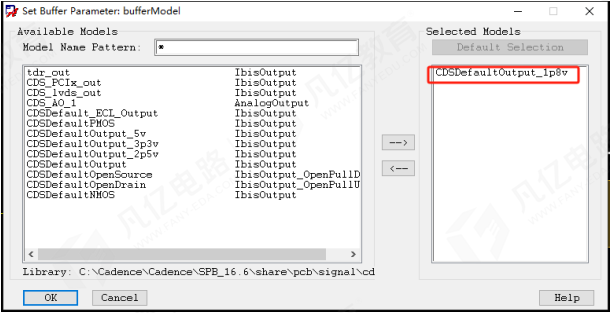

然后再把tx和rx的模型改为1.8v的高速模型

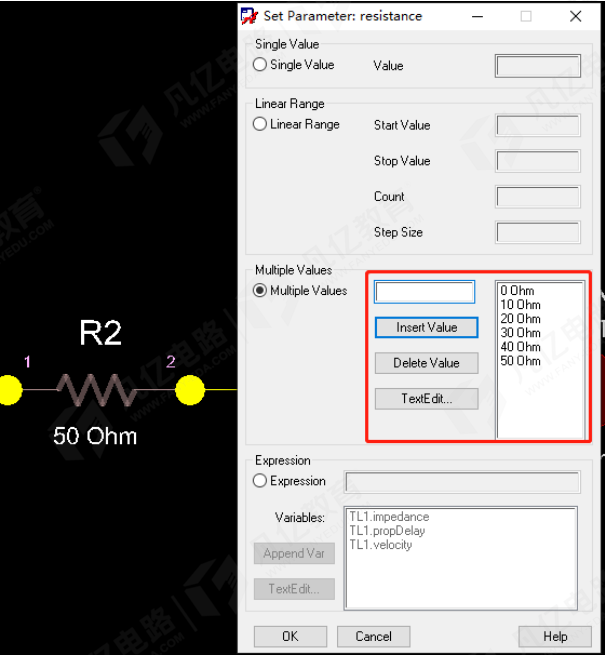

电阻的阻值大小我们分为6种情况进行仿真,如下图所示,看电阻大小对实际信号反射的改善效果,以及把模式切换成reflection,进行信号反射仿真

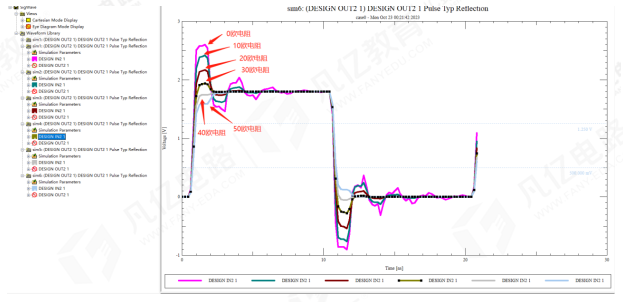

设置好前面的参数之后我们点击仿真,可以看到我们如下仿真的结果,rx端所接收到的波形,可以看到当我们前面没有串联电阻的时候信号会发生严重的过冲现象,当我们不断把电阻加大的时候我们会发现信号的过冲在不断的减小,但是当电阻为40欧姆和50欧姆的时候,信号的上升沿发生了欠冲的现象(上升沿变缓),当电阻在30欧姆的时候我们会发现信号的质量是最好的!

从上面的仿真结果我们知道电阻的大小会对波形产生不同的影响,而且电阻不是越大越好也不是越小越好,我们只有选择合适的串联电阻才能达到改善信号反射的效果。一般我们所选取的电阻大小为22-30欧之间,当然实际要确定这个阻值的具体大小最好是通过仿真验证决定或者在后期调试阶段可以更换电阻的阻值从而达到阻抗匹配的目的。

这其中的原理是因为在tx端有一个内阻(内阻不是一个固定值,他是会变化的),一般是小于50欧姆的,而传输线阻抗为50欧姆,两者阻抗不一致则会导致信号发生反射,我们在信号前面加一个电阻的作用则是为了改善信号的反射,使得信号内阻加上串接电阻的阻值等于或者接近传输线的阻抗,从而消除信号的反射。

以DDR为例,现在的DDR基本上都不会有串接电阻了,当然并不是说不需要这个电阻,是因为现在的DDR有了ODT技术,相当于把电阻集成到芯片内部了(而且电阻可调),所以我们外部的数据线是不需要添加串联的端接电阻了,但是需要注意的是,ODT技术是针对数据线来说的,不包含地址线,控制线,时钟线,所以地址线,控制线,时钟线如果不做处理的化也会有信号发生反射,除了串联端接外我们还有并联端接可以降低信号的反射,不同的端接方式有不同的应用场景以及有不同效果,这个电阻我们需要尽量靠近tx端进行放置才有效果,如果放置的过远则不会起到改善信号反射的效果,我们下次也可以验证一下电阻如果放置的过远信号的波形会产生什么变化。

声明: 本文凡亿教育原创文章,转载请注明来源!投稿/招聘/广告/课程合作/资源置换请加微信:13237418207-

pcb

+关注

关注

4417文章

23962浏览量

426090

原文标题:信号上的串联电阻是如何改善信号质量的

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

TUSB211A USB 2.0 高速信号调节器:提升信号质量的利器

信维高频MLCC电容,助力高速信号传输

信维高频陶瓷电阻,助力高速信号稳定传输

时钟信号对数字音频质量的影响

串联谐振的原理及基本性能

如何使用数据异常判断电能质量在线监测装置采样电阻是否损坏?

揭秘高频PCB设计:体积表面电阻率测试仪如何确保信号完整性

高扇出信号线优化技巧(上)

如何实现DAB高质量信号采集

信号上的串联电阻是如何改善信号质量的

信号上的串联电阻是如何改善信号质量的

评论