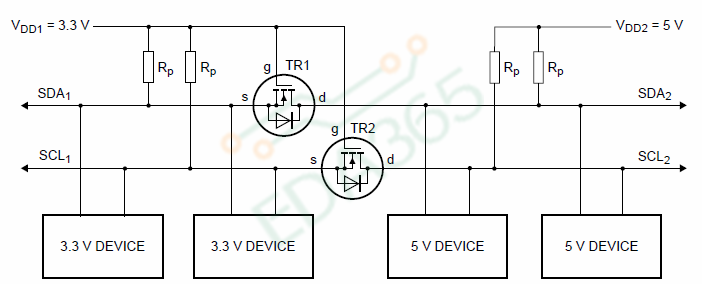

我们先来看一张图,熟悉I2C的人一看,这不是I2C的level shifter电路嘛,在Philip的I2C标准里面有,没有啥复杂的。

我们先来解读下这张图,I2C的level shifter是通过NMOS管来实现的,有人可能会问,为什么不用PMOS呢?一般情况下,只有在外部电源输入端,我们设计INRUSH电流缓启动或者防反插电路的时候才会用到PMOS。

理由很简单, PMOS是低电平打开,电源插入瞬间系统其实还没有用于打开MOSFET的高电平,所以只能选择PMOS, 而NMOS体积小,RDSON低,在系统内部会更多选择NMOS。

我们来举个PMOS的用例:

言归正传,我们来继续讨论I2C问题。首先我们要牢牢记住,I2C是Open-drain,所以level shifter电路的两边都是上拉电阻Rp的,下面讲下这个电路是怎么工作的。

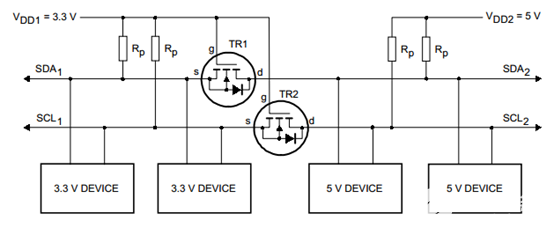

下图是两张I2C的基本操作时序图,分别是Master对Slave所做的读和写:

我们可以看到, SDA一定是双向的,既然是双向的,那么就有四种情况,我们来一一解释level shifter是怎么来cover它们的。(注意:这里面会含有一个Facebook的问题,不要忘记自测哦。)

01

第一步,Master往Slave发数据1

**1) **左边MasterSDA_1为输出,驱H-3.3V,NMOS的VGS=0, 此时NMOS关闭;

**2) **右边的Slave的SDA_2是输入,对外呈现高阻;

**3) **NMOS关断和SLAVE为输入,导致SDA_2悬空;

**4) **最终SDA_2依靠RP2上拉到5V,完成3.3V到5V的转换。

02

第二步,Master往Slave发数据0

1) 左边MasterSDA_1为输出,驱Low=0,NMOS的VGS>0, 此时NMOS打开;

**2) **右边的Slave的SDA_2是输入,对外呈现高阻;

3) NMOS打开和SLAVE为输入,导致SDA_2=SDA_1=0;

**4) **最终SDA_2被SDA_1拉到0,完成低电平的转换。

03

第三步,Slave往Master发数据1

1) 右边Slave SDA_2为输出,驱H-5V;

**2) **左边Master SDA_1为输入,对外高阻, 被RP1上拉到3.3V;

**3) **NMOS 因为VGS=0一直关闭;

**4) **NMOS关闭,Master SDA_1维持3.3V高电平,完成电平转换。

04

第三步,Slave往Master发数据0

**1) **右边Slave SDA_2为输出,驱LOW;

**2) **左边Master SDA_1为输入,对外高阻, 被RP1上拉到3.3V;

**3) **NMOS 因为VGS=0一直关闭;

**4) **NMOS关闭,Master SDA_1为3.3V高电平。

问题来了,我们看到右边的SDA_2位Low,但是左边的是SDA_1位High,那不是失败了嘛,不可能啊,这个电路是好的啊。

我们来看看下一步会发生什么,其实这个问题没有那么难,仔细看看这张图,还是比较容易发现线索的。

我们来揭晓答案: 大家看看上图的NMOS下面多了一个二极管,我们把这个二极管叫做Body Diode,它会在这个时候发挥作用。

**5) **由于左边SDA_1为高,右边SDA_2为LOW, Body Diode导通;

**6) **SDA_1被拉低,导致NMOS VGS>0 后打开;

**7) **NOMO打开后,SDA_1和SDA_2相当于短在一起;

**8) **最终左边SDA_1被右边的SDA_2拉低变为LOW。

我们看到由于体二极管的作用,打开NMOS管,使得右边Slave输出的L=0顺利到达左边的Master SDA_1输入端。

-

上拉电阻

+关注

关注

5文章

366浏览量

31719 -

电平转换

+关注

关注

3文章

182浏览量

35029 -

I2C总线

+关注

关注

8文章

422浏览量

63492 -

PMOS

+关注

关注

4文章

274浏览量

31714 -

SDA

+关注

关注

0文章

125浏览量

29743

发布评论请先 登录

I2C总线电平转换芯片在安防产品的应用

PCA9306 I2C总线和SMBus双向电平转换器简介

I2C双向电平转换电路

mos管电平转换电路原理与mos电平转换电路分析

硬件设计:接口--不同电源系统下I2C总线电平转换电路(电桥)设计

TCA9509电平转换I2C和SMBUS总线中继器数据表

I2C总线—电平转换

I2C总线—电平转换

评论