锁相环锁定时间取决于哪些因素?如何加速锁定?

锁相环(PLL)是一种常见的电路,用于稳定频率。PLL中的关键是相锁。相锁发挥着将输入频率与参考频率调整到相等的重要作用。在锁相环设计中,锁定时间是一个重要的参数。锁定时间越短,PLL就能更快地响应频率的变化。因此,减少锁相环锁定时间对于实现高效的电路设计非常重要。

锁相环锁定时间取决于以下因素。

1. 滤波器:锁相环的滤波器可以影响其锁定时间。滤波器的带宽越大,则锁定时间越短。因此,提高锁相环滤波器的带宽是减少锁定时间的一种方法。

2. 反馈环路:锁相环的反馈环路也会影响锁定时间。如果反馈信号的准确度不够高,则锁定时间会更长。因此,提高反馈信号质量可以加速锁定时间。

3. 比例增益:比例增益也可以影响锁定时间。增加比例增益可以提高锁定时间。但是,过高的比例增益可能会导致锁相环不稳定。因此,需要在增加比例增益和保持锁相环稳定之间进行权衡。

4. 相位检测器:相位检测器的性能可以影响锁定时间。如果相位检测器的响应速度很慢,锁定时间也会更长。因此,改进相位检测器的响应速度可以有效地缩短锁定时间。

因此,缩短锁定时间有以下方法:

1. 提高锁相环的滤波器带宽。

2. 优化反馈信号的质量,以提高精度和可靠性。

3. 适当增加比例增益,并保持锁相环的稳定。

4. 改善相位检测器的响应速度。

在实际应用中,还可以采用以下一些方法。

1. 提前对锁相环进行初始化:在拥有大量相位偏差的情况下,初始化锁相环可以减少锁定时间。

2. 应用逐步逼近锁定:这是一种逐渐加大参考频率的过程,从而使锁相环可以逐步逼近锁定的频率。通过这种方法,可以更快地实现锁定。

3. 预定锁定:预定锁定是通过预测可能的输入频率来提前调整锁相环,从而减少锁定时间。这种方法需要较高的计算能力和复杂的算法。

总之,锁相环的锁定时间受许多因素的影响。在优化锁定时间时,需要渐进式应用这些因素。需要注意平衡这些因素,以达到较优的锁定时间和稳定性。

-

锁相环

+关注

关注

36文章

637浏览量

91310 -

滤波器

+关注

关注

162文章

8476浏览量

186317 -

pll

+关注

关注

6文章

991浏览量

138400

发布评论请先 登录

高性能低噪声锁相环LTC6948:设计与应用全解析

上海微系统所在太赫兹半导体激光器光注入锁定方面取得进展

锁定放大器工作原理 锁定放大器和锁相放大器的区别

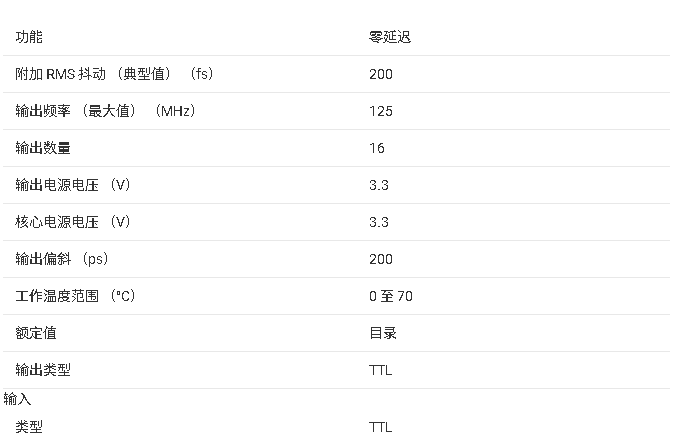

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC509:高性能3.3V锁相环时钟驱动器

CDCVF25081:高性能锁相环时钟驱动器深度解析

TLC2932A高性能锁相环芯片详解:设计与应用指南

探索TLC2933A高性能锁相环:特性、应用与设计要点

模数转换器(ADC)的最高使用频段取决于哪些因素

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDC516 3.3V相位锁定环时钟驱动器技术文档总结

基于锁相环的无轴承同步磁阻电机无速度传感器检测技术

高压放大器在锁相环稳定重复频率研究中的应用

锁相环锁定时间取决于哪些因素?如何加速锁定?

锁相环锁定时间取决于哪些因素?如何加速锁定?

评论