引言

在近代战争中,军事信息传递,例如通过发电报的方式,电报信息难免被敌方截获,而我们又不得不通过发电报传输信息(哟,都近代了,就别飞鸽传书了),所以发送方需要对信息进行加密,也就是编码,然后以一种双方事先沟通好的编码方式(密码本就是这样来的),在接收方再进行反编码,也就是解码,这样,即使信息被截获了,短时间内也难以被破解;这就是编码器的重要性。

编码器的逻辑功能就是将多输入的每一个高、低电平信号转为一个对应的二进制代码,它分为普通编码器和优先编码器。对于普通编码器,任何时刻只允许输入一个编码信号,否则输出将发生混乱。

一、普通编码器的 Verilog 代码实现和 RTL 电路实现

module Encoders(

input wire [7:0] d, // 输入信号_未编码

output reg [2:0] b = 3'b000 // 输出信号_已编码

);

always @ ( d ) begin

case ( d )

8'b0000_0001 : b <= 3'b000;

8'b0000_0010 : b <= 3'b001;

8'b0000_0100 : b <= 3'b010;

8'b0000_1000 : b <= 3'b011;

8'b0001_0000 : b <= 3'b100;

8'b0010_0000 : b <= 3'b101;

8'b0100_0000 : b <= 3'b110;

8'b1000_0000 : b <= 3'b111;

default : b <= 3'b000;

endcase

end

endmodule

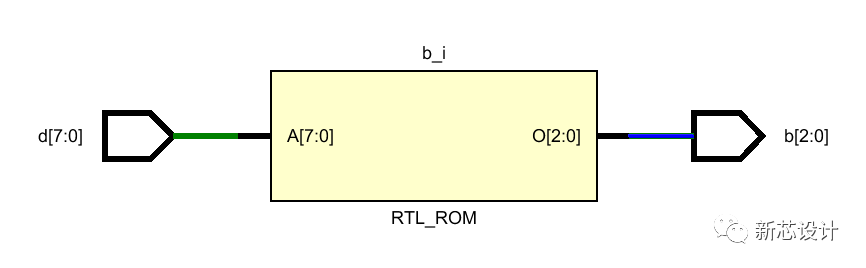

这是一个 8 线 − 3 线普通编码器,基于查找表 LUT(Look Up Table)的方式实现的一个电路,其 RTL 电路图如下所示:

普通编码器的 RTL 电路图

优先编码器其实就是允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最高的一个进行编码,即已经排好了队,从高位向低位递减。比如,8 线 - 3 线优先编码器的输入有 “0、1、2、3、4、5、6、7” 八位输入,而输出只有 “Y0、Y1、Y2” 三位输出,在这里,就是当 “7” 为 “1” 的时候,即 “7” 为有效值的时候,无论 “0” 到 “6” 之间为何值,都只对 “7” 进行编码,高位优先判断是否有效,以此类推。

二、优先编码器的 Verilog 代码实现和 RTL 电路实现

module Encoders(

input wire [7:0] d, // 输入信号_未编码

output reg [2:0] b = 3'b000 // 输出信号_已编码

);

always @ ( d ) begin

casex ( d )

8'b0000_0001 : b <= 3'b000;

8'b0000_001x : b <= 3'b001;

8'b0000_01xx : b <= 3'b010;

8'b0000_1xxx : b <= 3'b011;

8'b0001_xxxx : b <= 3'b100;

8'b001x_xxxx : b <= 3'b101;

8'b01xx_xxxx : b <= 3'b110;

8'b1xxx_xxxx : b <= 3'b111;

default : b <= 3'bxxx;

endcase

end

endmodule

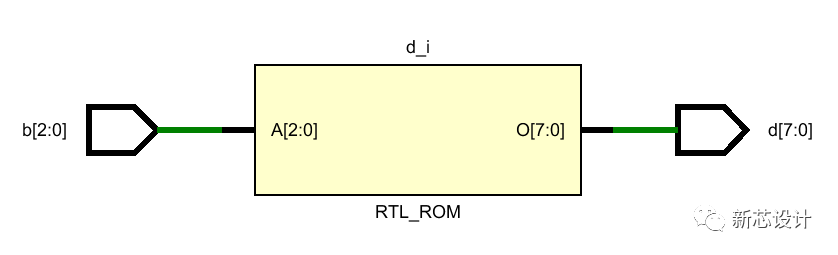

这是一个 8 线 − 3 线优先编码器,基于查找表 LUT(Look Up Table)的方式实现的一个电路,其 RTL 电路图如下所示:

优先编码器的 RTL 电路图

附加说明,其实,Verilog 中的 if - else 语句便隐含了优先特性,可以进行优先编码器的设计。中级及以上的 FPGA 玩家应该能懂的。

总结

编码器是非常重要的一个数字电路组合逻辑模块,不仅可以大大减少传输数据的信号线的数量,还是密码学的一部分,基于某种协议的编码能够让双方之间的通讯较为安全。

-

编码器

+关注

关注

45文章

3903浏览量

141443 -

RTL

+关注

关注

1文章

393浏览量

62394 -

LUT

+关注

关注

0文章

52浏览量

13074 -

Verilog设计

+关注

关注

0文章

20浏览量

6720

发布评论请先 登录

招聘:数字电路设计师

数字电路设计的基本方法有哪些

基于LabVIEW的数字电路设计和仿真

高速数字电路设计

Verilog数字系统设计——复杂数字电路设计2(FIFO控制器设计)

基于Verilog的经典数字电路设计(5)译码器

基于Verilog的经典数字电路设计(4)编码器

基于Verilog的经典数字电路设计(4)编码器

评论