数字电路设计全流程解析来啦!

数字电路设计是数字电路最为关键及重要的一步,今天我们将从各个流程为大家介绍完整的数字电路设计!

1总述

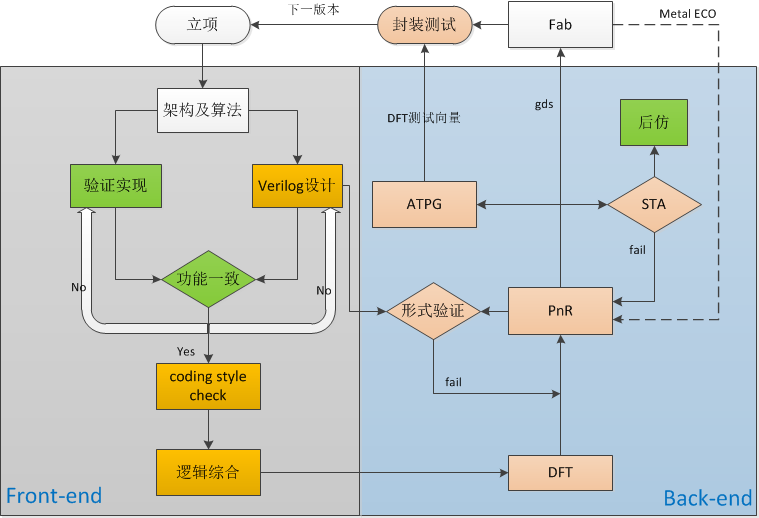

数字电路设计的基本流程如下图。大致可以分为立项,架构和算法,设计/验证,代码风格检查、综合、DFT设计、后端PnR,静态时序分析STA,后仿,流片,封装测试。之后根据测试的结果又会反馈给下一代的项目形成一个良性的循环。

理论上,流片过程中必须的环节是Verilog设计、逻辑综合和后端布局布线,因为只要有这三步,我们就能够把一个行为级的Verilog代码转换成门级网表,再通过PnR转换成版图GDS(Fab所需的版图二进制文件),再把版图GDS release给Fab完成流片过程。除此之外其他所有的工序和步骤都是为了保证所设计代码的功能和时序是符合要求的。毕竟在随着制造工艺越来越先进到如今的3nm时代,一次流片的成本需要几千万美金。流片失败的代价是非常大的。不仅错过了产品的市场窗口,同时也对资金的损失非常大。所以我们需要越来越多额外的工序、需要越来越复杂的验证方法学保证设计的正确性。

2数字电路设计流程分步骤解析

立项:从市场调研确定需要做一颗什么样的芯片,芯片的功能是哪些。具体指标要达到什么程度,市面的竞争对手有哪些。成功流片能够拿到多少市场份额,能够对公司产生多少利润,现金流等等

确定需要投入到这颗芯片的人力、物力和财力。规划好芯片的流片时间,制定项目计划和进度表。安排所有人员的工作以及schedule并随时跟踪

架构计算法:算法部门通过仿真建模确定每个部分的计算精度,量化控制,以及采用的计算方式等等

Architecture部门确定芯片的整体布局和架构,确定芯片最顶层的工作模式,子模块之间如何联动工作,芯片的性能,功耗,面积等各种参数

Verilog 设计:本课程的重点内容。

课程详情及试听课进入小程序查看:

通过Verilog这种硬件描述语言实现所需的各种功能。

注意设计中所有的代码必须是可综合代码

验证:另一门验证课程的重点内容

课时介绍:

课程详情及试听课进入小程序查看:

如何用system Verilog以及UVM对被测RTL进行逻辑功能的验证

主要集中考虑如何创建更多的测试用例保证所有的输入组合都能够遍历到,同时在所有遍历输入时输出都是符合预期的

通过代码覆盖率、功能覆盖率等保证验证的完备性

同时考虑验证平台的自动化,可移植性和可复用性等等

Coding Style check:一般采用spyglass工具。检查电路中的代码是否有潜在的问题。比如多个数相加导致的潜在溢出问题。异步复位信号又被当成逻辑信号使用,某一个信号即被当成异步复位,又被当成异步置位、赋值位宽对不上、实例化时信号对应不上等等

同时也会检查设计中所有的异步设计是否有防止亚稳态传播的电路

逻辑综合:本课程后续会讲解逻辑综合的基本流程

目的是在时序和面积等约束下把RTL的行为级Verilog代码转换成对应工艺的门级网表。同时产生约束文件并一起给后端进行布局布线

DFT和ATPG:DFT和ATPG本身和芯片的功能是没有任何相关性的。

目的主要是为了能够检查出Fab在制造过程中意外引入的缺陷。尤其是Fab良率不高时尤其重要

DFT的原理是通过把设计中的每一个触发器转换成带扫描链端口的触发器,从而能够给设计中的每一个触发器都赋一个初值。然后通过不同的初值能够遍历电路内部每一条线的状态,从而确定版图中的每一条在制造过程中是否有缺陷

ATPG则是根据DFT的扫描链产生出这些测试所需要的测试向量。并把测试向量以及期望输出结果一起给ATE。ATE由此可以对每一个芯片进行筛选判断其是否有制造缺陷

布局布线PnR:

课程详情及试听课进入小程序查看:

目的是在约束文件的控制下,把综合产生的门级网表生成对应工艺的物理版图。并完成版图直接的连线

其中主要步骤有FloorPlan,CTS, Placement, Route, DFM等

一般由专门的后端人员负责。尤其是对于IP众多,连线以及DRC规则复杂的芯片

形势验证:目的是比较两个待测设计的逻辑是否完全一直

其中比较的点主要集中在所有的输出端和触发器端

常用case1:比较综合后的网表和RTL网表是否一致,防止综合工具引入的意外错误

常用case2:比较综合后网表和后端网表是否一致,防止后端工具引入错误

常用case3:比较ECO后网表和同样ECO后RTL功能是否一致,保证网表的ECO功能是符合预期的

静态时序分析STA:主要应用于所有的同步电路设计,检查其中时序是否符合要求,对异步电路是不起作用的。

实际的制造过程中离子注入掺杂等不可能完全均匀,芯片在工作中温度和电压也不可能完全不变,为了保证芯片的时序在合理范围内都能正常。需要通过STA工具保证芯片在每一种PVT(工艺,电压,温度)组合下时序都能通过

同时STA工具在发现时序问题后还可以进行时序修复

后仿:速度非常慢,比前仿慢数十倍,所以一般只跑几个典型的工作场景

理论上STA和形势验证已经能够保证电路中所有同步电路都能正常工作,但有两种情况还是需要后仿的辅助:一是设计中时序的约束意外写错了,只能通过后仿发现。二是设计中异步电路的问题也只能通过后仿才能发现

流片 Tape Out:把后端生成的GDS二进制文件发送给Fab

一般需要2~3个月完成

掩膜版是流片中最贵的部分。一般Fab会把制造过程大致分为两个阶段。第一阶段是基础Base layer掩膜版制造阶段。此时若设计发现问题,可以通过修改metal解决,那么metal层的掩膜版可以直接用新的。节省资金。第二阶段是metal层掩膜版制造。此时如果发现问题并可以通过修改metal解决,那么只能重新制造掩膜版,但相比完整重新流片还是可以节省不少时间和资金

ECO:如前所述,芯片在制造或者测试过程中发现问题,如果流程从头开始走一遍来修复该问题,费时长同时消耗资金。

如果发现的问题比较简单。能够使用电路中预留的冗余单元,并修改一些金属连线就能修复该问题,那么就可以极大的节省时间和开支

此过程修改只能直接基于网表,为了保证网表修改没有错误,需要用形势验证工具保证修改后的网表功能和直接改RTL功能是一致的

封装与测试:根据芯片的速度、功耗等要求可以进行Flip-chip,BGA等各种封装

一般先由ATE进行芯片筛选。筛选后通过的片子再进行进一步的功能测试

测试发现的问题需要设计和验证人员进行复现。确定能够复现问题后再决定是否需要修改,或者可以在软件层面绕过

审核编辑:汤梓红

-

电路设计

+关注

关注

6746文章

2798浏览量

220241 -

Verilog

+关注

关注

31文章

1374浏览量

114723 -

数字电路

+关注

关注

193文章

1668浏览量

83537

原文标题:【干货】数字电路设计全流程是什么样的?

文章出处:【微信号:feifeijiehaha,微信公众号:电路和微电子考研】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

有源逻辑探头的具体应用

掌握数字设计基础:迈向芯片设计的第一步

SOSET索斯特分享:无源晶振电路设计指南

高速数字电路设计与安装技巧

华大九天Empyrean Liberal工具助力数字集成电路设计

老工程师分享的模电设计经验

如何学好电路设计?(文末分享电路设计资料合集)

数字电路设计的基本流程

数字电路设计的基本流程

评论