1 电感性间断引起反射及时延

几乎每种增加到传输线上的串行连接都伴随有环路电感 。用于改变信号层的通孔,串联端接电阻,连接器 , 等都有额外的环路电感。

如果信号路径中存在不连续性,环路电感主要由信号路径的部分自感决定,尽管在返回路径上存在部分互感。如果运回路径上存在不连续性,返回路径的部分自感将决定环路的电感。不管是哪种情况,信号对环路自感都是敏感的, 因为信号是电流回路, 沿着信号路径和返回路径之间来传播的 。

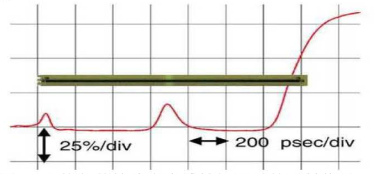

对于一个瞬时的,快速上升时间的信号来说,串行环路电感最初看起来是一个高的阻抗。导致正的反射回到源端。 下图表明 了在返回路径上的一个小间隙产生感性的间隔的情况下 , 均匀传输线的反射信号 。

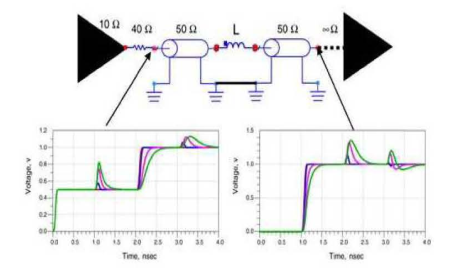

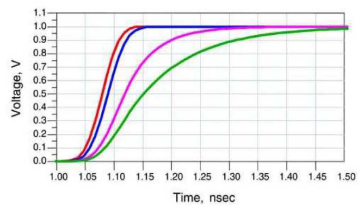

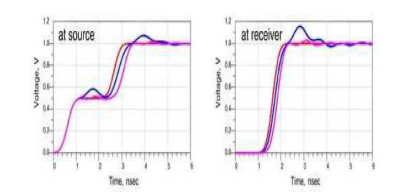

下面的仿真则表明了当电感间隔的值不同时, 在接收端和源端的信号 。信号的上升时间为50psec,电感值分别为 0 , 1 , 5, 10nH 。在近端, 信号先上升然后又下降 , 这种情况叫非单调性。这种特性本身不会导致信号完整性问题。

然而, 如果在近端放置接收器, 它接收到的信在超过幅值50% 的点时然后会下降到幅值的 50% 以下,这将会导致错误的触发 。非单调性行为应该尽可能的避免。在远端,发射信号会显示过冲和时延。

通常,电路中可接受的电感的最大值依赖于噪声的容限和电路的其它特性 。当离散的电导致走线特性阻抗增加20%时,反射信号大约为信号摆幅的10% ,通常这是反射噪声最大的可接受的值。

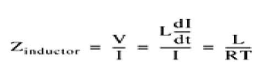

如果电感的阻抗值与特性阻抗相比很小,并且上升时间为线性斜面时,我们可以估计出电感的阻抗。

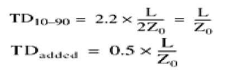

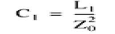

估计最大可允许的电感的阻抗, 如下式 :

电感性间隔还会增加延时, 当上升时间很短,并且发射信号的上升时间由串联电感决定,发射信号上升时间大约为 :

TDadded =信号上升到幅值的50%时的时延, 单位 ns

下图表明了在电感性间隔分别为 0 , 1,5, 10nH时, 对时延的比较 。

2 对环路电感的补偿方法

通常,电路中的串联环路电感是不可避免的,特别是电路本身已设计有一个连接器 。这会导致产生过量的反射噪声。可以通过补偿的方法来消除部分噪声。

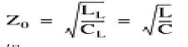

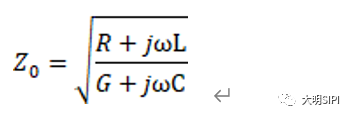

理想的传输线可近似为一个 n 段的 LC 网络,任一段的特性阻抗为:

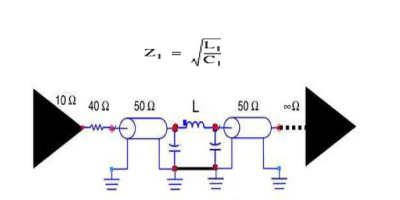

电感性间隔可以通过在两边增加小的电容,转换到传输线的片断。如图所示 。在种情况下,电感的表现性阻抗为;

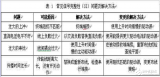

为了减小反射噪声,目标就是要找到合适的电容值,使连接器表观的特性阻抗 Z1 与剩余电路的特性阻抗Z0相等。按照上面的关系,增加的电容值为:

例如, 连接器的电感为10nH,走线的特性阻抗为50欧姆,要增加的补偿电容为 10/50^2=0.004nF=4pF。为 了达到最佳补偿,需要的电感的两端各分配一个2pF的电容。

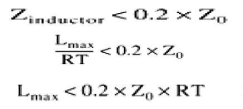

下图所示是三种情况下的发射信号和反射信号,没有连接器,带有连接器但是未被补 , 经过补偿的连接器 。 该图仿真的是10nH 的 电感性间隔, 上升时间为0.5ns 。经过补偿的连接器是在电感两边各放置一个2pF的电容。

这种补偿方法也同样适用于其它的电感性问隔存在的情况,比如通孔,电阻等 。

-

串联电阻

+关注

关注

1文章

235浏览量

15498 -

电感器

+关注

关注

20文章

2637浏览量

73200 -

接收器

+关注

关注

15文章

2638浏览量

76348 -

连接器

+关注

关注

102文章

15955浏览量

145493 -

信号完整性

+关注

关注

68文章

1473浏览量

97776

发布评论请先 登录

信号完整性学习笔记

【连载笔记】信号完整性-基本含义

信号完整性(五):信号反射

信号完整性简介及protel信号完整性设计指南

信号完整性学习笔记之电感对反射的影响

信号完整性学习笔记之电感对反射的影响

评论