在这个技术日新月异的时代,一个不争的事实是,我们已经迈入了芯片集成度迅速提升的阶段。随着5G、自动驾驶、人工智能等领域的飞速发展,对芯片性能的需求也急剧增加。这种挑战驱动芯片制造商走向更高的集成度,增加更多的晶体管,引入先进的光刻技术,并不断探索尖端的芯片工艺和封装方式。

一颗表面微小的芯片内部蕴藏着千丝万缕的设计细节。因此,对芯片设计的电路布局、连线以及物理特性进行及时的验证和确认至关重要。哪怕是一小步的差错,都有可能导致整体失效,这凸显了物理验证在芯片设计中的关键地位。

物理验证在先进芯片设计中的核心地位

近年来,“Shifting left”策略在芯片产业中受到了广泛关注。其核心目标是应对现代芯片设计的高复杂度,尽早在物理设计阶段进行验证,帮助设计团队及时纠正错误,以保证最后的设计准确无误,为最终流片做好充分准备。在此策略中,物理验证的重要性不言而喻。

物理验证主要包括设计规则检查(DRC)、布局与原理图(LVS)检查和面向制造设计检查(DFM)。在整个芯片设计项目中,一旦系统芯片(SoC)的主要部分组装完成,就可以开始进行DRC和LVS的验证。开发团队应当在每个设计阶段,如宏设计、IP和块级设计阶段,无缝且清晰地进行物理验证。与全芯片的组装并行地进行物理验证是更为高效的做法。

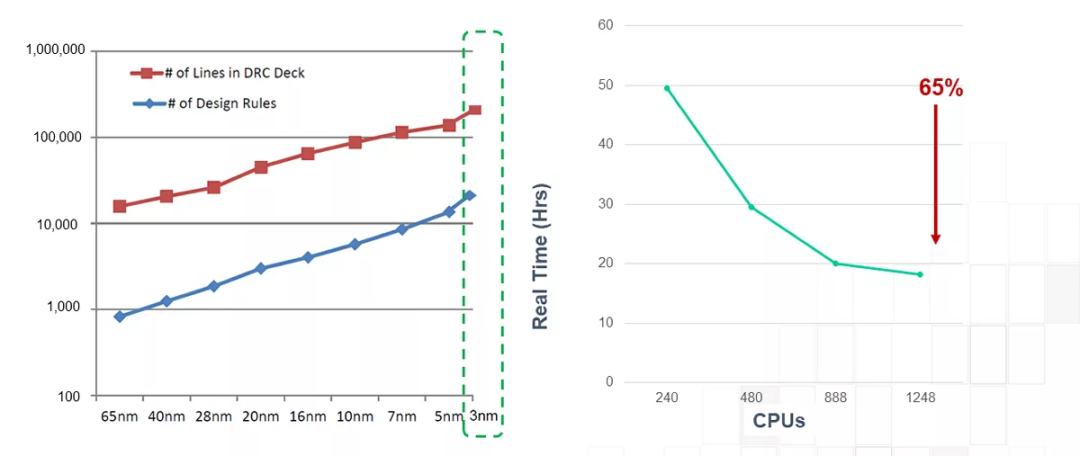

尽管物理验证一直都是计算密集型的工作,但如今的芯片设计尺寸和复杂性又将这一挑战提升到了一个全新的层次。对于拥有数十亿晶体管的多芯片系统而言,一个DRC或LVS的任务可能需要使用数百个CPU核,运行数天。随着工艺节点从7nm到5nm,再到3nm的进步,这一问题尤为突出。

在大型SoC的设计中,我们往往需要处理数百个组件,包括布局与路由块、模拟单元、存储器、第三方IP和I/O单元。尽管在设计过程中,这些组件各自可能都已经经过详细的DRC检查,但当它们被集成为一个完整芯片时,又会暴露出大量另外的设计问题,例如组件之间得位置不对齐,就可能触发大量的DRC违规行为。传统的DRC工具需要数日才能完成对如此庞大的设计的初次检查,这可能导致在项目的最后阶段,浪费流片输出团队大量额外的计算时间。

与此同时,LVS工具的发展也面临着相似的挑战。在现代的大规模电路设计中,LVS检查可能耗费数天时间。初次整合所有设计组件后,LVS可能会揭示出如宏/IP问题、顶层整合错误和界面引脚对齐问题等新问题。虽然这些问题本身可能容易修复,但它们确实会延长LVS的运行时间并增加计算要求,从而阻碍设计师的快速迭代。

在如今竞争白热化的芯片市场中,上市时间(Time-to-market)是很重要的竞争力。任何物理验证过程的延误都可能影响芯片的上市时间,这不仅会带来巨大的经济损失,还可能对企业的整体策略造成打击。

因此,物理验证工具必须不断创新和改进,进一步智能化并提高效率。

理想中的DRC工具应该能按制造商的基本规则自动运作,迅速评估设计质量。当设计基本合规时,它可以顺畅地完成剩下的检查任务。此外,如果DRC能为设计师提供一个错误“热图”则是极大的加分项,它帮助设计师直观地在数百万的小错误中标识出目标问题区域,使设计师能迅速定位并解决问题。

LVS工具应当能够准确地识别出设计中哪些部分是关键,提供一个自动化的方法来迅速定位全芯片LVS运行中出现问题的根源。

这些压力无疑给到了EDA供应商,但一旦解决,这也将成为他们的核心竞争力。

颠覆传统,新思科技塑造下一代物理验证

新思科技的IC Validator是一个专为现代设计的物理验证工具,它采用业界先进的分布式处理算法,可扩展到超过 4,000个CPU核,实现了目前业内领先的超大芯片的物理验证签收。数十亿个晶体管的设计,一天内就可完成设计规则检查 (DRC)、布局与原理图对照验证 (LVS) 以及金属填充的一次迭代。此外,IC Validator在仅有少量资源的情况下也可以立即启动,在资源增加时使用更多的资源。

(图源:新思科技)

近几年来,新思科技不断地对IC Validator进行升级,以满足日益变化的芯片验证需求。

1

Explorer DRC技术

早在2018年,新思科技就引入了Explorer DRC技术,为开发团队提供了在同一天进行DRC检查的功能,并在SoC整合过程中在几小时内识别关键设计缺陷。它的性能相比传统DRC流程大大提高,使运行时间加快五倍,使用的核心数量减少五倍。这意味着即使设计是“不干净”的,16或32核的CPU也可以在几小时之内完成一个典型5nm芯片的DRC验证,帮助流片工程师快速找到主要的设计问题并立即开始修复。

值得关注的是,新思科技正在尝试通过云计算进行IC验证,并以DRC作为其测试场景。这种创新的动力来源包括一下几方面:

(1)面对成本压力、不断缩小的市场窗口以及更好的性能和更多功能的市场需求,本地存储已成为许多企业无法承受的负担。在云端进行IC设计,并实现计算资源的弹性扩展的时机已经到来。

(2)单纯地为DRC工具增加计算能力并不能缩短运行时间,因为在IC验证过程中,某些计算资源可能会时常处于闲置状态,这导致了资源的浪费,增加了企业成本。

云计算为现代IC验证提供了有效的途径。通过云验证,企业可以轻松地从本地数百核扩展到云端的数千核。这种方式不仅提供了弹性、灵活性和扩展性,还确保了资源的合理利用。同时,DRC的任务也能分配到多个核心上并行执行,从而实现资源的最优化,节约时间和成本。

新思科技的IC Validator的动态弹性CPU管理与流行的作业队列系统(如LSF和SGE)能够无缝集成,并可在本地和云端等不同类型的计算网络上使用。例如,在新思科技与台积电和微软的合作中,在云端进行的IC设计将台积电 N3E工艺的验证时间从约50小时缩短到不到20小时,效率提高了65%,同时成本和CPU使用时间也比本地减少了25%。如下图所示。除了所有时间和成本优势之外,新思科技的虚拟网络(VNET)可以很好的确保云端部署EDA的安全性。

图片来源:台积电

2

Explorer LVS技术

2019年新思科技又推出了Explorer LVS技术,这也是行业首款是专为SoC时代设计的现代LVS解决方案。Explorer LVS可以在签核准备验收时的任何时候使用,以检查顶层设计的完整性。而且使用Explorer LVS可以快速、高效地检测到关键问题,使验收工程师无需承受传统LVS工具的低效率。当首次完成全芯片整合后立即运行时,其性能和效益可以达到最大。

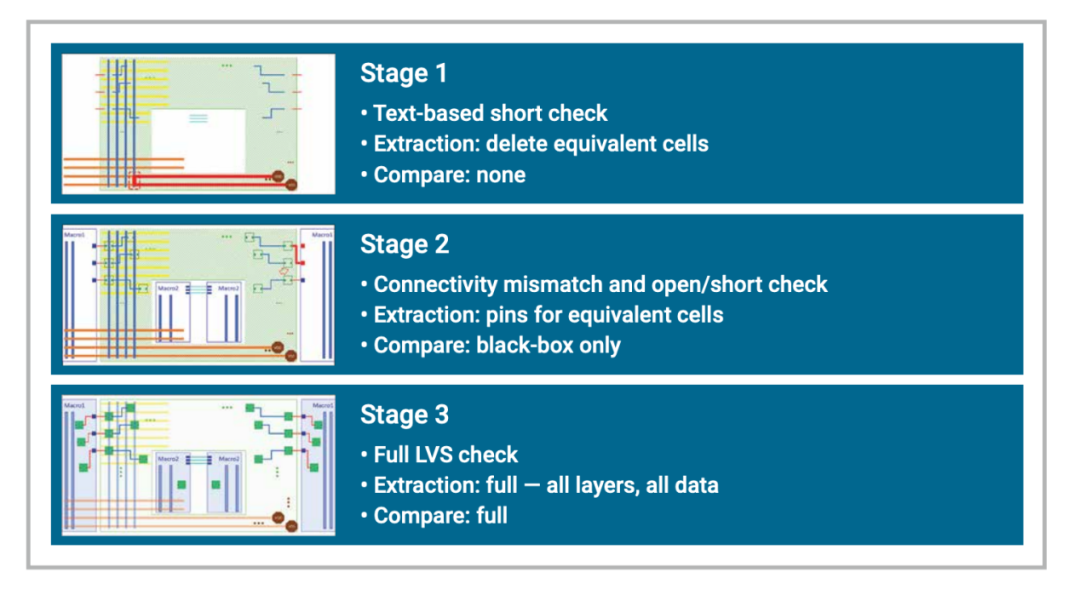

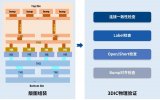

尽管Explorer LVS的主要设计目标是完整芯片的布局,但它适用于任何大小和复杂度的设计。设计越大、越复杂,其相对于前一代工具的性能就越好。Explorer LVS包括三个不同的阶段,如下图所示。

Explorer LVS检查的3个阶段

(图源:新思科技)

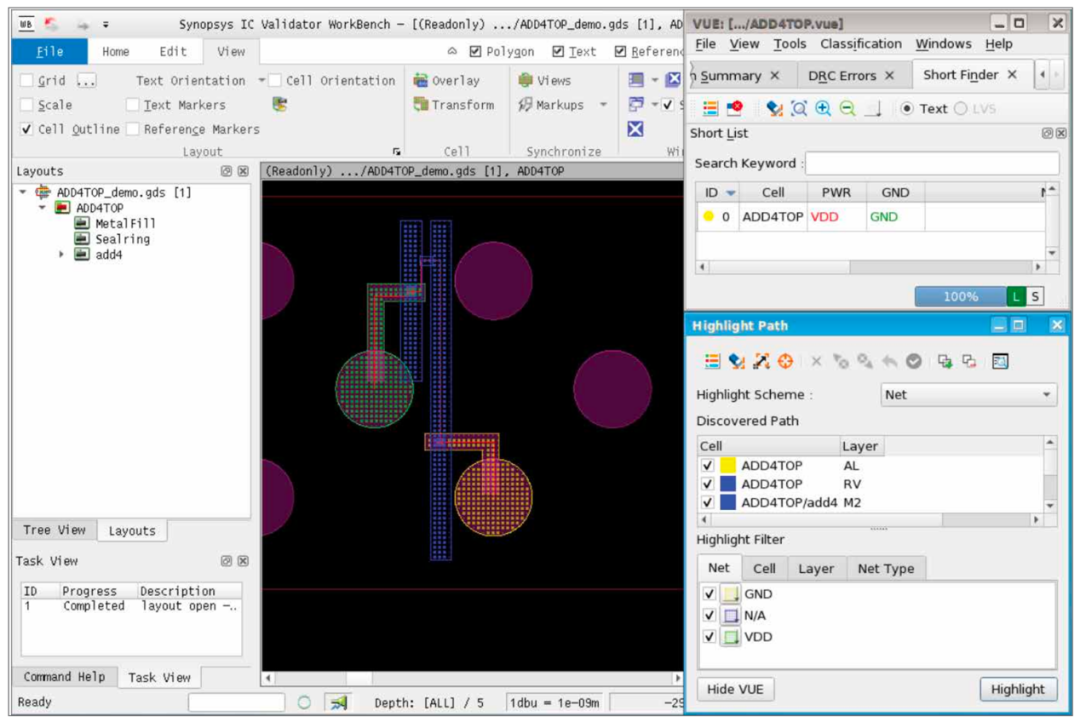

一旦Explorer LVS对设计执行,就会生成一个摘要文件,工程师可以使用摘要文件来检查全芯片设计的整体质量,以签署准备度来衡量。每个单独的错误都可以通过文本格式的日志文件或交互工具进行检查和调试。对于设计中的短路的调试,Explorer LVS的结果可以立即加载到IC Validator ShortFinder中,以便进行快速和简便的基于GUI的交互调试,如下图所示。

在LVS中调试设计缺陷

(图源:新思科技)

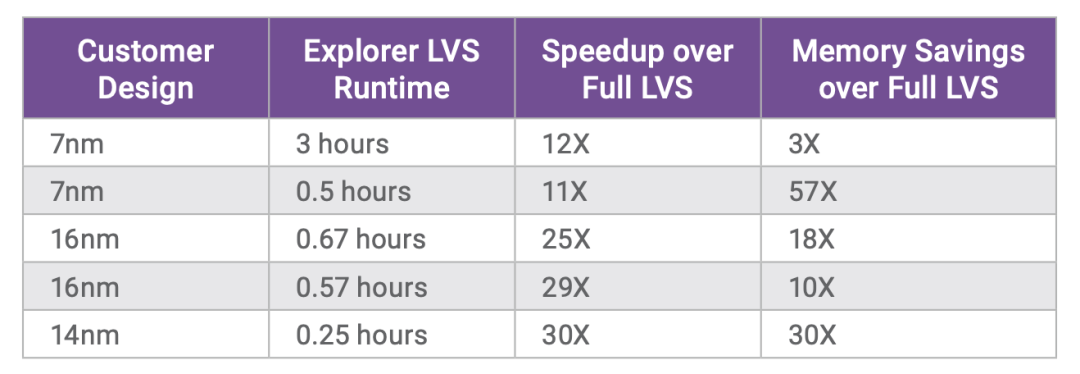

Explorer LVS可以与全面的LVS完美配合。在典型的流程中,当我们在初步的布局和路径规划后进行区块或模块设计时,可能会运行全面的LVS,以便在项目早期发现问题。当这些部分组装成一个完整的芯片时,Explorer LVS提供快速的运行时间和直观的调试来尽量清理设计,然后使用全面的LVS进行最终验收。如果在验收前发生了工程变更订单(ECOs)或最后一刻的宏/模块更新,Explorer LVS能确保设计的完整性不受损害。如下图所示,在真实的客户设计中,与全面的LVS相比,Explorer LVS的运行速度最快可提升30倍,且使用的内存减少了30倍。

Explorer LVS的实际性能结果

(图源:新思科技)

结论与展望

随着半导体技术的迅猛发展,面对日益增长的挑战,我们亟需更为先进的设计验证工具。新思科技在物理验证技术上的持续创新,特别是通过Explorer DRC和Explorer LVS,再加上其在EDA云技术上的探索与突破,可以使芯片工程师更为高效和精确地完成设计验证。这不仅确保了产品的卓越质量和稳健可靠性,而且为当下的芯片物理验证流程注入了创新活力。

展望未来,随着云计算的普及和技术的成熟,我们期望EDA工具能够更加完美地集成到云环境中,实现真正的全球协作和无缝的设计验证流程。同时这就需要像新思科技这样的EDA厂商继续在物理验证技术上进行更深入的研究与创新。这将为整个半导体产业带来更大的效率提升和成本节约。

审核编辑:刘清

-

芯片设计

+关注

关注

15文章

1172浏览量

56776 -

人工智能

+关注

关注

1820文章

50317浏览量

266894 -

DRC

+关注

关注

2文章

157浏览量

38327 -

DFM

+关注

关注

8文章

491浏览量

31681 -

自动驾驶

+关注

关注

794文章

14986浏览量

181466

原文标题:芯片集成度飙升,物理验证成为关键

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2026年AI芯片破局指南:晶圆厂不再是瓶颈,先进封装才是核心胜负手

集成电路制造工艺中的刻蚀技术介绍

台积电计划建设4座先进封装厂,应对AI芯片需求

功函数在芯片制造中的核心作用

华宇电子分享在先进封装技术领域的最新成果

嵌入式需要掌握哪些核心技能?

硅通孔电镀材料在先进封装中的应用

智能座舱骨架承重物理测试:极限载荷下结构变形量与耐久性验证 智能座舱骨架承重物理测试:极限载荷下结

新思科技携手AMD革新芯片设计流程

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

力旺NeoFuse于台积电N3P制程完成可靠度验证

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

ADI 数据采集解决方案在先进光刻芯片制造领域大放异彩l

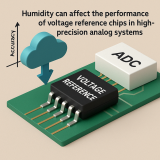

湿度对基准源芯片稳定性的影响探究

物理验证在先进芯片设计中的核心地位

物理验证在先进芯片设计中的核心地位

评论