四面无引线扁平封装(Quad Flat No-lead Package, QFN)属于表面贴装型封装, 是一种无引脚且呈方形的封装, 其封装四侧有对外电气连接的导电焊盘(引脚),引脚节距一般为0.65mm、0.5mm、0.4mm、0. 35mm。

由于封装体外部无引脚, 其贴装面积和高度比QFP小。QFN封装底部中央有一个大面积外露的导热焊盘。QFN封装无鸥翼状引线, 内部引脚与焊盘之间的导电路径短, 自感系数及体内线路电阻低, 能提供优越的电性能。外露的导热焊盘上有散热通道, 使QFN封装具有出色的散热性。

上图分别是WB-QFN (Wire Bonding-QFN)和FC-QFN(Filp Chip-QFN)基本结构示意图。这些结构加上MCP技术和SiP等封装技术,为QFN的灵活多样性提供了良好的I/O设计解决方案,也进一步提高了封装密度。

QFN的工艺流程与传统封装的接近, 主要差异点如下所述。

(1)Q FN产品框架在塑封前一般采取贴膜工艺,进行球焊时的球焊参数模式与传统的有差异, 若控制不当, 会造成焊线第2点的断裂;另外,矩阵框架的塑封工艺必须采取多段注射方式来避免气泡和冲线的发生。

(2)QFN产品的分离是采取切割工艺来实现的,切割过程中要采取合适的工艺(如低温水)来避免熔锡,采用树脂软刀来减少切割应力, 采用合适的切割速度来避免分层等。

(3)QFN产品通过选择不同收缩率的塑封料来控制翘曲, 不同厚度和大小的芯片需要选择不同收缩率的塑封料。

(4)QFN产品的框架均为刻蚀框架, 框架设计包含应力、抗分层、预防毛刺等考虑因素, 框架设计的好坏决定着产品品质的水平。

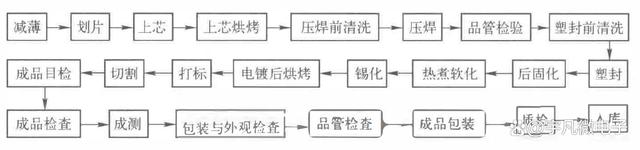

传统上芯(装片)的QFN产品的生产工艺流程如下:

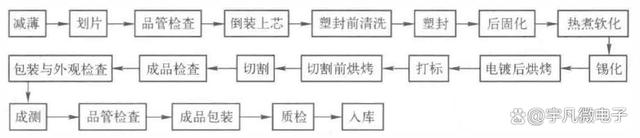

倒装上芯的QFN产品的生产工艺流程如下

在常见的QFN封装下,宇凡微还提供定制封装服务,如QFN20等,能定制十多种特殊的封装。

-

封装

+关注

关注

128文章

9330浏览量

149047 -

qfn

+关注

关注

3文章

216浏览量

58460 -

封装工艺

+关注

关注

3文章

69浏览量

8307

发布评论请先 登录

LED晶膜屏的FPC基材选型与COB封装工艺研究(源头厂家技术白皮书)

Freescale半导体QFN封装迁移及MC9S08SH8芯片详解

Freescale半导体QFN封装迁移及MC9S08GB60A芯片解析

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

短距离光模块 COB 封装与同轴工艺的区别有哪些

SK海力士HBS存储技术,基于垂直导线扇出VFO封装工艺

采用 QFN 封装的 0.1 至 3.8 GHz SPDT 高功率天线调谐开关 skyworksinc

采用 QFN 封装的 0.6 至 6.0 GHz 4xSPST 分流 MIPI 天线调谐开关 skyworksinc

半导体封装工艺流程的主要步骤

QFN封装工艺讲解

QFN封装工艺讲解

评论