转向异构方法需要在芯片设计、IC 封测方面建立基础设施。

异构IC封装已经投入生产,并且越来越多的客户正在 Amkor 以及其他外包半导体组装和测试 (OSAT) 供应商和代工供应商处开发和验证其产品。

这种新的多管芯实施例的基本原理已经得到充分记录和讨论。归根结底,更多的系统内容正在转移到软件包本身中,从而在性能、成本和上市时间 (TTM) 方面带来好处。由于较小的小芯片的产量更高,因此总硅成本可以降低。异质封装还提供了使用混合硅工艺节点来进一步优化硅成本的机会。虽然异构 IC 封装更昂贵,但积极的权衡/好处是较低的总硅成本和积极的 TTM 优势。转向异构方法需要在设计、IC 和封装制造以及测试方面建立基础设施。

随着每个 OSAT 和代工厂提供自己的技术,支持小芯片和异构结构的 IC 封装选项也不断传播。结果,术语变得相当混乱。值得庆幸的是,这些封装结构比目前行业中存在的术语简单得多。多芯片产品必须集成到一个功能单元中,这可以在传统的 IC 封装基板上完成,也可以通过使用更高密度的集成方法(即晶圆级多芯片模块、超细线集成或两者兼而有之)来完成。然后将该模块附着到 IC 封装基板上。

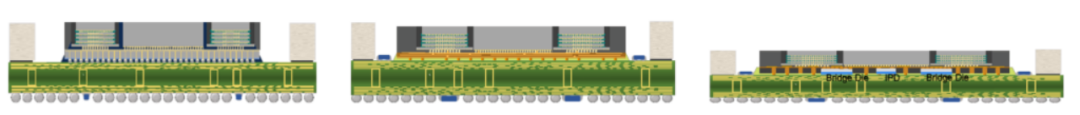

第一种选择以历史悠久的多芯片模块 (MCM) 为代表,该模块已投入生产数十年,现代设计趋向于在基板上采用更高的硅和无源密度。高密度集成方法的第二个选择是创建集成芯片或小芯片的模块,这需要芯片间接口的超细线路布线。如今,这些是 (A) 基于硅中介层的模块 - 2.5D 硅通孔 (TSV)、(B) 基于高密度扇出 (HDFO) 多层再分布层 (RDL) 方法的模块,或 (C) 具有桥接器的模块,如图 1 所示。

图 1:a) 2.5D TSV(硅中介层,b)HDFO (S-SWIFT) RDL 中介层,c) 桥 (S-Connect)(RDL+ 桥)。

异构 IC 封装设计

基于 HDFO 内插器的模块已通过内部认证,是客户产品,并且正在认证中。由于向小芯片的过渡刚刚开始,市场上使用 HDFO 内插器的不同设备的数量仍然有限。然而,市场正在发生变化,大多数已经在生产高端单片或 MCM 设备的先进封装客户要么正在积极验证 HDFO 中介层,要么正在询问,以期开始开发。

在包含HDFO模块的产品的初始规划阶段,重要的是要了解每个设备都可能被视为“定制”。虽然认证范围可能包括正在考虑的整体模块和封装尺寸,但每个器件都有独特的挑战。因此,几乎每个新设备都有测试车辆的迭代。随着越来越多的测试车辆(TV)成功完成,并且更多可能的设计空间品种通过认证,有可能直接进入产品认证阶段,但目前强烈建议使用 TV。

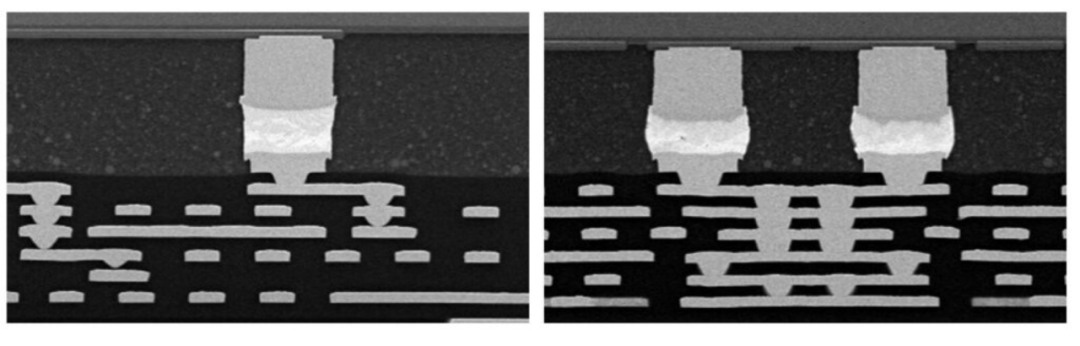

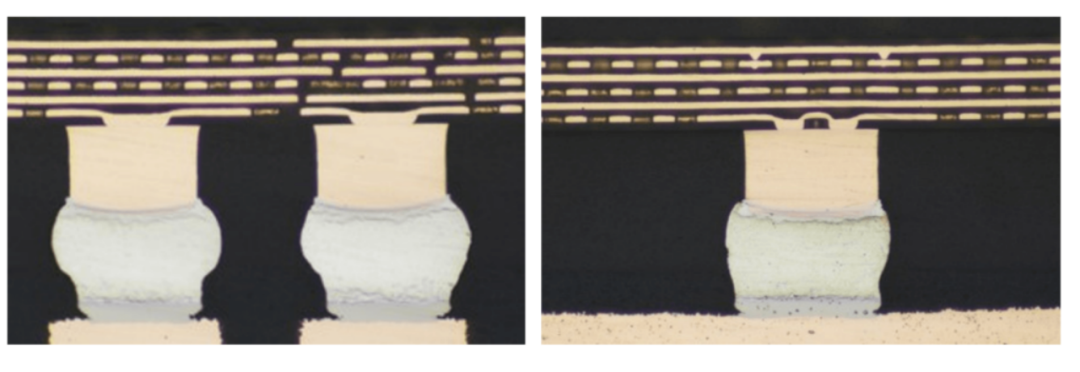

第一个通常使用TV。是菊花链芯片或至少是凸块虚拟芯片,以允许发现模块中多芯片布局的任何独特特征。评估中介层载体和包覆成型晶圆级翘曲就是一个很好的例子。机械仿真可用于估计翘曲,但尽管可以模拟全晶圆级翘曲,但它对RDL中的金属密度等也非常敏感。总是可以在模拟中确定趋势,但最终评估需要通过实际TV来确定。由于TV的内部制造速度相对较快,因此可以快速根据真实数据校准模拟,以便在更改模型或者设备中的不同元素时可以了解趋势。通过构建机械或菊花链TV,可以快速收集数据以了解任何工程工作需要集中在哪里。迄今为止,这已在许多TV结构中重复出现,并且是 Amkor 众所周知的流程开发路径。图 2a 和 b 显示了典型的TV方法。

图 2a:连接到 HDFO 的测试车辆芯片。

图 2b:连接到封装基板的测试车辆 HDFO 模块。

第二台TV可以是另一个菊花链设备,或者在芯片中具有一些最小的功能或芯片封装交互 (CPI) 测试结构。尽管芯片可能不具备完整的功能,但设计本身要么与功能设计类似,要么实际上就是功能设计。中介层 RDL 的设计通常在第一台TV之前开始,因为芯片之间的小芯片接口仍然是客户特定的。随着设计规则的不断改进,寻找最佳布线策略需要客户和制造商之间的密切合作。根据产品的生产目标时间,可能会提供仍在开发中的更高级的设计规则,这将实现初始设计规则不允许的布线。每个客户对设计流程都有自己的偏好。Amkor 尝试满足所有偏好,从仅接收中介层的成品图形数据流 (GDS) 到管理整个设计流程。

HDFO 中介层设计流程通常从 Amkor 设计团队在 Cadence(SIP/MCM 文件)或西门子 Expedition 中提供的入门数据库开始。起始数据库不是必需的,但会自动启动标准设计规则和必要的设置,以与 Calibre 设计规则检查 (DRC) 实现进行交互,从而节省时间。无论使用哪种电子设计自动化 (EDA) 工具,Amkor 还可以帮助设置这些参数。Calibre DRC 规则平台可以由 Amkor 或客户运行,因为它直接在从 EDA 工具导出的 GDS 上运行。

对于更大、更复杂的中介层,设计过程可能需要 4 到 12 周。自 Amkor 推出 SWIFT HDFO 技术以来,EDA 工具多年来得到了显著改进。动态填充步骤的处理时间可能比大多数设计人员习惯的时间长得多,因此从一开始就预测生产计划中的增加时间非常重要。这是由于设计中存在大量的引脚、迹线和形状。脱气通常是设计发布之前执行的最后操作,具体取决于所需的操作。Amkor 已开发出可以减少脱气所需时间的方法,但对于大型设计,这可能需要数天的时间。

设计完成后,将其发布到 HDFO 生产线以启动 RDL 构建过程。在制造第二台TV的 HDFO 内插器时,通常会在第一台TV上收集数据。这允许在第二台TV上规划任何所需的实验设计 (DOE)。并非每个设备都需要 DOE,但这是至关重要的一步,以便在开始组装第二台TV之前可以标记并修复或改进。

第二个测试车辆通常用于封装鉴定。HDFO 模块已被证明非常坚固,通过了湿度敏感性测试 1 级 (MSL1) 和温度循环、条件 C (TCC)(-65°C 至 +150°C)。一旦附着到基材上,更常见的是在 MSL 4 和温度循环、条件 G(-40°C 至 +125°C)下进行评估,但使用压力更大的 TCB(-55°C 至 125°C)进行 > 3000 个温度循环也取得了成功。总体而言,就封装可靠性而言,HDFO 已被证明是一种非常坚固的结构。针对大型封装的标准高温存储 (HTS) 测试(150°C,1000 小时)和标准无偏高加速应力测试 (UHAST)(110°C,85% 相对湿度 (RH),264 小时)在封装鉴定方面也未发现任何问题。

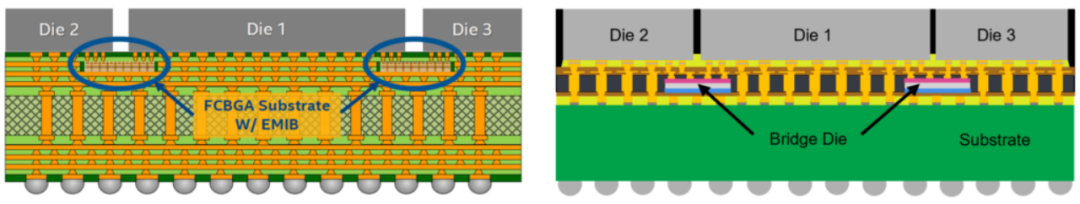

多年来,业界一直致力于研究利用桥接技术的方法。英特尔的嵌入式多芯片互连桥 (EMIB) 利用放置在有机基板内的桥来实现高密度布线,而无需使用硅中介层。Amkor 在这一领域的方法是将桥(硅或其他桥)嵌入到 HDFO 设计中,这为 HDFO 工具箱带来了超高密度设计规则。Amkor 将此技术称为 S-Connect。图 3 显示了这两种设计技术的比较。

图 3:(L) Intel EMIB(图片由 Intel 提供)(R) Amkor S-Connect

与客户和行业合作伙伴合作时,需要进行权衡分析,在硅中介层、有机 RDL HDFO 和 S-Connect 等桥接解决方案之间做出决定。使用桥的决定必须解决桥芯片(带或不带 TSV)和硅集成无源器件(如果有保证)的采购问题。最终客户还考虑每个解决方案的整体生产准备情况和成熟度。硅中介层最为成熟,因为它们已进行大批量制造 (HVM) 多年,其次是已完成许多成功认证的有机 RDL 和 S-Connect。随着系统变得更加复杂,集成的需求可能会迫使解决方案转向桥接解决方案,例如 S-Connect。

桥梁技术的三个主要驱动因素。桥接技术通过包含用于小芯片到小芯片或芯片到芯片布线的基于硅的高密度布线桥,可以减少 RDL 数量,从而有可能降低系统成本。桥接技术还利用晶圆厂光刻技术,使布线密度低于 1 µm,从而有助于在硅顶部芯片上实现更精细的凸块间距。最后,桥接技术的使用允许在同一 3D 位置(见图 4)创造性地使用嵌入式硅集成无源器件 (IPD),直接放置在顶部芯片下方,以实现最佳功率传输。

HDFO 设计和制造可采用先芯片或后芯片配置。对于更简单和更小的设计,芯片优先可能是合适的并且成本较低的方法。Amkor 的 S-Connect 设计主要路径采用后芯片方法,以利用后芯片 HDFO 技术的专业知识,并尽量减少对客户芯片的良率影响。

后模 S-Connect 结构由带有预制高铜柱的基础 RDL 组成。桥芯片和其他非桥芯片(包括 IPD)面朝上放置,并带有较小的铜柱。晶圆被模制并平坦化以露出所有铜柱。芯片放置能力是一项关键的工艺要求,随着任何给定产品中放置的面朝上桥芯片数量的增加,该能力变得更加复杂。然后使用有机 RLD 工艺(如 HDFO)执行额外的 RDL 处理,并提供用于芯片连接的芯片连接垫。然后通过第二次模具和模具研磨工艺完成晶圆上芯片组装。然后将晶圆从载体上取下并翻转进行背面处理,其中电镀受控塌陷芯片连接 (C4) 铜柱。至此,模块形成完成,并适合用于其他集成模块的通用过程。

在考虑 S-Connect 而非其他形式的异构集成时,桥芯片采购是另一个关键方面。客户可能要求桥接器还具有 TSV,以便为 I/O PHY 提供电源和接地。这些 TSV 承载桥芯片的采购和加工将使 S-Connect 模块的晶圆级制造更加复杂。Amkor 拥有丰富的 TSV 工艺经验,包括大量可供选择的化学机械平坦化 (CMP)/背面钝化配方,可最大程度地减少 TSV 轴承桥制备过程中所需的开发工作。

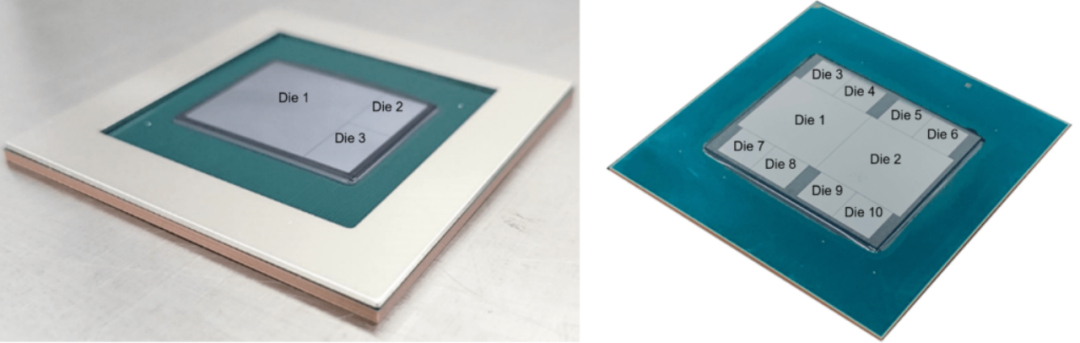

目前,有两个内部TV用于 S-Connect 开发。三个芯片模块的开发和内部鉴定已经完成,其中包括一个较大的芯片和两个较小的芯片(如高带宽内存 (HBM))。该模块具有两个桥芯片和多个测试芯片,用于模拟非 TSV 承载 IPD 芯片的放置。在更大规模上,模块TV的开发正在使用 10 个顶部芯片和 10 个桥芯片。该演示针对的是非常大的模块,这些模块从硅桥芯片的使用中获益最多。该TV预计将于 2023 年获得可靠性结果。图 4 显示了两台 S-Connect 测试车辆。

图 4:S-Connect 测试车辆的类型。

Amkor 一直在为异构集成的下一次发展做准备,我们相信,随着需要更多集成,它将提供独特的功能来增强 HDFO 和硅中介层解决方案。对于更大的中介层(>2500 mm2),桥接解决方案将有助于保持高良率,因为最高密度要求(以及最高的潜在良率损失)发生在桥上,而桥接已经具有极高的良率。

测试方法

自这些设计开始以来,Amkor 就一直为异构集成产品提供测试服务。设计和评估TV的系统方法使测试工程师能够在产品投入使用之前针对设计的关键方面进行测试。

所有异构小芯片封装都面临一些共同的测试挑战。小芯片互连完整性是一项重要的因素。向封装内每个小芯片传输信号和电源需要在制造过程中进行仔细的布局、设计和测试。封装材料类型影响小芯片和封装级暴露的引脚之间的互连性能。这包括静态连接质量、连续性、泄漏和瞬态交流时序、阻抗匹配和信号串扰。在精心设计的整体产品架构中,对产品所有功能方面的可测试性设计 (DFT) 访问是一个重要的考虑因素。

由于小芯片温度不均匀导致的热梯度很常见。受控、管理和可重复的生产测试环境可确保为未来的产品设计迭代提供准确的反馈和一致的产量。

结论

使用 MCM 和古老的 2.5D TSV 硅中介层方法的异构集成已投入生产多年。向基于异构小芯片的集成的过渡才刚刚开始。

为了集成小芯片,典型的设计必须在芯片之间具有高带宽接口,这通常需要精细的凸块间距(≤55 µm)、高信号速率和短总线长度。HDFO 和 S-Connect 设计为这些集成提供了经济高效的途径。典型的设计小于 2500 mm2,但目前的趋势是朝着更大尺寸和更高芯片数量发展。

对于较大的模块,使用桥是有意义的。由于 RDL 产量,使用极细线 RDL 的大型模块(>2500 mm2)成本会更高。使用极高产量的桥在芯片之间提供最精细的布线,并结合其他地方较低密度的 RDL,由于预期总产量较高,因此将是更好的经济权衡。桥接封装解决方案正在开发中,目标是在 2023 年和 2024 年获得客户资格。HDFO 小芯片集成已通过内部资格认证,HDFO 已准备好接受客户参与和产品资格认证。针对异构集成产品的一流测试服务完善了整个制造过程。

-

芯片

+关注

关注

463文章

54431浏览量

469381 -

模块

+关注

关注

7文章

2849浏览量

53439 -

封装

+关注

关注

128文章

9330浏览量

149047

原文标题:异构IC封装:构建基础设施

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

为何CPU是AI基础设施的核心

西门子Innovator3D IC异构集成平台解决方案

华为成功举行数据中心基础设施峰会

1.93 - 1.995 GHz 基础设施小型蜂窝功率放大器模块 skyworksinc

CATV 基础设施放大器 1.2 GHz CCAP/Edge QAM/CMTS 驱动器 skyworksinc

无人机巡检系统为基础设施装上智慧天眼

Imagination加入龙蜥智算基础设施联盟,携手共建AI开源新生态

异构IC封装:构建基础设施

异构IC封装:构建基础设施

评论