AMD Zen4还在积极布局中,AMD Zen5也不远了。

快科技7月7日消息,AMD在最新提交的Linux补丁中,已经加入了对Zen5的初步支持,加入了新的PCI设备ID,对应Family 26(1Ah) Model 00-31(00h-1Fh)、67-79(40h-4Fh)。

具体支持包括k10tmp热敏传感器、EDAC AMD64驱动内存校验纠错等等。

补丁文件显示,Zen5霄龙将具备12个DDR5内存通道,这和此前曝料一致,和现有Zen4 Genoa、Bergamo系列是一样的。

不知道下一代霄龙是否会更换接口,但考虑到要支持MR-DIMM、MCR-DIMM等内存规格,不排除会有变。

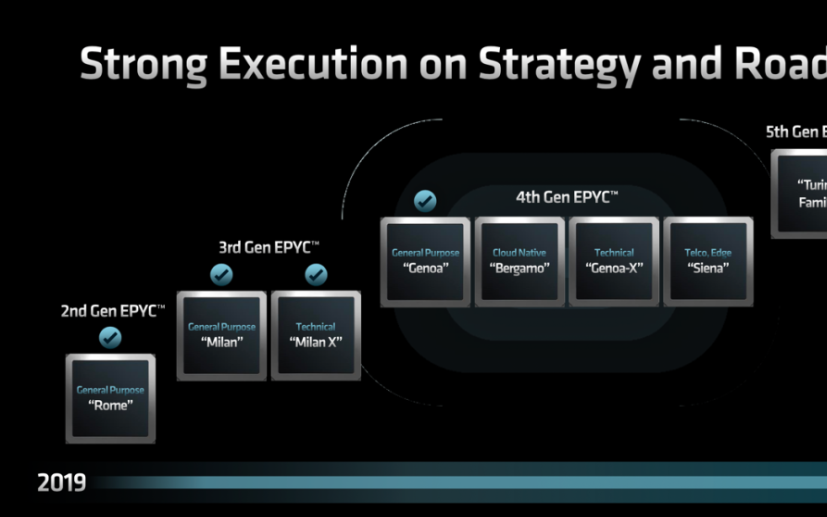

按照AMD给出的官方路线图,消费级的锐龙8000系列、数据中心级的下一代霄龙,都将在2024年推出。

其中,霄龙家族代号Turin,升级为4nm、3nm工艺,包含Zen5、Zen5 3D V-Cache、Zen5c等多个不同版本,和现有产品线一一对应。

曝料称,Zen5霄龙标准版将有16个CCD、128核心、512MB三级缓存,3D缓存版集成最多1GB,加上原生512MB,三级缓存就多达1.5GB,Zen5c版本则是12个CCD、192核心、384MB三级缓存。

锐龙8000还是最多16核心32线程,二三级缓存不变,一级缓存从64KB增加到80KB,IPC提升最多19%,加速频率预计可达5.8-6.0GHz,热设计功耗最高还是170W。

另外,AMD日前低调推出了锐龙5 5600X3D,这是第二款采用Zen3架构的3D缓存型号,而且更加主流,非常适合老平台升级,只可惜目前仅限美国Micro Center电商独家发售。

它的的基础规格和锐龙5 5600X一致,都是6核心12线程、3MB二级缓存、32MB三级缓存,叠加64MB 3D缓存后总容量99MB,只比锐龙7 5800X3D少了1MB二级缓存。

频率设定在3.3-4.4GHz,分别降低了400MHz、200MHz,但是热设计功耗反而从65W增加到了105W。

价格方面仅为229美元。

Tom's Hardware已经拿到了一颗锐龙5 5600X3D,并进行了详细评测,这里只看结论。

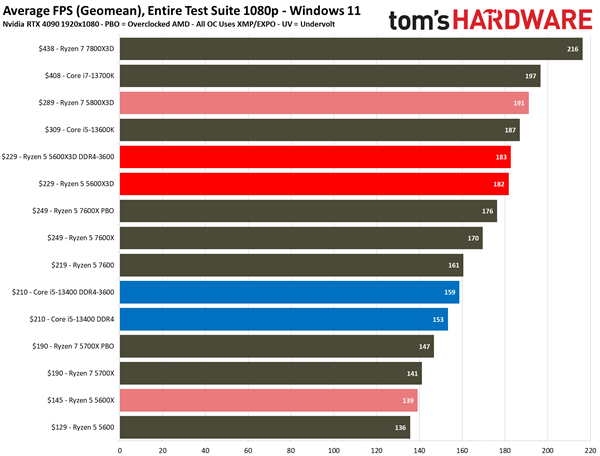

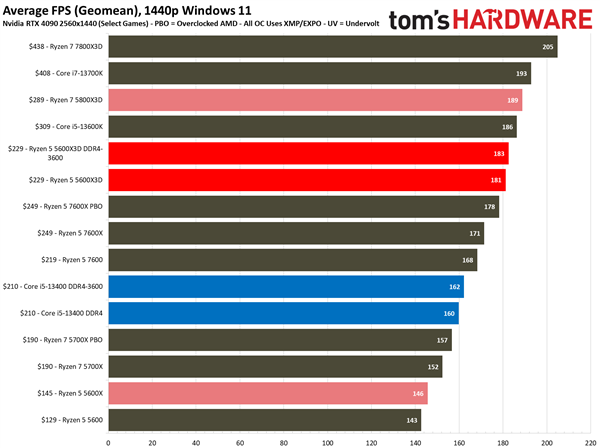

总体而言,锐龙5 5600X3D相比于锐龙7 5800X3D只损失了大约5%的游戏性能,但价格却便宜了足足20%,性价比极高,同时也超越了Zen3、Zen4架构的所有标准版锐龙。

对标竞品的话,它要领先i5-13400 20%左右,优势极为明显,同时也已经非常逼近i5-13600K。

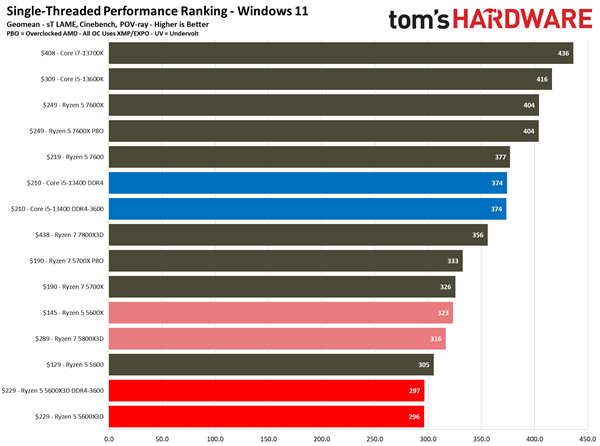

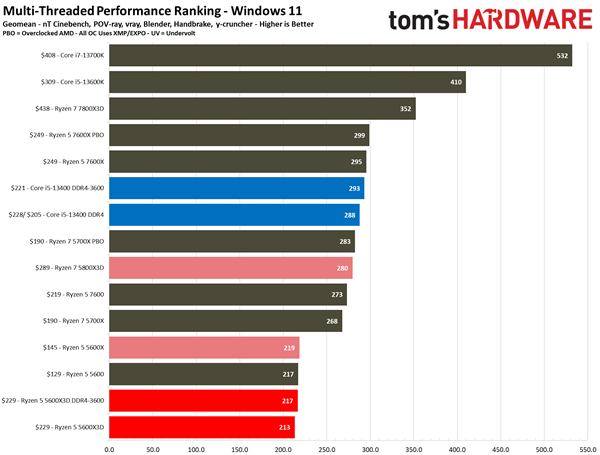

当然,3D缓存导致锐龙5 5600X3D的频率降低不少,常规性能就不行了,i5-13400的单核、多核性能要比它分别快26%、35%之多。

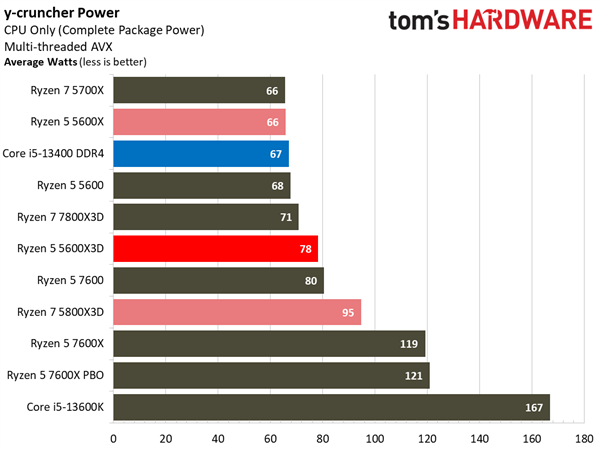

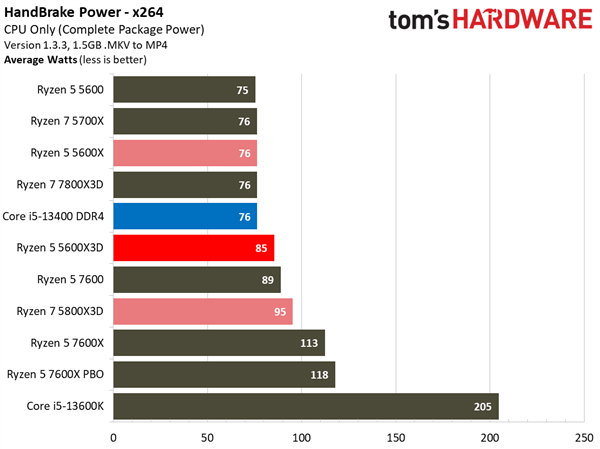

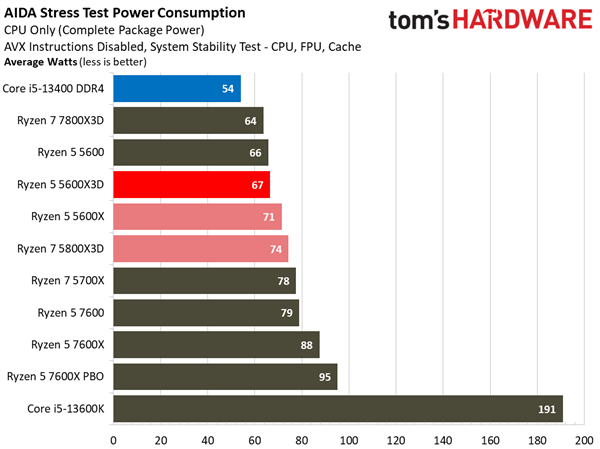

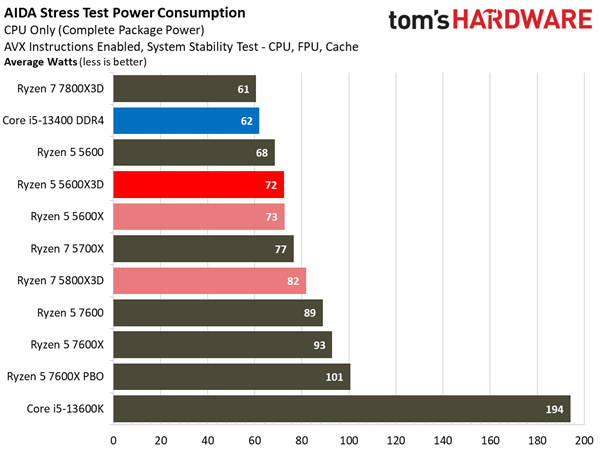

功耗方面,锐龙5 5600X3D虽然标称TDP 105W,但实际功耗最多也就87W,能效还是不错的。

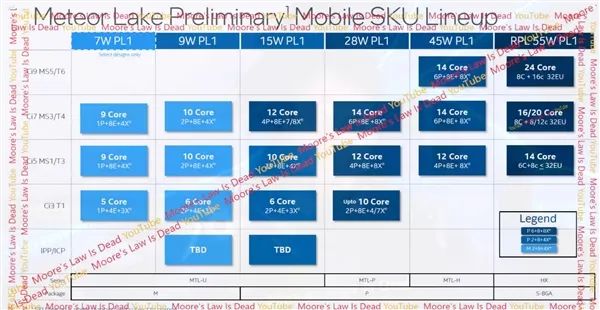

再说Intel,下一代处理器将分为三大序列,其中全新的Meteor Lake命名为一代酷睿Ultra,覆盖中低端笔记本;升级版的Raptor Lake-HX/S系列命名为14代酷睿,覆盖高端游戏本、桌面;升级版的Raptor Lake-U系列命名为一代酷睿,覆盖低功耗轻薄本。

曝料大神MLID现在公布了酷睿Ultra家族的完整产品线,包括7-45W五种不同等级功耗,还有14代酷睿HX,功耗级别还是55W。

具体来首:7W U系列超低功耗有5-9个核心,最少1P+4E、最多1P+8E,13代没有这个系列;

9W U系列超低功耗有6-10个核心,最少2P+4E、最多2P+8E,13代也没有这个系列;

15W U系列低功耗有6-12个核心,最少2P+4E、最多4P+8E,对比13代去掉了1P+4E 5核心;

28W P系列低功耗有10-14个核心,最少2P+8E、最多4P+8E,对比13代增加了2P+8E 10核心;

45W H系列高性能有12-14个核心,最少4P+8E、最多4P+8E,对比13代砍掉了4P+4E 8核心、6P+4E 10核心;

55W HX系列还是13代扛着,14-24个核心,最少6P+8E、最多8P+16E,不再提供意义不大的6P+4E 10核心。

核显方面,酷睿Ultra将升级为全新的Xe LPG架构,也就是Arc A系列独立显卡所用Xe HPG架构的低功耗版本,完整支持DX12 Ultimate,针对功耗、面积做了优化,核心数量也比现在增加1/3。

酷睿Ultra的核显依然分为不同档次,最多8个Xe核心,或者说128个EU单元,同时还有7核心、4核心、3核心的不同版本。

其中,7/15W 3-4个核心,15W 3-8个核心,28W 4-8个核心,45W 8个核心。

审核编辑:刘清

-

传感器

+关注

关注

2578文章

55567浏览量

794209 -

Linux系统

+关注

关注

4文章

617浏览量

30174 -

MCR

+关注

关注

0文章

19浏览量

11437 -

CCD技术

+关注

关注

0文章

3浏览量

6228 -

DDR5

+关注

关注

1文章

485浏览量

25819

原文标题:AMD Zen5开始行动!冲上192核心、锐龙8000明年见

文章出处:【微信号:hdworld16,微信公众号:硬件世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AMD Versal CPM5 QDMA Gen4x8 ST Only Performance Design CED示例

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(下)

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

AMD 推出锐龙 AI 嵌入式处理器产品组合,为汽车、工业和物理 AI 领域提供 AI 驱动的沉浸式体验

强强联手 | AMD嵌入式高层一行访问ALINX,深化2026战略合作前沿技术布局

如何在AMD Vitis Unified 2024.2中连接到QEMU

江波龙企业级DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性认证

AMD Power Design Manager 2025.1现已推出

使用AMD Vitis Unified IDE创建HLS组件

基于AMD Versal器件实现PCIe5 DMA功能

AMD Spartan UltraScale+ FPGA 开始量产出货

如何使用AMD Vitis HLS创建HLS IP

AMD Zen4还在积极布局中,AMD Zen5开始行动!

AMD Zen4还在积极布局中,AMD Zen5开始行动!

评论