今天,高速发展的电子产品已经成为了人们生产生活必不可少的工具。除了笔记本、智能手机,云计算、物联网、车载安防等各个场景都高度依赖着强大的运行速度和内存。而当今,最有发展潜力的存储技术莫过于3D NAND闪存,所有主要闪存制造商都在积极采用各种方法来降低闪存的每位成本,同时创造出适用于各种应用的产品。闪存制造商还在积极展开研究,期望能够扩展3D NAND闪存的垂直层数。虽然15nm似乎是NAND闪存目前能够达到的最小节点,但开发者依然在不懈地追求缩小闪存的光刻节点。此外, 闪存制造商也在积极探索将MLC和TLC技术与3D NAND闪存技术相结合, 许多制造商已经看到了胜利的曙光。

然而,NAND设计IP仍然面临更多挑战。如何使验证变得更加高效?新思科技的NAND闪存验证IP提供了一套全面的协议、方法、验证和效率功能, 使开发者能够加速实现验证收敛。

NAND闪存简介

-

工业用户需要在断电时也能保护数据的存储解决方案,因此NVM对他们极具吸引力

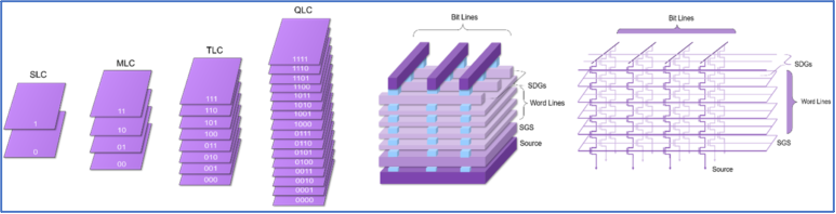

NAND闪存类型

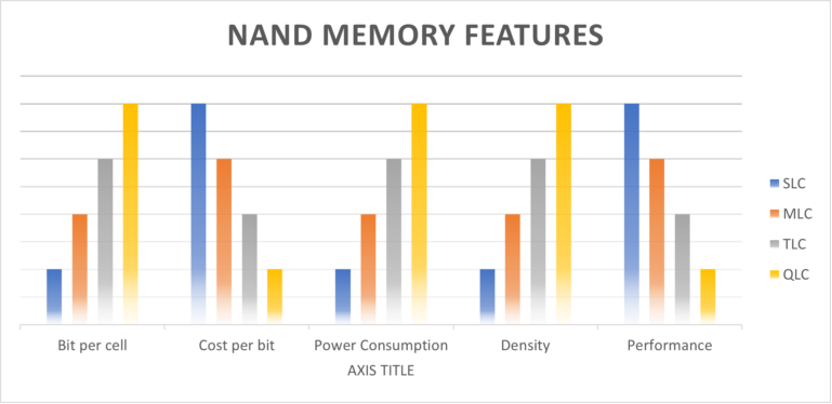

随着时间的推移,NAND闪存的位密度一直不断增加。早期的NAND设备是单层单元(SLC)闪存,这表示每个闪存单元只能存储一位数据。现在,借助多层单元(MLC)技术,闪存的每个单元可以存储两位或更多数据,因此位密度得到提高。这听起来不错,但MLC也有缺点:MLC NAND支持多种电气状态,这也会增加错误率并降低耐久性。一些设备支持将部分(或全部)存储修改为伪 SLC(PSLC)模式。

这样可以减小存储尺寸并提高设备的耐久性。由于闪存的价值取决于芯片面积,如果在同等面积内可以存储更多数据,那么闪存将更具成本效益。NAND闪存主要分为四种类型:单层单元(SLC)、多层单元(MLC)、三层单元(TLC)和四层单元(QLC)。

3D NAND 技术

近十年来,3D NAND(亦称垂直NAND)是闪存市场最大的创新之一。闪存制造商开发了3D NAND来解决缩减2D NAND尺寸时遇到的问题,旨在以更低的成本实现更高的存储密度。此外,这项技术还带来了速度提升、耐久性增加和功耗降低。与2D NAND中不同,制造商选择在另一个维度上堆叠单元,因而创造了单元垂直堆叠的3D NAND。堆叠消除了单元尺寸缩小时会产生的电气干扰。由于存储密度更高,因此能够实现更大的存储容量,而价格却不会大幅上升。此外,3D NAND还具有更好的耐久性和更低的功耗。

3D NAND

目前,各大SSD供应商都在销售3D NAND SSD。例如,借助该项技术,三星的新款NVMe NF1 SSD中装载了8 TB的闪存。英特尔公司、三星海力士、SK以及东芝的合作伙伴Western Multimedia Corporation都是当下领先的3D NAND闪存制造商。总体而言,NAND是一种非常重要的存储技术,因为它能够以较低的每位成本提供快速的擦除和写入速度。数据中心、电信、汽车、个人电脑等各行各业都在从HDD过渡到SSD,这种过渡推动了NAND技术的不断发展,从而满足消费者日益增长的存储需求。

NAND闪存的主要特性

-

有效防止损耗(磨损均衡):智能闪存驱动器使用损耗均衡技术,该技术可以尽可能确保所有闪存单元的磨损程度相近,而不是过度损耗某一些闪存单元。限制每页的程序数量可以实现适当的芯片损耗均衡。

-

检测和纠正错误(纠错码):NAND非易失性存储器在正常运行过程中通常会在某一时刻出现轻微的数据损坏。这可能是由于磨损或其他干扰造成的。因此,信息由纠错码(ECC)保护有助于检测损坏的数据及纠正信息。

-

坏块处理能力:ECC提供了将被纠正的比特数,并为检测到的最大错误数定义了阈值。一旦达到阈值,信息就会被纠正,并被移动到设备上的正确块。之前的位置被标记为坏块。坏块不再被使用,因为它们可能已损坏。

内存验证挑战与新思科技验证解决方案:

设计NAND闪存IP的过程中存在着各种挑战,而新思科技验证解决方案可以帮助开发者克服所有这些挑战:

-

不断增长的内存大小:新思科技的可配置内存解决方案提供各种密度范围验证ONFI验证IP,能够验证LUN、目标、块、页以及每页数据字节数等等。

-

更高的速度支持:凭借双向源同步DQS和可扩展I/O接口,NAND闪存接口能够提供更快的速度,最高可达3600MTs。

-

多控制器设计:新思科技验证IP的可配置参数页面为控制、器提供了所有器件的相关功能,从而能够加快设计、认证和测试速度。参数页面通过描述修订信息、功能、组织时间以及其他供应商特定数据,解决了器件之间的不一致问题。

-

接口切换:内存解决方案支持在异步和源同步模式之间进行切换。

-

外形尺寸小:先进的裸片选择功能可以减少芯片使能(CE)引脚的数量,进而能够减少控制器引脚的数量,从而提高PCB布线效率(固态驱动器(SSD)、手机存储、嵌入式内存卡、USB设备等等均采用NAND非易失性存储技术实现)。

-

供应商支持:美光、三星、赛普拉斯半导体、华邦以及铠侠等各大公司均提供了广泛的市场支持,并且各家供应商均提供了特定零部件支持功能。

-

调试时间:原生集成Verdi协议分析器、跟踪文件、调试端口、详细错误信息功能。

-

各种覆盖模型:内置覆盖模型和验证计划、配置使随机测试平台能够完全覆盖所有配置和所有供应商组件。

总结与展望

所有主要闪存制造商都在积极采用各种方法来降低闪存的每位成本,同时创造出适用于各种应用的产品。闪存制造商还在积极展开研究,期望能够扩展3D NAND闪存的垂直层数。虽然15nm似乎是NAND闪存目前能够达到的最小节点,但开发者依然在不懈地追求缩小闪存的光刻节点。此外,闪存制造商也在积极探索将MLC和TLC技术与3D NAND闪存技术相结合,许多制造商已经看到了胜利的曙光。随着新技术的出现,有望很快能够实现每个内存单元可以存储一个字节的数据,而垂直层数则可以达到256层甚至更多。

目前,市面上的NAND闪存产品使用以下两种接口:开放式NAND闪存接口(ONFI)和Toggle NAND接口(TNAND、3DNAND)。新思科技的NAND闪存验证IP提供了一套全面的协议、方法、验证和效率功能,使开发者能够加速实现验证收敛。此外,新思科技的验证解决方案允许开发者根据需要随机配置闪存的多种选项,这样不仅可以满足IP和SoC层面的要求,而且还可以支持三星、美光、华邦、东芝和铠侠等供应商的特定零部件。

新思科技验证IP原生集成了新思科技的Verdi协议分析器调试解决方案以及Verdi性能分析器。新思科技验证IP可以在运行时动态切换速度配置,并提供了一组广泛且可定制的帧生成和错误注入功能。

在SoC上运行系统级有效载荷需要更快的、基于硬件的流片前解决方案。基于新思科技IP的新思科技事务处理器、内存模型、混合和虚拟解决方案可在业界速度最快的验证硬件系统新思科技ZeBu和新思科技HAPS上实现各种验证和验证用例。

关于基于应用的内存验证挑战以及如何在各行各业的垂直领域中使用不同类型的NAND闪存,点击“阅读原文”,了解更多。

-

新思科技

+关注

关注

5文章

979浏览量

52989

原文标题:NAND闪存加速度,推动Multi-Die验证新范式

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

石英加速度计让空间受限的平台拥有“高精度感知”

软件定义的硬件辅助验证如何助力AI芯片开发

加速度计伺服电路模块原理与应用

新思科技以AI驱动EDA加速Multi-Die创新

如何为你的项目选择合适的加速度计?

加速度传感器可以测量物体的垂直移动速度吗?

mems加速度传感器都有哪些类型?这三种mems加速度计各有什么利弊?

加速度传感器需要考虑的五大因素

石英加速度计如何成为航空航天测量线性加速度的核心器件?

MEMS加速度计与石英加速度计的发展现状与水平对比

洞察万物运动:详解加速度计的分类与广泛应用

为什么在振动分析中加速度计最常用?

Murata加速度传感器的FAQ

NAND闪存加速度,推动Multi-Die验证新范式

NAND闪存加速度,推动Multi-Die验证新范式

评论