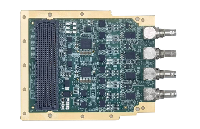

一、板卡概述

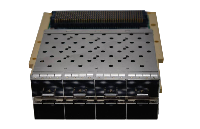

板卡为标准FMC接口子卡,ADC采用两片TI的ADS54J60,4通道1Gsps,16bit,DAC采用2片TI的DAC39J84,4通道16bit1.25Gsps时钟采用HMC7044,支持板上时钟和外接时钟;共10个SSMB接口,1个FMC/HPC接口。

二、性能指标

| 板卡功能 | 参数 | 内容 |

| ADC | 芯片型号 | ADS54J60 |

| 路数 | 4路ADC, | |

| 采样率 | 1Gsps | |

| 数据位 | 16bit | |

| 数字接口 | JESD204B | |

| 模拟接口 | 交流耦合 | |

| 模拟输入 | ±1V | |

| 输入阻抗 | 50Ω | |

| 模拟指标 | ||

| DAC | 芯片型号 | DAC39J84 |

| 路数 | 4路DAC, | |

| 转换率 | 1.25Gsps | |

| 数据位 | 16bit | |

| 数字接口 | JESD204B | |

| 模拟接口 | 交流耦合 | |

| 模拟输出 | ±1V | |

| 输出阻抗 | 50Ω | |

| 模拟指标 | 信噪比SNR:69.327dBFS | |

| 时钟 | PLL芯片 | HMC7044 |

| 板载晶振 | 10MHz温补晶振VCXO | |

| 外输入时钟 | 默认10MHz,3.3VLVTTL电平 | |

| 外触发 | 路数 | 1路输入 |

| 电平 | 3.3VLVTTL电平 | |

| 连接器类型 | FMC-LPC | ASP_134604_01 |

| 前面板 | 10路SSMB | |

| 板卡标准 | FMCANSI/VITA57.1-2008 | |

| 板卡尺寸 | 69X76.5mm | |

| 板卡重量 | (含散热片) | |

| 板卡供电 | +12V@1A | |

| 板卡功耗 | 8W | |

| 工作温度 | Industrial-20℃到+70℃ | |

| 支持母板 | Xilinxboard | V6、V7、KU、VU、ZYNQ、ZU开发板 |

| Orihardboard | 136、270、367、288、330、274、3、9 |

四、板卡应用

板卡配置FPGA母板用于模拟信号、无线电、光电、雷达的采集输出场景。

三、软件内容

提供ISE或者Vivado版本的FMC接口AD输入或者DA输出,时钟配置、外触发接入的参考测试程序,支持的FPGA型号或者板卡见说明书表格。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22508浏览量

639473 -

adc

+关注

关注

100文章

7950浏览量

556976 -

FMC

+关注

关注

0文章

115浏览量

20763

发布评论请先 登录

相关推荐

热点推荐

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析 在电子设计领域,ADC(模拟 - 数字转换器)一直是信号处理系统中的关键组件。今天,我们来深入探讨Analog

数据采集IO卡设计原理图:136-KC705E增强版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

FMC子卡模块, Kintex-7 XC7K325T板卡, 高速信号处理, 软件无线电处理平台, 数据采集IO卡

高速采集卡丨AD 采集丨 多通道数据采集卡丨高速数据采集系统丨青翼科技FMC 子卡

FMC119 是一款基于 VITA57.1 标准规范,实现 2 路 24-bit、 2MSPS 采样率的 AD 采集子卡模块。该模块遵循 VITA57.1 标准,可 作为一个理想的模块直接与符合

视频图像FMC子卡丨高速采集卡丨高速数据采集卡丨数据采集卡丨青翼凌云优质视频图像FMC子卡模块

该板卡支持 2 路 TLK2711 数据的收发,支持线速率 1.6Gbps,经过 TLK2711 高速串行收发器,可以将 1.6Gbps 的高速串行数据解串为 16 位并行数据以及一路随路时钟,通过

【FMC129】基于 VITA57.1 标准的 JESD204B 接口 8 通道 125MSPS 16 位 AD 采集子卡模块

FMC129是一款8通道125MHz采样率16位AD采集FMC子卡,符合VITA57.1规范,可以作为一个理想的IO模块耦合至FPGA前端,8通道AD通过高带宽的

FMC子卡模块设计方案:FMC160-两路14位400Msps AD,两路16位400Msps DA FMC子卡模块

CameraLink图像模拟源, FMC子卡, FMC子卡模块, 万兆网络的触发采集, 中频信号

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

【FMC213】青翼凌云科技基于 VITA57.1 标准的 8 路 SFP+光纤通道数据传输 FMC 子卡模块

FMC213 是我司自主研制的一块基于 FMC 标准的 8 路万兆光纤 子卡模块。该板卡符合 VITA57.1 标准,该板卡可以作为一个理想

【FMC214】青翼科技基于 VITA57.1 标准的 4 路 3G/6G/12G SDI 高清视频传输 FMC 子卡模块

该板卡支持 SDI 双向输入/输出,可以通过配置实现输入或者输出的切换。

该 FMC 子卡与基于 Xilinx FPGA 开发板配合,快速搭建起高速SDI 视频图像传输的验证平台,可广泛适用于

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

1. 概述PC7044是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044具有两个整数

发表于 05-08 15:57

FMC子卡设计资料原理图:FMC451-基于JESD204B的4路1GspsAD 4路1.25Gsps DA FMC子卡

FMC子卡设计资料原理图:FMC451-基于JESD204B的4路1GspsAD 4路1.25Gsps DA FMC子卡

评论