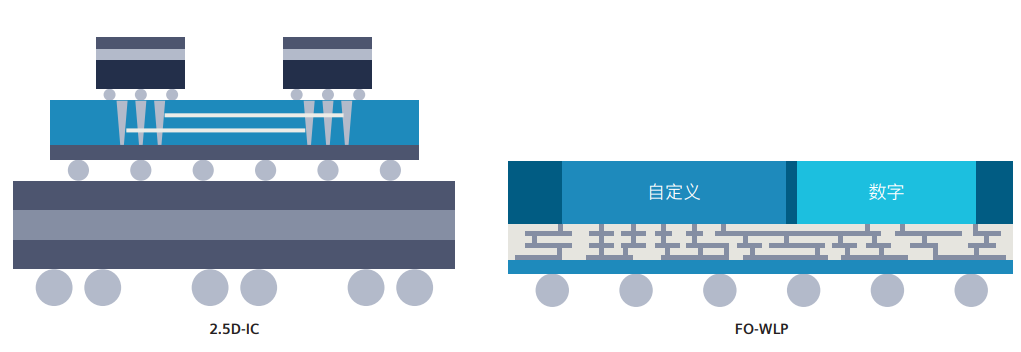

领先的晶圆代工厂组装和封测代工厂 (OSAT) 已经在为其客户提供高密度先进封装(HDAP) 服务了。晶圆代工厂/OSAT 目前提供的常见方法包括 2.5D-IC(基于中介层)和扇出型晶圆级封装(FOWLP) 方法(单裸片或多裸片),如图 1 所示。

图 1. 目前最常使用的封装类型是 2.5D-IC 和 FO-WLP。

由于 2.5D-IC 的中介层类似于传统的裸片(除了不包括有源器件),所以通常由 IC 设计组负责 2.5D-IC 设计,而这需要采用面向 IC 的设计方法(版图数据库中的曼哈顿形状、SPICE/Verilog 作为源网表等)。

在 FO-WLP 中,IC 封装组采用的设计方法通常基于电子表格(以捕捉设计意图)、设计内制造检查的设计方法,而且(传统上)没有自动版图与电路图比较(LVS) sign-off。自动化的 LVS 过去在封装领域并不流行,因为元器件和所需 I/O 的数量通常很少,一张简单的电子表格或焊线图足以满足肉眼检查的需要。但随着 HDAP 的发展及其使用范围的扩大,对使用类似 LVS 的自动化流程来检测和高亮显示封装连接关系错误的需求变得越来越明显。

要想成功识别芯片缺陷,必须对器件应用高质量的测试,以及在出现失效时执行准确的诊断。设计人员通常选择使用既针对固定故障,也针对各种时序故障模型的测试向量。高质量的测试标准可以确保制造测试流程不会遗漏有缺陷的元件。

此外,嵌入式分析技术也被越来越多地用于识别芯片缺陷以及设计的预期功能中存在的异常,这些异常可能是由于缺陷,也可能是由于软件错误和网络安全威胁所致。本文聚焦的安全应用需要极高水平的测试质量,并且支持对现场退货进行全面诊断。本文将讨论运用嵌入式确定性测试来实现安全应用所需的可测试性和高安全性水平的测试方法,以及如何应用嵌入式分析技术在器件的功能层面提供一个安全层。

审核编辑:汤梓红

-

晶圆

+关注

关注

53文章

5451浏览量

132768 -

IC设计

+关注

关注

38文章

1406浏览量

108431 -

封装

+关注

关注

128文章

9339浏览量

149062 -

LVS

+关注

关注

1文章

38浏览量

10524

原文标题:白皮下载丨封装设计人员需要装配级 LVS 进行 HDAP 验证

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

器件高密度BGA封装设计

简单介绍IC的高性能封装

直到PCBA装配不了,才知道封装设计丝印标示的重要

【限时免费】《PCB封装设计指导白皮书》携全套最新“封装实战课程”再度来袭!

解决高密度先进封装的设计与验证挑战

PCB设计人员需要掌握的技能

为什么需要封装设计?

封装工艺简介及元器件级封装设备有哪些

封装设计人员需要装配级LVS进行HDAP验证

封装设计人员需要装配级LVS进行HDAP验证

评论