多埠暂存器阵列

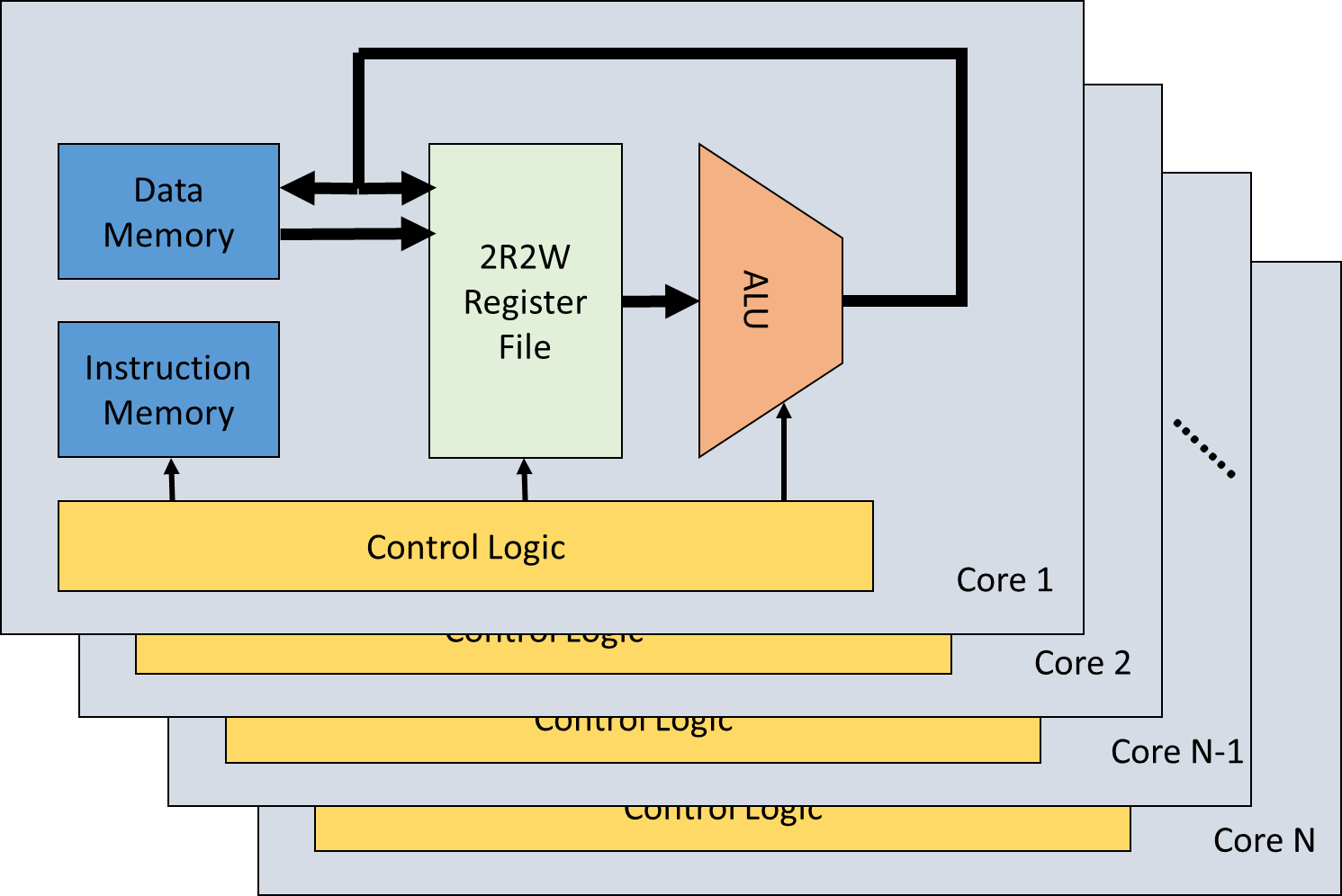

多埠暂存器堆,简单来说是处理器中多个暂存器所组成的阵列,故又称多埠暂存器阵列,是处理器(如中央处理器、内嵌式处理器或神经网络处理器)中常见的记忆体,用于暂存指令、数据和位址。暂存器阵列的存贮容量十分有限,但却有读写速度快的优点,因此在处理器架构裡,暂存器阵列被用来储存运算单元计算的中间结果,利用快速存取资料来支援运算单元并改善处理器运算效能。

多埠暂存器阵列的实现方式有两种,其一,藉由逻辑合成的方式,使用标准原件库中的闩锁器或正反器构成;而另一种方式,是使用客製化的多埠静态随机读写存储单元,实现客製化的暂存器阵列,这种多埠存储单元具有专门的读埠与写埠,可以支援多路同时存储。两者相较,第一种能快速地完成的暂存器阵列的设计与实现,而第二种方式则可以提供较佳的面积与效能。

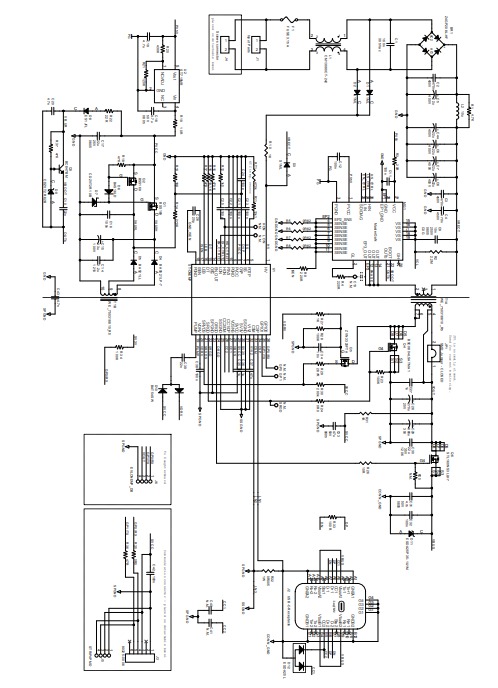

图: 2R2W Register File in Multi-core Computing Structure

图: 2R2W Register File in Multi-core Computing Structure分时多工的创新技术

针对客製化实现多埠暂存器阵列,M31提出分时多工的创新技术,优化暂存器阵列的控制单元,有效提高记忆体单元的储存与读取频宽,可使用晶圆厂提供的标准静态随机读写存储单元(如单埠记忆体单元、双埠记忆体单元)完成多埠暂存器阵列设计与实现。此一创新技术,不但可以缩短设计时间、缩短交货流程,更可以提供最佳优化面积与效能的多埠暂存器阵列,协助客户完成更具有竞争力的处理器设计。

客製化记忆体模组区块

M31提供完善的设计解决方案,採用TSMC 12奈米先进製程,针对市场的超高速操作需求,提供2R2W的4埠静态随机读写暂存器(SRAM),各埠皆有独立的操作模式,且不能互相干扰,此外,M31记忆体团队使用读写的屏蔽技术,确保操作时资料读写的稳定性,并同时兼顾CPU/NPU对于平行处理资料运算读写的需求;而针对晶圆厂的SRAM bit cell架构,M31所客製化记忆体模组区块,可大幅减少由传统闩锁器或正反器组成所消耗的面积与功耗,并且,M31开发出boosted amplifier架构,克服bit cell自身读取速度的极限,能进一步满足处理器内部大于兆频以上的超高频需求。

-

IP

+关注

关注

5文章

1849浏览量

154923 -

记忆体

+关注

关注

0文章

18浏览量

9905 -

暂存器

+关注

关注

0文章

12浏览量

8200 -

IC芯片

+关注

关注

8文章

264浏览量

27900 -

先进制程

+关注

关注

0文章

89浏览量

8978

发布评论请先 登录

是德E5071C矢量网络分析仪多端口校准与S参数测试技巧

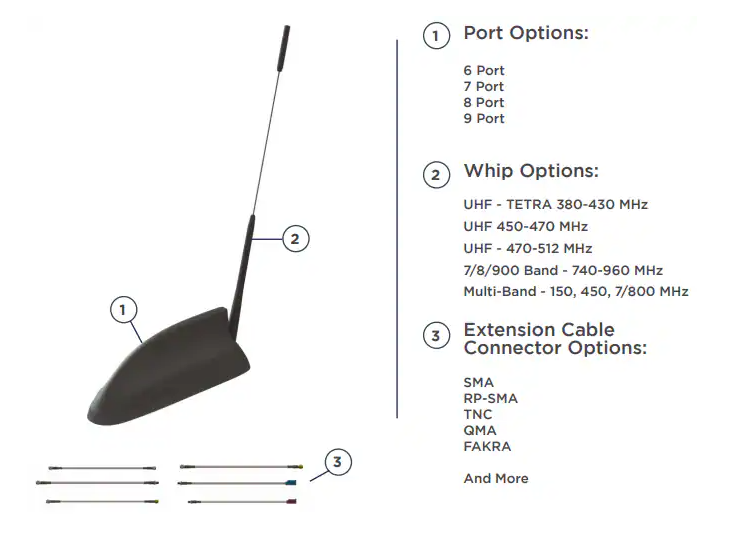

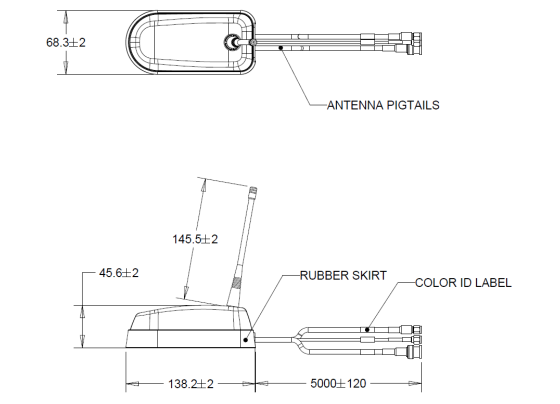

TE Connectivity RP20多端口MIMO FWA全向天线技术解析

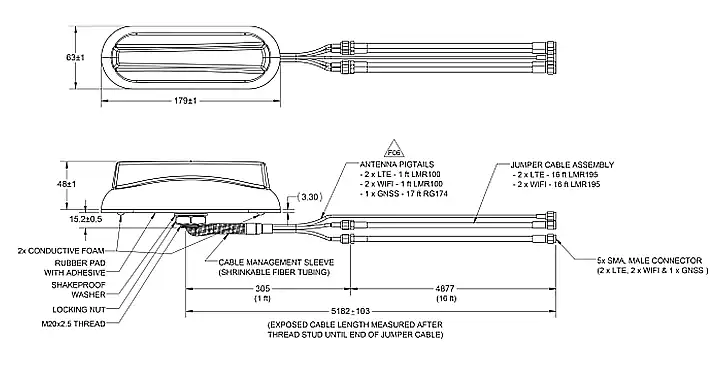

TE Connectivity FP20多端口车载天线技术解析

TE Connectivity VFP69383B22JN 多端口车载天线技术解析

基于TE Connectivity FPL pro多端口车辆天线的技术解析与应用指南

基于STMicroelectronics EVLONEMP评估板的65W多端口快充设计解析

京信通信推出首款多频多端口无源互调分析仪

M31 深耕中国大陆IP市场 赋能汽车电子与 AI 应用新突破

ADS4129后级接缓存器,缓存器出现过热的原因?

M31 12纳米GPIO IP获国芯科技采用,点亮先进制程车用电子芯片创新

M31与国芯科技携手,12纳米GPIO IP点亮车用电子芯片创新

M31全系列车用硅智财解决方案亮相ICCAD 点亮未来車用芯片发展

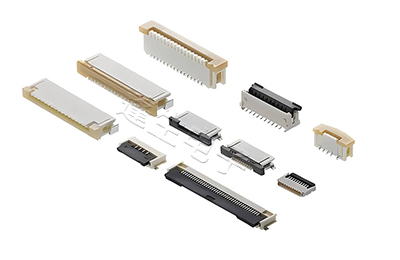

M31谈12 FFC多端口缓存器数组

M31谈12 FFC多端口缓存器数组

评论