作为数字芯片设计流程中的“责任担当”,EDA仿真验证贯穿了芯片立项、架构定义、芯片设计到流片等环节,且在整个研发过程中占了7成左右的时间。面对日益增长的成本及市场压力,寻找灵活的仿真验证技术就显得十分迫切。软件仿真、硬件仿真及原型验证是设计和验证团队在前端的常规选项,三者的搭配往往基于性能、编译时间、设计能力和调试等的需求而定。

软件仿真是最直接的仿真方式,设计工程师会应用硬件描述语言(HDL)来设计数字电路,也就是用软件和编程的方式将硬件特征虚拟出来,通过计算机验证芯片的功能正确性。因此软件仿真可以查看电路中任何地方的信号,但一旦碰到大规模设计数字电路,结构越是复杂,仿真所需要的时间就越长。

所以通过专门的设备在硬件上调试芯片设计, 如硬件仿真和原型验证,是其重要的解决方案之一。硬件仿真和原型验证的效率和速度比软件仿真可要高很多,尤其是硬件仿真,它可以对完整的芯片设计进行自动化的加速仿真并调试,多应用于芯片设计前期的RTL功能验证。另外信号全可视是硬件仿真器的关键特性,因为硬件仿真中含有数量较多的探测仪器、信号记录器等,以记录系统电路运行的每一个时钟周期的数据,以便查找设计错误。

在芯片设计后期的系统级功能和性能验证,就需要用到原型验证。它可以为整个系统、固件以及软件提供一个早期而真实的硬件环境,在流片之前对整个系统进行整体的性能评估和瓶颈分析。工程师将RTL代码转换为可编程逻辑,并部署到FPGA芯片上,即可实现原型与真实世界的数据交互,从而轻松检测出设计中的问题。此外,原型验证可以提供更高的性能,这意味着可以更快地执行验证任务。而更好的软件调试环境使得工程师可以在硬件和软件之间进行快速切换,并通过与真实数据的交互来捕获和解决问题。

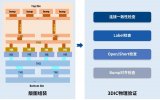

在先进工艺下,异构计算架构正逐渐成为设计芯片的主流,不同的运算单元有不同的架构设计,对信息流也有不同的处理方式,这些都需要针对其特性使用不同验证的方法学。为了缩短芯片的上市周期,在不同设计阶段选择不同的仿真验证工具,提高验证效率,如今已成了各大芯片设计公司的共识,并运用在各大芯片领域。利用异构验证方法,多种不同形式的设计在系统建模(芯神匠),软件仿真(芯神驰),硬件仿真(芯神鼎),原型验证(芯神瞳)得以协同仿真和交叉验证,以确保设计出正确的芯片。

-

芯片

+关注

关注

463文章

54375浏览量

468986 -

eda

+关注

关注

72文章

3140浏览量

183665

发布评论请先 登录

更快抵达终点线:Questa One如何加速整体仿真周转时间

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 芯片“卡脖子”引发对EDA的重视

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况

软件定义的硬件辅助验证如何助力AI芯片开发

西门子EDA AI System驱动芯片设计新纪元

如何缩短电能质量在线监测装置的抗干扰能力验证时间?

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

无惧EDA封锁升级,思尔芯国产方案筑牢客户验证防线

芯华章携手EDA国创中心推出数字芯片验证大模型ChatDV

芯片的验证为何越来越难?

EDA硬核科普|异构验证:整合三大数字芯片验证工具,显著缩短芯片开发周期

EDA硬核科普|异构验证:整合三大数字芯片验证工具,显著缩短芯片开发周期

评论