如今IC 封装的设计周期越来越短,我们必须尽早发现并纠正布线问题,仿真愈发成为设计周期中不可或缺的一部分。Layout工程师希望采用一种快速而准确的方法,通过观察附近信号引起的阻抗值变化和高耦合度来发现layout错误。但遗憾的是,Layout工程师通常没有机会使用昂贵而复杂的信号完整性工具。此外,在项目期限已经很紧张的情况下,他们几乎没有时间学习一种复杂的新工具。

好消息是,Allegro Package Designer Plus 工具内引入了一个高速分析和检查环境。Allegro Package Designer Plus SiP Layout Option 中新集成的设计同步阻抗和耦合工作流程由 Sigrity 求解器提供支持,能够以快速简单的方式分析Layout后的封装,使工程师无需再在复杂的工具上花费时间和精力。

在新发布的Allegro SPB 17.4 版本中,Allegro Package Designer Plus with SiP Layout 增加了一个新菜单,即 Workflow Manager。本文将带领大家了解一下运行阻抗和耦合工作流程的步骤。

步骤一:为封装设计设置仿真环境

在开始仿真之前,请确保满足以下几点要求:

设计必须具备一个地平面

环境变量 sigrity_eda_dir 指向最新的 Sigrity 设置,可以通过 Setup ─ User Preferences ─ Paths ─ Signoise 来访问该变量

步骤二:阻抗分析工作流程

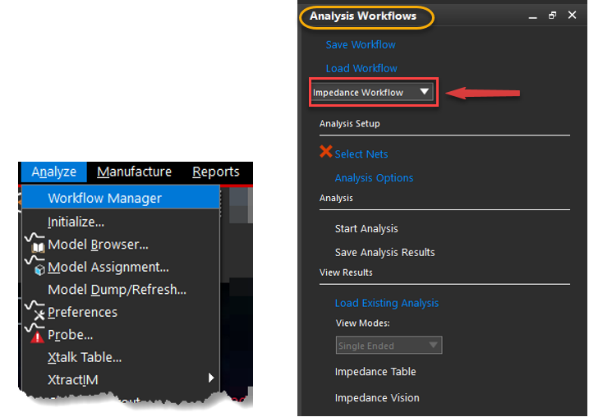

运行阻抗分析工作流程可以识别并解决设计中真正的阻抗问题。在菜单中选择Analyze——Workflow Manager,打开 Analysis Workflows 界面:

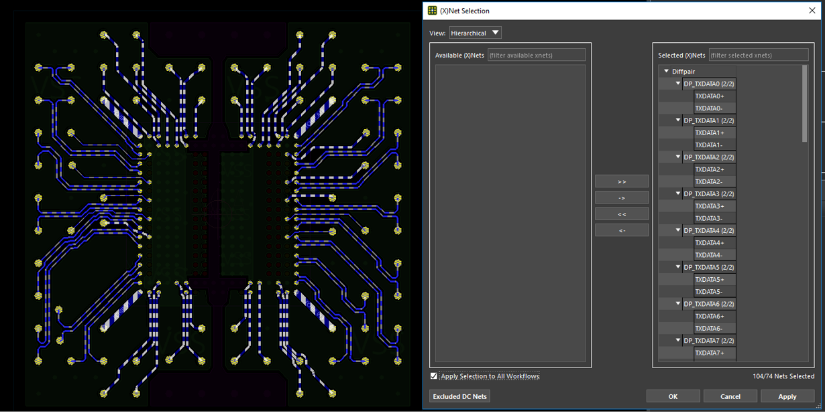

使用 Select Nets 选项来选择设计中的关键网络。这些网络显示在用户界面的 Selected (X)Nets 部分。如果启用 Apply Selection to All Workflows 复选框,所选择的网络也将应用于耦合工作流程。

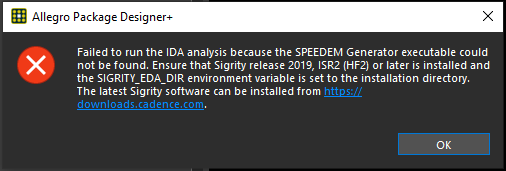

点击 Start Analysis,开始仿真。如果看到下面的失败信息,则表示没有正确设置 sigrity_eda_dir 变量。请打开 User Preferences Editor,确认设置该变量并再次运行仿真。设置和运行仿真非常容易,可以很快完成。

如果没有看到以上消息,则说明运行成功,结果已加载到工作流程之中。阻抗分析在仿真时忽略了设计中存在的引线键合。

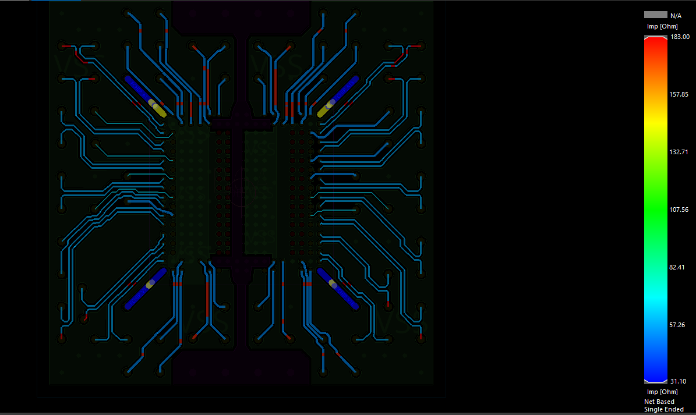

现在,选择 Impedance Vision,在设计界面上叠加阻抗结果的色彩编码视图。色彩编码范围从红色到蓝色,再加上汇总表,可以很容易地找到哪些地方信号阻抗很高,需要快速进行设计修复。

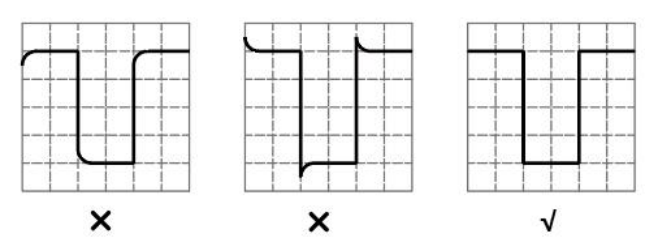

高阻抗可能是由各种原因造成的,如接地平面存在间隙、层发生变化或走线宽度发生变化;但是,有一点是肯定的——高阻抗需要快速进行设计修复。为了使阻抗降到最低,可以点击表格中的数据点,找到该走线。然后修复问题,并重新运行仿真进行验证。

保存分析结果,并在之后需要时重新加载。也可以使用 Save Workflow 选项,保存完整的工作流程选择和设置,然后使用 Load workflow 选项导入工作流程,以便重新使用保存的工作流程。

步骤三:耦合分析工作流程

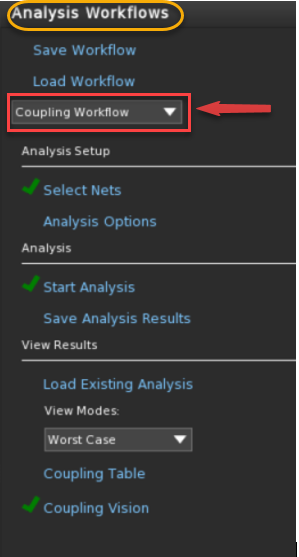

在最后设计确认时,运行“耦合分析”也可以发现潜在的耦合问题。为此,请在 Analysis Workflows 用户界面的下拉菜单中选择 Coupling Workflow。

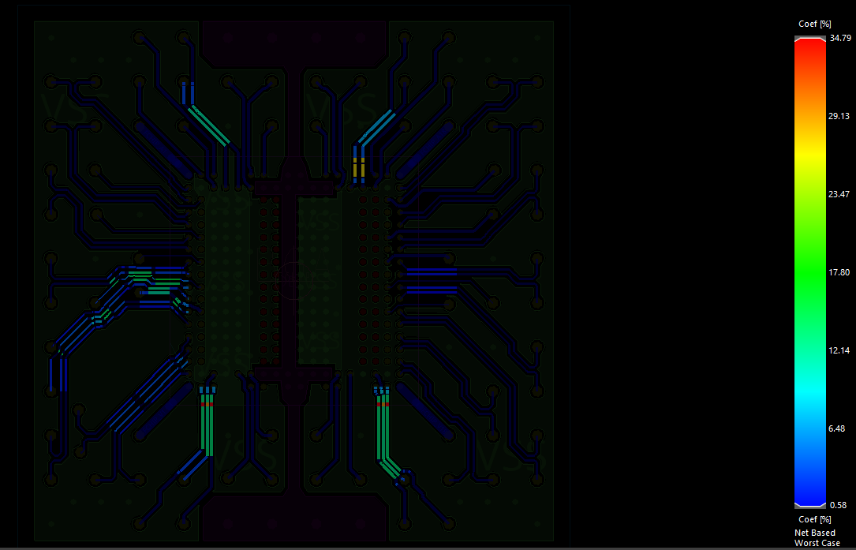

按照阻抗分析流程中提到的方法运行仿真。仿真完成后,选择 Coupling Vision,在设计界面上分析结果。有耦合问题的走线会在画面上突出显示,并在表中列出受影响者 (victim) 和影响源 (aggressor) 网络。调整走线之间的间距,以消除或减少耦合问题。然后再次运行分析,检查纠正措施是否有效。

总结

封装设计中的设计同步分析可以帮助Layout工程师快速找到并解决关键的信号完整性问题,同时无需占用额外时间或资源来学习如何使用复杂的信号完整性工具。

-

IC

+关注

关注

36文章

6474浏览量

186330 -

封装

+关注

关注

128文章

9329浏览量

149039 -

仿真

+关注

关注

55文章

4535浏览量

138659

发布评论请先 登录

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

技术资讯 I 信号完整性与阻抗匹配的关系

深圳 9月12-13日《信号完整性--系统设计及案例分析》公开课,即将开课!

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

了解信号完整性的基本原理

上海 6月20-21日《信号完整性--系统设计及案例分析》公开课,即将开课!

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

受控阻抗布线技术确保信号完整性

信号完整性测试基础知识

技术资讯 I 如何在IC封装中使用”设计同步分析”流程解决信号完整性问题

技术资讯 I 如何在IC封装中使用”设计同步分析”流程解决信号完整性问题

评论