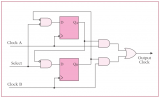

输入sel,clka,clkb,sel为1输出clka,sel为0输出clkb。

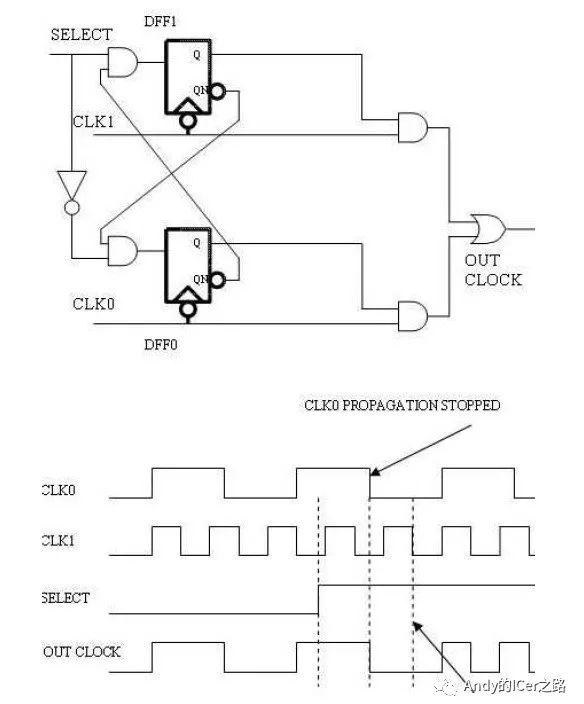

一、两个时钟源是倍数的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out1;

reg out0;

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= ~out0 & select;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= ~select & ~out1;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule

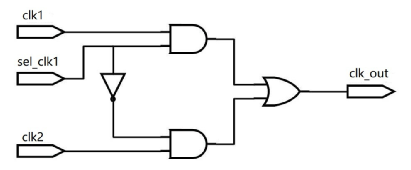

二、两个时钟源为异步时钟的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out_r1;

reg out1;

reg out_r0;

reg out0;

always @(posedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r1 <= 0;

else

out_r1 <= ~out0 & select;

end

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= out_r1;

end

always @(posedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r0 <= 0;

else

out_r0 <= ~select & ~out1;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= out_r0;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟源

+关注

关注

0文章

113浏览量

16820 -

CLK

+关注

关注

0文章

132浏览量

18097 -

异步时钟

+关注

关注

0文章

18浏览量

9580 -

时钟切换电路

+关注

关注

0文章

7浏览量

5922

发布评论请先 登录

相关推荐

热点推荐

FPGA的时钟门控是好还是坏?

喜我对时钟门控有一些疑问。从我所读到/学到的东西 - 时钟门控可用于低功率fpga设计(关闭时钟以防止元件切换以节省功率)。但是,我还读到

发表于 02-21 10:21

比特翻转现象:GLitch是第一个利用JavaScript入侵智能手机

的比特。 GLitch 也是第一个利用标准 JavaScript 入侵智能手机的 Rowhammer 攻击,意味着只需要用户访问一个恶意之后就能能利用漏洞远程执行代码。

一个时钟异步切换原理图

首先肯定是在本时钟域内的clk_en会先变低(invalid),之后才会使得另外时钟域内的clk_en变高(valid),这时另外一个时钟域

基本时钟切换术语和标准输入时钟切换配置资料下载

电子发烧友网为你提供基本时钟切换术语和标准输入时钟切换配置资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料

发表于 04-05 08:40

•7次下载

HMC305S:Glitch Free.5 db-5位Serical Service Serical Services Services Attrator,0.4-7.0 GHz数据Sheet

HMC305S:Glitch Free.5 db-5位Serical Service Serical Services Services Attrator,0.4-7.0 GHz数据Sheet

发表于 05-17 14:30

•0次下载

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是

怎么设计一个Glitch Free的时钟切换电路呢?

怎么设计一个Glitch Free的时钟切换电路呢?

评论