1、Chiplet是国内半导体弯道超车的重要途径,市场规模有望快速增长

1.1、Chiplet为后摩尔时代提升芯片算力与集成度的重要途径

摩尔定律指引过去几十年集成电路产业发展。摩尔定律由英特尔创始人之一的戈登·摩 尔(Gordon Moore)提出,其核心内容为:在价格不变时,集成电路上可以容纳的晶体 管数量每 18-24 个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降 为之前的一半。在过去几十年,摩尔定律指引着集成电路产业发展。随着工艺进步,集 成电路上晶体管密度不断提升,驱动计算机性能保持几何级数增长,而性能的快速提升 则推动芯片价格迅速下降。

“摩尔定律”发展陷入瓶颈,集成电路进入后摩尔时代。从 1987 年的 1um 制程至 2015 年的 14nm 制程,集成电路制程迭代大致符合“摩尔定律”的规律。但自 2015 年以来, 集成电路先进制程的发展开始放缓,7nm、5nm、3nm 制程的量产进度均落后于预期。随 着台积电宣布 2nm 制程工艺实现突破,集成电路制程工艺已接近物理尺寸的极限,摩尔 定律发展陷入瓶颈,行业进入了“后摩尔时代”。

Chiplet 可在不改变制程的前提下提升算力,且保证芯片良率。Chiplet 俗称“芯粒”, 又称“小芯片组”,从字面意义上可以理解为“粒度更小的芯片”。它是将一类满足特 定功能的 die,通过 die-to-die 内部互联技术实现多个模块芯片与底层基础芯片封装 在一起,进而形成一个系统芯片。它可以有效提升芯片的集成度,是在不改变制程的前 提下提升算力,并且保证芯片生产良率的一种手段。

资料来源:EE Times,东莞证券研究所

与传统 SoC 相比,Chiplet 在设计灵活度、设计与生产成本、上市周期等方面优势明显。传统 SoC,即系统级单芯片,是将多个负责不同类型计算任务的计算单元,通过光刻的 形式制作到同一块晶圆上。随着摩尔定律放缓,传统的 SoC 的生产周期越来越长,在成 本大幅增加的情况下性能提升幅度有限,行业接近制造瓶颈;与 SoC 不同,Chiplet 是 将一块原本复杂的 SoC 芯片,从设计时就先按照不同的计算单元或功能单元对其进行分 解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将 各个单元彼此互联,最终集成封装为一个系统级芯片组。

相比传统的 SoC,Chiplet 能够有效降低研发、设计与制造成本,并显著提升芯片良率。英特尔公司高级副总裁、中国区董事长王锐在 2022 世界集成电路大会上表示,Chiplet 技术是产业链生产效率进一步优化的必然选择。“不但提高芯片制造良品率,利用最合 适的工艺满足数字、模拟、射频、I/O 等不同技术需求,而且更将大规模的 SoC 按照不 同的功能,分解为模块化的芯粒,减少重复的设计和验证环节,大幅度降低设计复杂程 度,提高产品迭代速度。且有利于后续的产品迭代,缩短上市周期。”

Chiplet 优势一:降低芯片设计的复杂程度,有效降低研发与设计成本。Chiplet 芯粒 设计灵活,且可重复使用,通过将已知的合格芯片裸片进行集成,能够缩短芯片的研发 与设计周期,降低研发设计成本。据悉,设计 28nm 芯片的平均成本为 4,000 万美元, 设计 7nm 芯片的成本上升至 2.17 亿美元。而 The Linley Group 的白皮书《Chiplets Gain Rapid Adoption:Why Big Chips Are Getting Small》中提出,Chiplet 技术可以将大 型 7nm 设计的成本降低 25%。

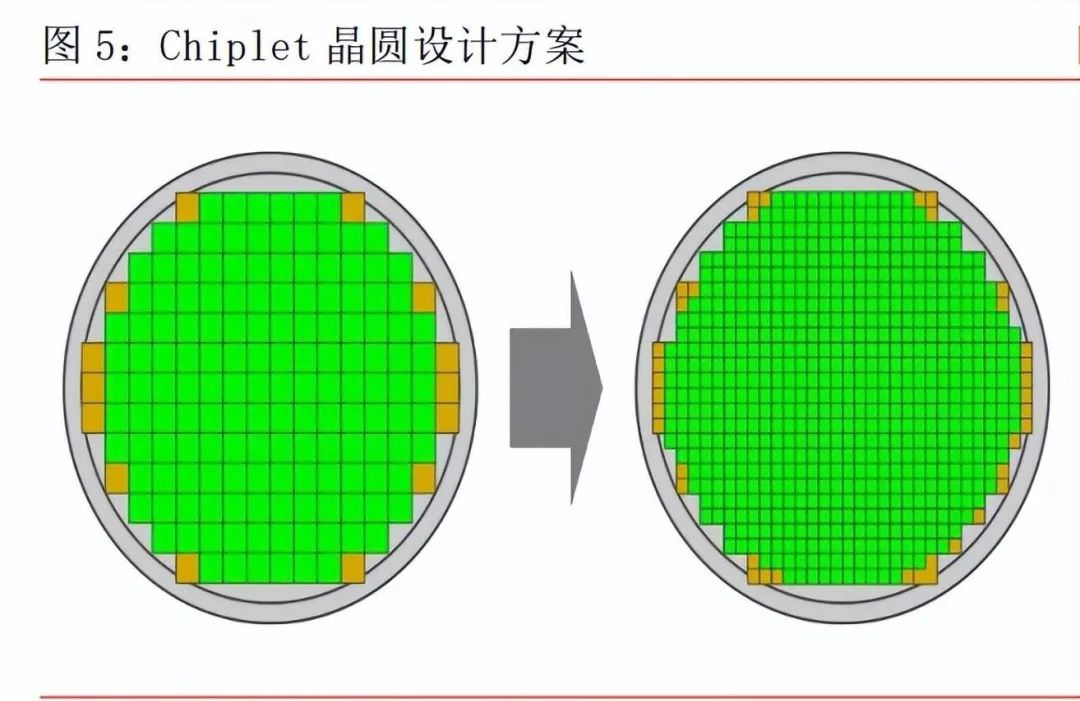

Chiplet 优势二:提升良率。SoC 将多个不同类型计算任务的计算单元以光刻形式集成 在同一片晶圆上,随着先进制程不断推进,单位面积上集成的晶体管数量越来越多,设 计周期越来越厂,芯片面积也在加大。高性能计算等领域巨大运算需求推动逻辑芯片运 算核心数量上升,配套 SRAM 容量、I/O 数量随之提升。随着芯片面积的加大和集成的 晶体管数量增多,对制造过程中的芯片良率提出较高挑战,让芯片生产中的工艺误差和 加工缺陷显得愈发明显,一个微小的缺陷就可能导致整个大芯片报废。Chiplet 技术将 大芯片分割成不同功能模块进行独立制造,通过将广泛的、成熟的芯片裸片进行集成, 只需保障各个被集成的成熟芯片良率即可,能够降低先进制程的研发与制造风险,有效 提升良率。

资料来源:台积电法说会,东莞证券研究所

Chiplet 优势三:大幅降低芯片制造成本。SoC 中的逻辑计算单元对性能要求高,整体 依赖先进制程,具有极高的生产壁垒与制造成本;Chiplet 方案则可针对不同的模块采取不同的合适的制程,分开制造,最后采用先进封装技术进行组装,能大幅降低芯片的 制造成本。

后摩尔时代,Chiplet 成为提高芯片算力与集成度的重要途径。后摩尔时代,随着集成 度提升,SoC 开始在供电、功耗和散热等方面面临挑战,芯片全流程设计成本大幅增加, 而制程工艺接近极限,每次迭代升级都需要付出极大的额外成本,而随着性能提升,发 热功耗等方面的问题也日益凸显,继续追求极致工艺的意义已经不大。Chiplet 作为当 下较受关注的半导体发展方向,可有效降低能够有效降低芯片设计与制造的门槛,提升 良率和节约成本,因此成为摩尔定律趋缓背景下提升芯片集成度与算力的重要途径。

1.2、海外科技领域制裁加剧,Chiplet助力国内半导体产业弯道超车

海外科技领域制裁加剧,国内半导体先进制程发展受限。近年来中美摩擦加剧,美国针 对中国在高科技领域的限制增多,企图通过加大制裁力度来限制国内集成电路产业发展。2020 年 12 月,美国将中芯国际列入“实体清单”,限制企业 14nm 及以下半导体制程的 扩产;2022 年 8 月,美国签署《芯片与科学法案》,主要用于增强美国本土晶圆厂的竞 争力,并明确规定获得美国政府补贴的企业,10 年内不得在中国大陆扩产 28nm 以下的 芯片制造。《芯片法案》的签署,进一步加剧了中美在高科技领域的脱钩程度,导致国 内芯片先进制程发展受到限制。

先进制程是提高算力的必要途径,台积电先进制程占比不断提高。近年来,人工智能、 大数据、自动驾驶和 AIoT 等下游应用的不断发展,对芯片处理与运算能力提出更高的 要求,高性能、低功耗成为先进制程的发展方向。从全球晶圆代工龙头台积电的各制程 营收占比来看,近年来台积电先进制程营收占比不断提升:2022 年前三季度,台积电实 现营收 6,131.4 亿元新台币,其中 5nm 制程占比 28%,7nm 制程占比 26%。而分地区看, 近年来台积电来自大陆市场的营收占比有所下滑。2022 年,美国市场成为台积电最大来 源,营收规模达 1.49 万亿新台币,占比 65.96%,中国大陆市场营收 2,451.68 亿元,占 比 10.82%,相比 2020 年的 17.45%大幅下滑。

资料来源:Omdia,东莞证券研究所

海外制裁加剧,Chiplet 有望助力国内半导体产业实现弯道超车。通过先进制程可实现 芯片性能的迅速提升,因此全球晶圆代工龙头先进制程占比不断提升,而中国大陆先进 制程发展受到限制。Chiplet 技术仅对核心 Chip 采用先进制程,其他如存储芯片、I/O 芯片采用成熟制程,有效降低对先进制程的依赖,有望成为我国半导体产业弯道超车的 突破口。2022 年 12 月,我国第一个原生 Chiplet 技术标准——《小芯片接口总线技术 要求》团体标准正式发布,这个标准涵盖了多种应用场景的小芯片接口总线技术要求, 包括总体概述、接口要求、链路层、适配层、物理层和封装要求等,能够灵活应对不同 的应用场景、适配不同能力的技术供应商。《总线技术要求》的发布,对于我国集成电 路产业延续“摩尔定律”,打破先进制程限制因素,提升产业综合竞争力,具有重要意 义。

1.3、新互联标准提供行业规范,Chiplet市场规模有望快速扩张

新互联标准 UCle 出台,为集成不同芯片提供标准与技术支持。尽管 Chiplet 优势明显, 但由于过去 Chiplet 互联标准并不统一,各类 Chiplet 产品接口有所不同,无法“拼接” 在一起,因此行业发展受到制约。2022 年 3 月,AMD、英特尔、台积电、三星、美光、 微软、Meta、Google 等十余家半导体、互联网行业巨头联合成立了 Chiplet 标准联盟, 正式推出了通用 Chiplet 高速互联标准“Universal Chiplet Interconnect Express” (通用芯粒互连,简称“UCIe”),旨在定义一个开放、可互操作的 Chiplet 生态系统 标准。业内巨头联手推动 Chiplet 接口规范的标准化,以实现 Chiplet 在封装级别的普 遍互联,构建开放的 Chiplet 生态系统,有助于 Chiplet 行业快速发展。

UCle 是唯一具有裸片间接口堆栈的标准,成为 Chiplet 设计的首选标准。此前为应对 Chiplet 设计中所面临的挑战,行业出现了集中不同的标准,但 UCle 是唯一具有完整裸 片间接口堆栈的标准,其他标准都没有为协议栈提供完整裸片间接口的全面规范,大多 仅关注在特定层。而且 UCIe 支持 2D、2.5D 和桥接封装,预计未来还会支持 3D 封装。新思科技(Synosys)指出,Ucle 的堆栈本身拥有三层:协议层:最上层为协议层,通过基于流量控制单元(FLIT)的协议实现,确保最大效率 和降低延迟,支持最流行的协议,包括 PCI Express(PCIe)、Compute Express Link (CXL)和/或用户定义的流协议;

中间层:用于对协议进行仲裁与协商,以及通过裸片间适配器进行连接管理。基于循环冗余检查(CRC)和重试机制,该层还包括可选的错误纠正功能;物理层:定义了与封装介质的电气接口,是电气模拟前端(AFE)、发射器和接收器以 及边带通道允许两个裸片之间进行参数交换与协商的层级。逻辑 PHY 实现了连接初始化、 训练和校准算法,以及测试和修复功能。

资料来源:Yole,东莞证券研究所

国内厂商纷纷加入,直接受益于 Chiplet 发展趋势。Ucle 的提出,为集成不同制程工艺、 不同厂商、不同技术的芯片提供了标准与技术支持,让晶圆代工厂可以对不同类型的芯 片进行集成,有助于 Chiplet 行业快速走向成熟。经过数年发展,Chiplet 技术已逐渐 走向商用,成为芯片厂商较为依赖的技术手段,也被认为是未来芯片行业发展的重要方 向。截至目前,芯原股份、长电科技、OPPO、阿里巴巴等众多国内知名企业已加入 UCle 联盟中,直接受益于相关技术标准,共同构建 Chiplet 生态体系,助力行业快速发展。

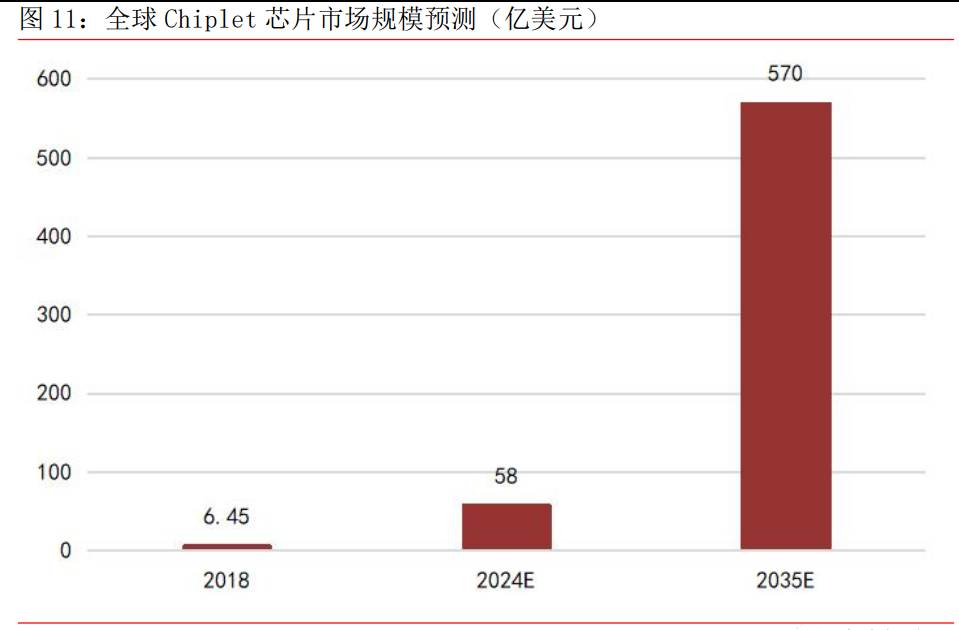

Chiplet 市场规模不断扩张,预计 2034 年有望达到 570 亿美元。Chiplet 可在一定程度 上避免摩尔定律放缓的窘境,全球半导体龙头企业积极推进,市场规模有望实现高速增 长。Omdia 指出,2018 年全球 chiplet 市场规模约为 6.45 亿美元,至 2024 年将达到 58 亿美元,预计到 2035 年有望突破 570 亿美元,2018-2035 年复合增长率超过 30%。

2、Chiplet技术持续推进,先进封装、IC载板、半导体IP等多环节受益

2.1、Chiplet拉动先进封装、半导体测试需求

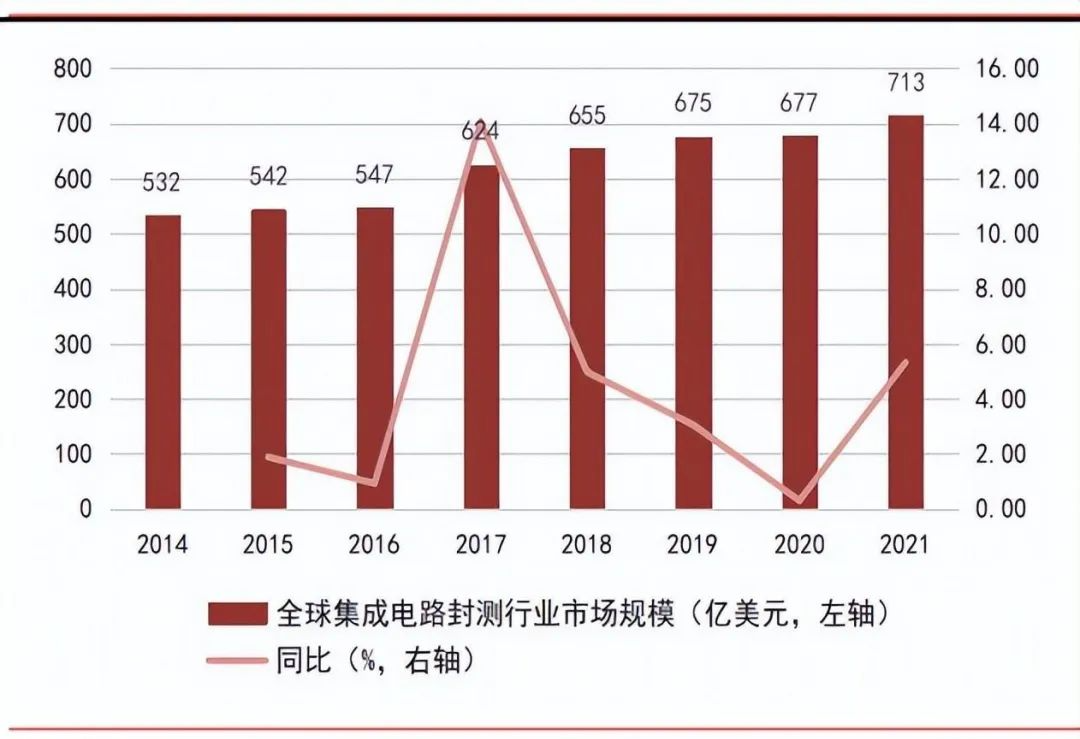

近年我国封测产业稳步发展,行业增速高于全球平均水平。封测行业位于半导体生产制 造环节的下游,需要大量的设备与人员投入,属于资本密集型、人员密集型产业。过去 十余年,在半导体产业转移、人力资源成本优势、税收优惠等因素促进下,全球集成电 路封测产能逐步向亚太地区转移,目前亚太地区占据全球约 80%集成电路封测产能。近 年来,全球集成电路封测产业进入稳步发展期,2014-2021 年行业市场规模复合增长率 为 4.27%,而我国受益于下游智能手机等终端应用的蓬勃发展,封测产业增速领先全球。据中国半导体行业协会数据统计,中国集成电路封测业年度销售额从 2014 年的 1,256 亿美元增至 2021 年的 2,763 亿美元,2014-2021 年符合增长率约为 11.92%,远高于同 期全球平均水平,随着下游应用持续发展以及先进封装工艺不断进步,国内封测行业成 长空间广阔。

本土 IC 设计企业增多,增大下游封测需求。我国的集成电路设计产业发展起点较低, 但依靠着巨大的市场需求和良好的产业政策环境等有利因素,已成为全球集成电路设计 产业的新生力量。从产业规模来看,我国大陆集成电路设计行业销售规模从 2010 年的 550.0 亿元增长至 2022 年的 5,345.7 亿美元,年复合增长率约为 20.87%;而本土产业 链的逐步完善,也为国内初创芯片设计公司提供了晶圆制造支持,叠加产业资金与政策 支持,以及海外人才回流,我国芯片设计公司数量快速增加。据中国半导体行业协会数 据,自 2010 年以来,我国芯片设计公司数量大幅提升,2010 年仅为 582 家,2022 年增 长至 3,243 家,2010-2022 年年均复合增长率约为 15.39%。不断扩大的集成电路设计市 场规模与不断增加的 IC 设计企业数量也增大对下游半导体封装、测试需求,推动我国 集成电路封测产业发展。

资料来源:中国半导体行业协会集成电路设计分会

封测为我国集成电路领域最具竞争力环节,共有四家厂商营收进入全球前十。目前我国 集成电路领域整体国产自给率较低,尤其是在半导体设备、材料与晶圆制造等环节,与 国际领先水平差距较大,而封测为我国集成电路领域最具国际竞争力的环节。近年来, 以长电为代表的几家国内封测龙头企业通过自主研发和并购重组,在先进封装领域不断 发力,现已具备较强的市场竞争力,有能力参与国际市场竞争。据芯思想研究院,2022, 中国大陆有 4 家企业进入全球封测厂商前十名,分别为长电科技、通富微电、华天科技 和智路封测、全年营收分列全球第 3、第 4、第 6 和第 7 位。

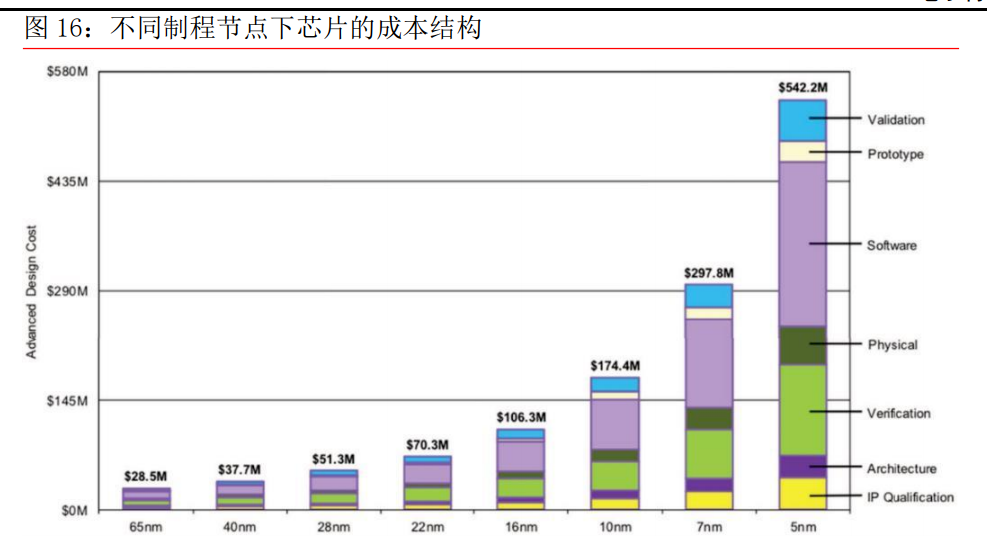

后摩尔时代,先进封装成为提升芯片性能的重要途径。“后摩尔时代”制程技术突破难 度较大,工艺制程受成本大幅增长和技术壁垒等因素,进步速度放缓。据市场调研机构 ICInsights 统计,28nm 制程节点的芯片开发成本为 5,130 万美元,16nm 节点的开发成 本为 1 亿美元,7nm 节点的开发成本需要 2.97 亿美元,而 5nm 节点开发成本则上升至 5.4 亿美元。从产品开发角度,产品进入到大规模量产前需要多次流片验证,带来费用 支出成倍增加。由于集成电路制程工艺短期内难以突破,且制程升级对芯片性能提升的 边际收益有所收窄,通过先进封装技术提升芯片整体性能成为了集成电路行业的一个重 要发展趋势。

先进封装相比传统封装优势明显。先进封装是相对传统封装提出来的概念。传统封装主 要是以引线框架作为载体,采用引线键合互联的形式进行封装,包含 DIP、SOP、SOT、 DFN、BGA 等封装形式;先进封装指当下最前沿的封装形式与技术,目前带有倒装芯片 (Flip Chip,FC)结构的封装、晶圆级封装(Wafer Level Package,WLP)、2.5D 封 装、3D 封装等被认为属于先进封装的范畴。

随着先进制程持续演进,以及电子产品不断向小型化、高速化、系统化与低成本化发展, 传统封装的局限性愈发突出。与传统封装相比,先进封装能够提升芯片的集成密度与互 联速度,有效降低设计门槛,优化功能搭配的灵活性,能够增强芯片性能,并改善散热 和可靠性,因此在高端逻辑芯片、存储芯片、射频、图像处理和触控芯片等领域得到广 泛应用。Yole 指出,2019 年全球先进封装市场规模占总封装市场比重约为 42.60%,预 计 2019-2025 年将以 6.6%的年均复合增长率持续增长,至 2025 年先进封装占整个封装 市场的比重有望接近 50%。

资料来源:IBS,东莞证券研究所

先进封装技术是 Chiplet 的基础,Chiplet 方案大概率会采用先进封装,推动先进封装 发展。Chiplet 具有成本低、周期短、良率高等优点,其核心是实现芯片间的高速互联, 且兼顾多种芯片互联后的重新布线,为实现既定性能,对 Chiplet 之间的布线密度、信 号传输质量提出较高要求,封装加工精度与难度进一步加大,并且要考虑散热和功率分配等问题。因此,Chiplet 技术因此需要高密度、大带宽的先进封装技术提供硬件支持, 大概率采用先进封装方案,如 SiP(系统级封装技术)、RDL(晶圆重布线技术)、Bumping (晶圆凸点工艺)、Fan-in/out(扇入/扇出式封装)等。

Chiplet 提升半导体测试需求,利好下游封测厂商、半导体独立测试厂商和测试设备供 应商。Chiplet 通过将多个裸芯(die)进行堆叠合封的先进封装,通常使用较为复杂的 芯片。由于在 Chiplet 中封装了多个 die,为确保正常运行,需要对 Chiplet 进行全检, 以确保每一个裸芯片都能正常工作,此外需通过边界扫描(Boundary Scan)测试,才能 确保多个裸芯(die)互联的可靠性。

中芯国际在其 2020 年的技术发展性报告中说道:以 Chiplet 技术生产芯片的可测试性是一个挑战,特别是一旦这些小系统被封装在一起, 只有数量较少的测试引线可以延伸到封装外;因此,测试必须分阶段进行,先测试单个 的芯片,然后测试封装后的完整系统。由此可见,Chiplet 既要对每一个裸芯片进行测 试,也要对裸芯片下的互联进行测试,因此会增大对半导体封测、半导体封测设备的需 求。并对测试设备的数量和性能都提出更高要求,利好封测企业、半导体独立测试厂商与半导体测试设备供应商。

全球、国内大厂积极布局 Chiplet 先进封装,共同推动封测产业发展。Chiplet 优势显 著,提高对先进封装与测试需求,国内及全球 OSAT 厂、晶圆代工大厂积极布局支持 Chiplet 方案的先进封装,目前已取得初步成果。国内方面,长电科技 XDFOI 平台以 2.5D 无 TSV 为基本技术平台,并于 2023 年 1 月宣布,XDFOI Chiplet 高密度度多维异构集成 系列工艺已按计划进入稳定量产阶段,基于利用有机重布线堆叠中介层可实现 2D/2.5D/3D 集成,并已实现国际客户 4nm 多芯片系统集成封装产品出货;

通富微电与 AMD 合作紧密,利用次微米级硅中介层以 TSV 将多芯片整合于单一封装,已实现 7nm 量 产,5nm 有望于 22H2 实现小规模试产;华天科技于 3 月 28 日晚间公告,公司全资子公 司华天江苏拟投资 28.58 亿元,进行“高密度高可靠性先进封测研发及产业化”项目的 建设。项目建成投产后形成 Bumping84 万片、WLCSP48 万片、超高密度扇出 UHDFO 2.6 万片的晶圆级集成电路年封测能力。

资料来源:观研天下,东莞证券研究所

2.2、IC载板是先进封装的关键材料,国产替代前景广阔

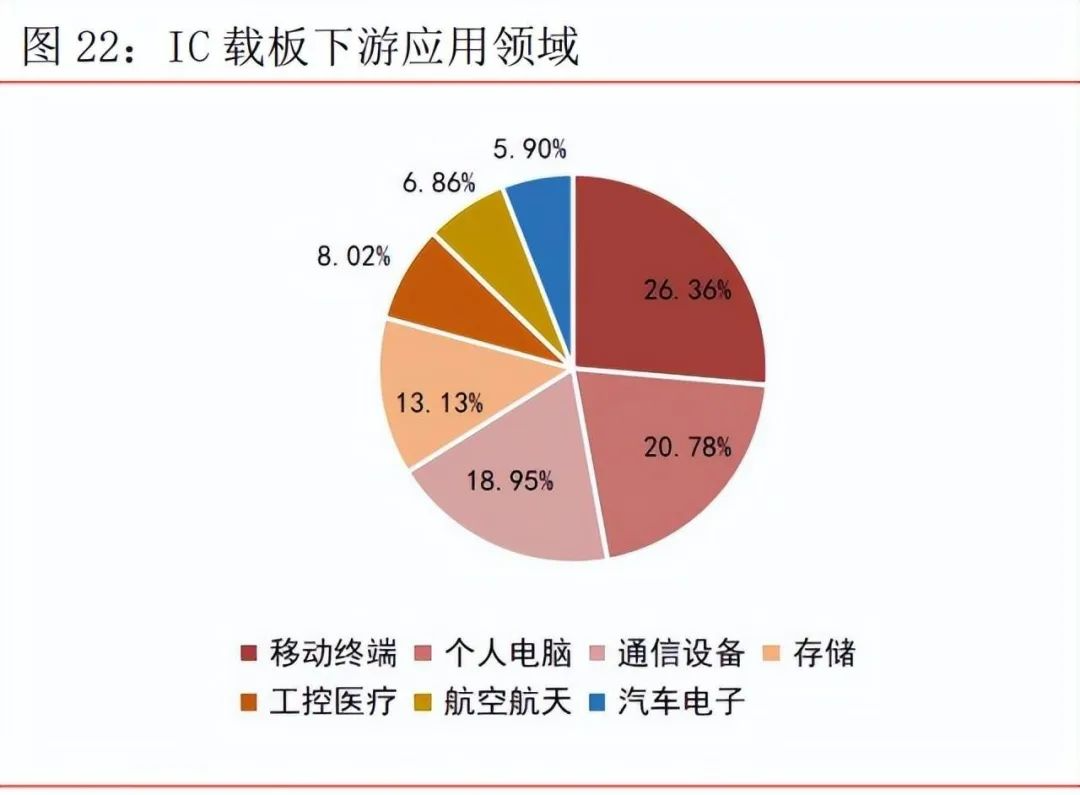

IC 载板是先进封装的关键材料,下游应用广泛。IC 封装基板(IC Package Substrate, 又称 IC 载板)是先进封装所采用的一种关键专用基础材料,它用于建立 IC 与 PCB 之间 的信号连接,此外还起到保护、支撑、散热以及形成标准化的安装尺寸的作用。IC 载板 作为一种高端 PCB 板,具有高密度、高精度、小型化和轻薄化的特点,广泛应用于移动 终端、通信设备、服务/储存等下游应用领域。

价值占比:IC 载板为半导体封装中价值量占比最大的耗材。半导体封装中所用耗材种类 较多,包括封装基板、引线框架、键合线、封装树脂、陶瓷封装和芯片粘接等,其中封 装基板占比最高,价价值占比接近一半,连接线/键合线、引线框架、封装树脂和其他 材料占比分别为 46%、13%、10%和 15%。IC 载板行业壁垒高于普通 PCB 产品。

IC 载板具有高精度、高密度、高性能、小型化及轻薄化等特点,在各种技术参数上要求较高,尤其是最核心的线宽/线距参数要远小于 其他种类 PCB 产品,因此具有较高的技术门槛;资金投入方面,相较其他 PCB 品类,IC 载板产线在投产前研发投入巨大且用时良久,在产线建设、后续运营等方面也需要巨大 资金持续投入,尤其是需要巨额的设备采购支出;客户壁垒方面,IC 载板客户认证体系 较普通 PCB 产品更严格,业内通常采用合格供应商认证制度,认证过程复杂且周期较长, 由此可见,相比其他 PCB 品类,IC 载板具有更高的技术门槛、资金壁垒和客户认证壁垒。

ABF/BT 载板原材料被海外企业垄断,原料供应瓶颈制约行业产能扩张。按照封装材料不 同,IC 载板可分为硬质基板、柔性基板和 IC 载板,硬质基板又可进一步分为 BT、ABF 和 MIS 载板。目前 ABF 载板与 BT 载板生产所需的重要原材料——ABF/BT 有机树脂被日 本头部企业垄断,原材料供给较为紧缺。主要原材料的供应短板也制约了行业产能扩张, 预计行业供不应求局面有望持续较长时间。

资料来源:Omdia,东莞证券研究所

行业竞争格局:日、韩、台份额绝对领先,大陆企业占比较低。从 IC 载板发展过程看, 行业基本遵循“日本-韩国-中国台湾-中国大陆”的产业转移路径。目前全球 IC 载板产 能集中在东亚地区,但由于我国在该领域起步较晚,目前日、韩、台企业仍占据行业主 导地位,在技术储备、产能规模、收入与利润等方面全方位领先大陆厂商。

据 Prismark 统计,全球 IC 载板前三大企业分别为台湾欣兴电子、日本揖斐电和韩国三星电机,行 业市场份额高度集中,前十大厂商份额占比超过 80%。虽然大陆企业起步时间晚,且面 临较高的行业壁垒,但受益于本土巨大的市场空间、产业配套和成本优势,叠加近年来 全球半导体封测产业逐渐向中国大陆转移,有望直接拉动封装材料需求。日益旺盛的下 游需求和稀缺的产能供给之间已形成较大缺口,本土以兴森、深南为代表去企业积推动 封装基板扩产,以满足下游客户需求。

先进封装拉动 IC 载板需求增长。IC 载板在高端封装领域已取代传统引线框架,成为封 装过程中的必备材料。先进封装增加 IC 载板的层数,有效拉动行业增长,而 Chiplet 封装技术也大大增加了 ABF 载板的需求面积,带动 ABF 载板需求提升。据 Prismark 统 计,,2021 年全球 IC 封装基板行业规模达到 142 亿美元,同比增长近 40%,预计 2026 年将达到 214 亿美元(约 1474 亿元),2021-2026 年 IC 载板 CAGR 为 8.6%。国内方面, 预计 2025 年国内 IC 载板市场规模将达到 412.4 亿元,占全球比重接近 30%。

2.3、Chiplet采用新型的IP复用模式,为半导体IP发展提供新机遇

半导体 IP 指预先设计好的功能模块。半导体 IP 是指集成电路设计中预先设计、验证好 的功能模块,它位于 IC 设计上游,提供 SoC 所需的核心功能模块。在芯片设计的过程 中,通过结合使用 EDA 软件和半导体 IP,能有效缩短的设计周期,降低开发成本。目前 大部分芯片厂商采用外购+自主设计部分 IP 相结合的生产模式,并结合外购 EDA 工具进 行独立芯片设计,因此 fabless 企业与 IDM 企业为半导体 IP 厂商的主要下游客户。

半导体 IP 在 IC 设计中起到不可或缺的作用。半导体 IP 具有性能高、功耗优、成本适 中、技术密集度高、知识产权集中、商业价值昂贵等特征,是集成电路设计产业的核心 产业要素和竞争力体现。随着芯片种类愈加丰富与先进制程不断推进,集成电路的设计 流程愈发复杂,导致研发费用加大,半导体 IP 为简化 IC 设计流程提供便利,配合先进 的 EDA 工具,IC 设计借助半导体 IP 实现了极大的便利。

资料来源:IBS,芯原股份招股说明书,东莞证券研究所

Chiplet 开启新型 IP 复用模式,为半导体 IP 发展提供机遇。Chiplet 采取搭积木的方 式,通过 3D 集成等先进集成技术将特定功能的芯片裸片集成在一起,从而形成一个系 统芯片。Chiplet 开启了 IP 复用新模式,即硅片级别的 IP 复用;不同功能的 IP,如 CPU、 存储器、模拟接口等,可灵活选择不同的工艺分别进行生产,从而可以灵活平衡计算性 能与成本,实现功能模块的最优配置而不必受限于晶圆厂工艺;Chiplet 的发展演进, 为 IP 供应商,尤其是具有芯片设计能力的 IP 供应商,拓展了商业灵活性和发展空间。目前 chiplet 已有少量商业应用,并吸引英特尔和 AMD 等国际芯片厂商投入相关研发, 在当前 SOC 早于工艺节点和成本瓶颈的情况下有望发展成为一种新的芯片生态。

单个芯片可集成 IP 数量增加,半导体 IP 市场有望实现快速增长。随着先进制程的演进, 线宽的缩小使得芯片中晶体管数量大幅提升,使得单颗芯片中可集成的 IP 数量也大幅 增加。以 28nm 工艺节点为例,单颗芯片中已可集成的 IP 数量为 87 个,当工艺节点演 进至 7nm 时,可集成的 IP 数量达到 178 个。单颗芯片可集成 IP 数量增多为更多 IP 在 SoC 中实现可复用提供新的空间,从而推动半导体 IP 市场进一步发展。据 IBS 数据显示, 导体 IP 市场将从 2018 年的 46 亿美元增长至 2027 年的 101 亿美元,年均复合增长率为 9.13%。其中处理器 IP 市场预计在 2027 年达到 62.55 亿美元,2018 年为 26.20 亿美元, 年均复合增长率为 10.15%;数模混合 IP 市场预计在 2027 年达到 13.32 亿美元,2018 年为 7.25 亿美元,年均复合增长率为 6.99%;射频 IP 市场预计在 2027 年达到 11.24 亿美元,2018 年为 5.42 亿美元,年均复合增长率为 8.44%。

芯原股份为国内半导体 IP 佼佼者,助力 Chiplet 技术发展。芯原股份为国内半导体 IP 龙企业,主营业务包括一站式芯片定制服务与半导体 IP 授权服务,已向市场推出多款 一站式芯片定制方案,致力于打造芯片一体化设计平台。公司在 IP 技术储备深厚,已 加入 UCle 联盟并推出高端应用处理器平台,积极推动 Chiplet 相关技术发展,加快 Chiplet 产业化落地。。2022 年,公司实现营收 26.79 亿元,同比增长 25.23%,实现归 母净利润 7,381.48 万元,同比增长 455.31%。在全球半导体景气下行的大背景下,得益 于公司无产品库存风险、无应用领域边界的独特商业模式,以及逆产业周期的属性,报 告期内公司业务实现快速发展,行业地位和市场竞争力不断提升。

审核编辑 :李倩

-

半导体

+关注

关注

339文章

31248浏览量

266610 -

封装

+关注

关注

128文章

9333浏览量

149053 -

chiplet

+关注

关注

6文章

499浏览量

13650

原文标题:2、Chiplet技术持续推进,先进封装、IC载板、半导体IP等多环节受益

文章出处:【微信号:CADCAM_beijing,微信公众号:智能制造IMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AI时代算力瓶颈如何破?先进封装成半导体行业竞争新高地

北大团队最新研究:AI芯片算力提升数倍,能效提升超90倍

奇异摩尔入选2025年度上海算力产业十大经典案例

沁恒网络芯片,自研技术解锁集成度与灵活性

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

后摩尔时代破局者:物元半导体领航中国3D集成制造产业

后摩尔时代:芯片不是越来越凉,而是越来越烫

Chiplet为后摩尔时代提升芯片算力与集成度的重要途径

Chiplet为后摩尔时代提升芯片算力与集成度的重要途径

评论