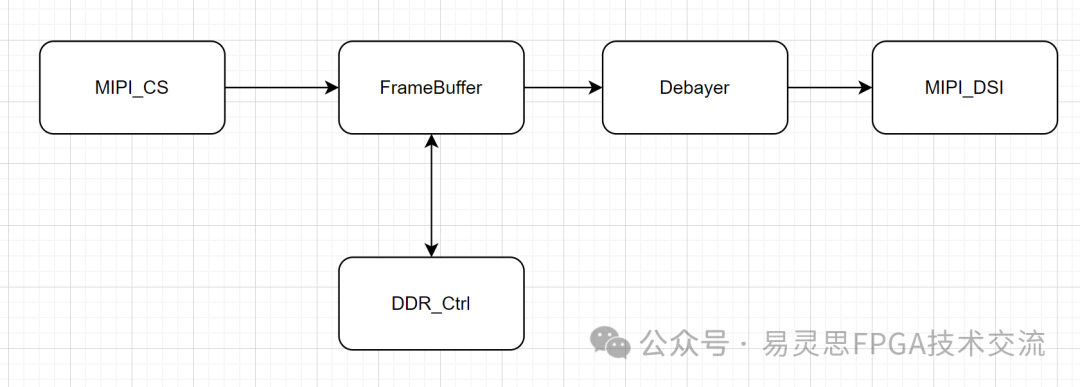

最近陆续有客户在评估易灵思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一个简单的移植来试验下MIPI DSI 驱屏。

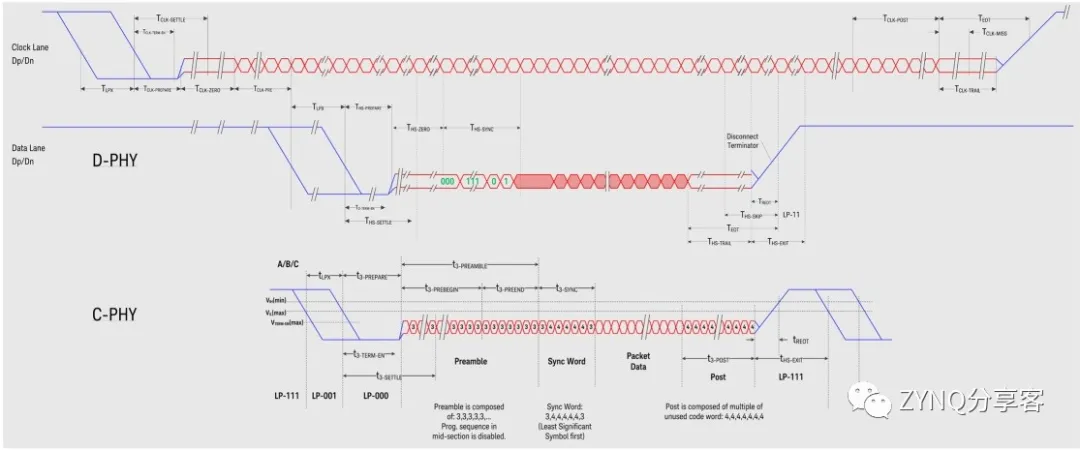

MIPI 2.5G DPHY简介

Ti180有4组MIPI 2.5G DPHY,每组是4组数据和一个时钟。

支持MIPI DPHY1.2版本协议

支持ULPS.

支持连续与非连续时钟模式。

支持反向传输。

MIPI TX 参考时钟来源?

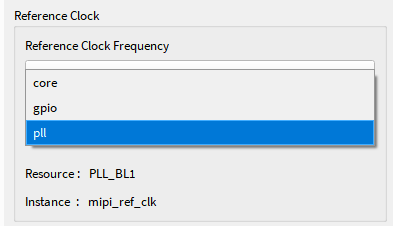

MIPI TX的参考有GPIO,PLL输出和core三个来源。

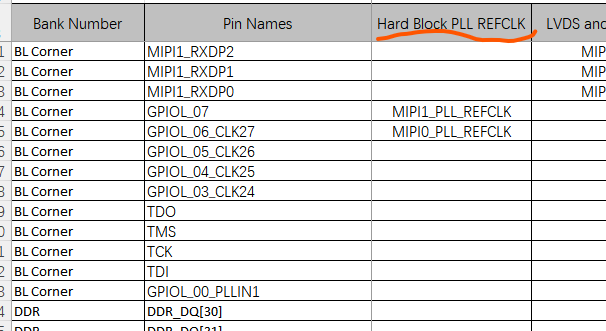

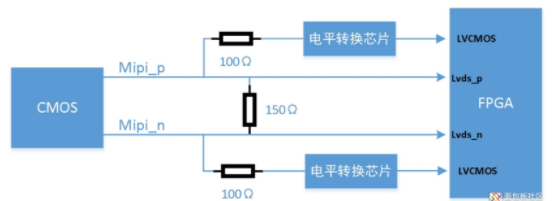

(1)如果是GPIO 输入,请参考pinout设计文件里有一栏Hard Block PLL REFCLK.就是指如果硬件如果参考时钟从外部供给时指定的管脚。这是在硬件设计时需要注意的,需要提前规划好时钟的来源。

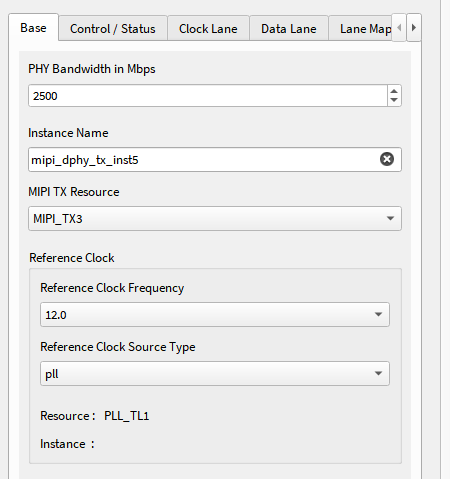

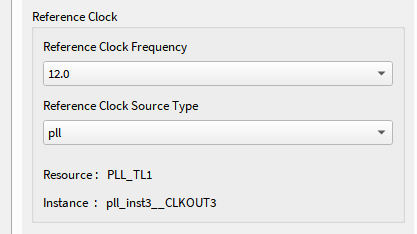

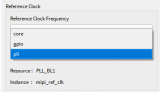

(2)如果把时钟参考设置为PLL又应该怎么使用,明显IP核上并没有给出任何设置PLL参考源的选项。PLL的参考只能是固定的。当我们选择PLL的时候,下图的Resource会指定需要用那个PLL,如下图的PLL_TL1,这时我们就必须要使用PLL_TL1,但是选择的是PLL_TL1的输出的那个时钟呢?在下图的Instance后面还是空白的。

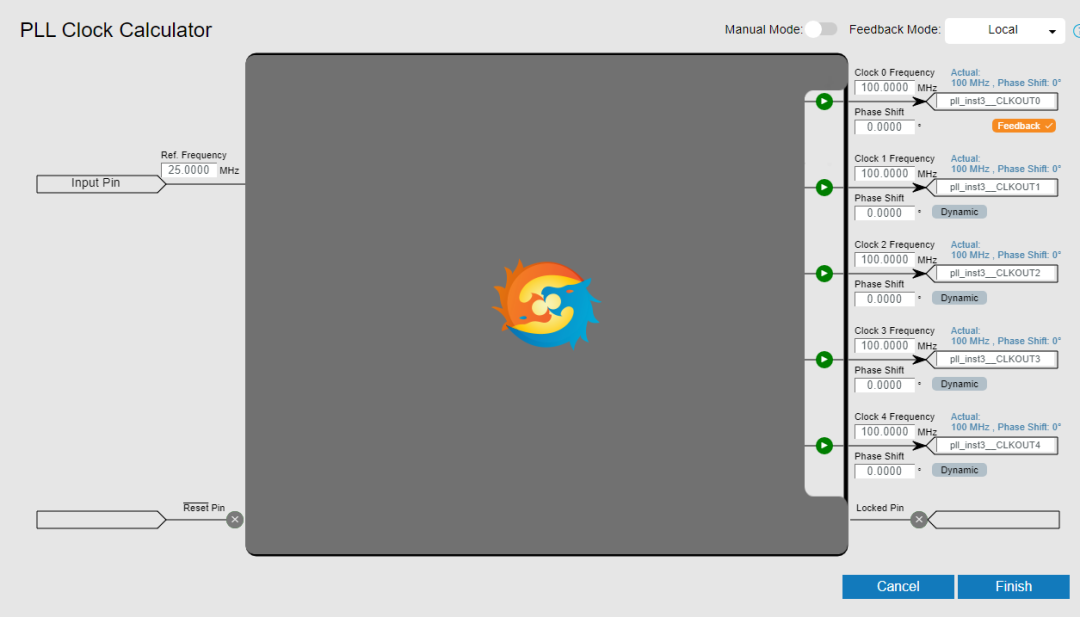

于是我们新建一个PLL_TL1,并把所有的输出时钟都打开。

当我们再次查看DPHY的参考时,发现Instance已经不再为空,为是指定了pll_inst__CLKOUT3.说明用的是PLL_TL1的clk_out3,所以在设计时也要注意对该时钟的规划。

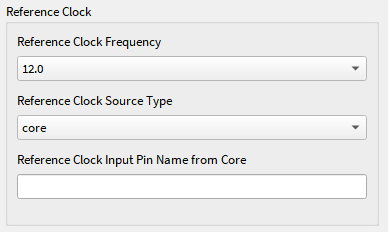

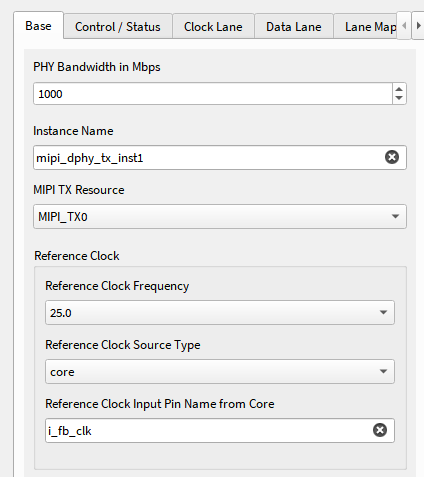

(3)如果时钟选择Core呢?这时时钟可以手动输入想选择的时钟,无论是从GCLK输入的还是PLL输出的。

另外需要提醒要注意时钟频率的选择哦。

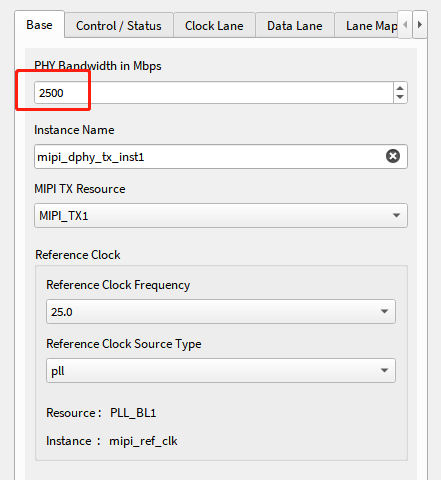

如果要修改速率DPHY部分应该做什么呢?

(1)修改PHY Bandwidth参数。

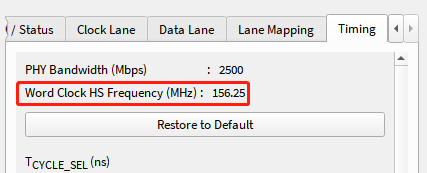

(2)在Timing中也可以确认

(2)修改clk_byte_HS ,该时钟要求为phy_clk_byte_HS的两倍。

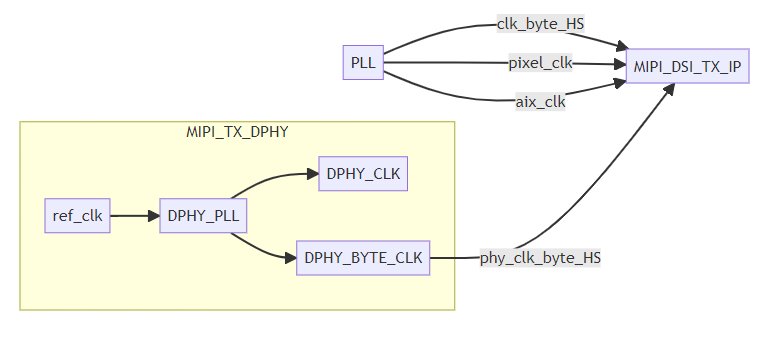

时钟方案

该demo中MIPI DSI TX的IP部分时钟主要如下,

(1)在DPHY中会生成一个phy_clk_byte_HS给DSI TX IP。

(2)同时还会通过PLL输出一个clk_byte_HS 给DSI TX IP,该时钟要求是phy_clk_HS的两倍,demo上这两个时钟并不同源。

(3)另外PLL还提供了MIPI TX IP需要的pixel_clk和axi_clk。

移植说明:

该demo是MIPI DPHY 4lane 1G输出。内部产生了一个彩条。

(1)MIPI屏速率是1Gbps4 lane.

(2)分辨率是1920x1080

(3) demo来自易灵思提供的DSI TX demo。

(4)目前demo板没有预留MIPI的GPIO参考,为了方便就直接通过Core时钟来驱动(PLL输入还是要指定位置的),实际这个时钟也是从PLL输出的。

(5)屏使用的是易灵demo板中提供的手机屏。

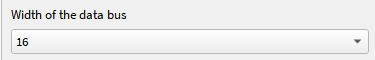

(3)目前MIPI DSI TX IP里面有两个参数,clk_byte_HS和phy_clk_byte_HS,而且文档明确说明clk_byte_HS是phy_clk_byte_HS的2倍。如果在DPHY中把数据总线位宽修改成16位,还必须是2倍关系吗?

.clk_byte_HS (dphy_byte_clk ), .clk_pixel(i_sysclk), .phy_clk_byte_HS(mipi_dphy_tx_pclk),

注意:

(1)如果使用易灵思原厂提供的demo板评估,要连接R171,这个是LCD屏的复位信号 。

(2)屏的参数与IP的参数目前共用。

审核编辑:汤梓红

-

pll

+关注

关注

6文章

976浏览量

137592 -

移植

+关注

关注

1文章

407浏览量

29215 -

时钟

+关注

关注

11文章

1953浏览量

134548 -

MIPI

+关注

关注

11文章

346浏览量

50701 -

GPIO

+关注

关注

16文章

1313浏览量

55730

原文标题:MIPI2.5G DPHY TX demo移植 -v1

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于Xilinx FPGA实现MIPI DPHY接口案例分析

1.5G MIPI dsi TX移植注意事项及demo - update8

MIPI2.5G DPHY CSI2DSI demo移植 -v1

Gowin MIPI DPHY RX TX用户使用指南

请问RK3568 MIPI RX DPHY接收MIPI协议的是否同时支持CSI与DSI两种协议?

SN75DPHY440SS MIPI® CSI-2/DSI DPHY 重定时器

为何要选择比DPHY复杂多的物理层CPHY呢?

MIPI dsi TX移植注意事项

详解Object Detection Demo的移植

基于高云Arora-V 60K FPGA实现的MIPI CPHY转MIPI DPHY透传模块

MIPI2.5G DPHY TX demo移植教程

MIPI2.5G DPHY TX demo移植教程

评论