车辆在动态称重时,作用在平台上的力除真实轴重外,还有许多因素产生的干扰力,如:车速、车辆自身谐振、路面激励、轮胎驱动力等,给动态称重实现高 测量造成很大困难。若在消除干扰的过程中采用模拟方法滤波,参数则不能过大,否则将产生过大的延迟导致不能实现实时处理,从而造成滤波后的信号仍然含有相当一部分的噪声。所以必须采用数字滤波消除干扰。

FIR滤波的原理及实现

本文采用FIR数字滤波,其原理如公式1所示。

Y(n)=(1)

其中h(k)为系统滤波参数,x(n)为采集的信号,Y(n)为滤波后的输出信号。

FIR滤波器的h(n)0≤n≤N-1

H(z)=(2)

在本文中N=17。由于h(n)具有对称性质,即:

h(n)=h(N-1-n)(n=0,1,。..,(N-1)/2)(3)

这样就可以把FIR滤波器设计成具有线性相位。利用这一情况,可以得到的乘法结构,需要(N+1)/2次乘法,仅是级联或并联结构所需次数的一半,因此,实际应用中多采用此方法。

我们选用17点的FIR滤波算法,这样实现 FIR卷积运算需要执行9次乘法和16次加法。为了实现数据的实时处理,需要在20ms内完成这个卷积运算,如果选用单片机89C51(12M晶振)则无法实现。所以我们选用了Altera公司的FLEX10K20。FLEX10K系列是工业界 个嵌入式的PLD,采用重复可构造的CMOSSRAM工艺,把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能。具有高密度、低成本、低功率等特点。

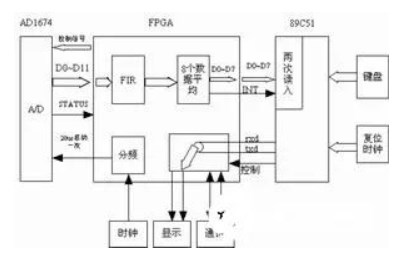

图1硬件结构框图硬件设计

由于我们选用的AD1674芯片转换时间为10ms,而所设计的电路每隔20ms启动转换 ,所以有足够的时间完成模数转换。轴重台的宽度为40cm,汽车通过轴重台的 速度为15km/h,通过计算可知在这段时间里系统可采集4800个数据。由于前30ms是传感器的反应时间,将剩下的数据进行FIR数字滤波后,噪声会被有效的抑制。为了进一步平滑波形,对每8个数据做 平均,这样就消弱了由于汽车高速通过轴重台时由于颠簸产生的尖峰信号。FPGA的每次滤波包含有FIR运算和8个数据的平均值运算,完成 滤波就会向单片机发一个中断请求,此时单片机读取滤波后的数据。由于我们选用的A/D转换器是12位,而单片机89C51是8位的,所以经过处理后的数据必须分两次读入。 次读入低8位,第二次读入高4位,然后对数据处理。此时我们可以认为单片机接收的数据为滤波后不含有噪声的数据。根据轴重称量的波形图可以知道,只要求出此时的 值就是汽车的真实重量。

在此仪表中,串行口即用来显示也用来通讯,我们可以通过FPGA很容易实现切换。如图1所示,当控制信号为1的时候RXD、TXD用于显示,而当控制信号为0的时候用于和上位机通讯。

我们选用加海明窗的理想低通滤波器,其归一化截至频率为0.25,如图2所示。汽车称重信号为含有多种成分噪声的直流信号如图3所示,这1000个数据经过FPGA的FIR滤波和8点数据平均后,提供给单片机125个数据

滤波之前的噪声的峰峰值在0.1V左右,而此时的轴重信号为1,这将严重影响测量 。滤波后我们看到情况得到了明显的改善,噪声信号的峰峰值被抑制在0.02V的范围内,大大改善了信噪比,从而提高了测量 。

结语

本设计不但实现了硬件数字滤波电路,而且减少了许多门电路和组合逻辑电路。用比较少的器件实现了比较复杂的功能,减少了故障率。用此方法设计的汽车动态称重仪表具有良好的实时性和较高的 ,现已投入批量生产。

审核编辑:刘清

-

FPGA

+关注

关注

1655文章

22283浏览量

630290 -

滤波电路

+关注

关注

47文章

654浏览量

71399 -

数字滤波电路

+关注

关注

0文章

2浏览量

5708 -

FIR滤波

+关注

关注

0文章

6浏览量

10050 -

AD1674

+关注

关注

0文章

12浏览量

20870

原文标题:基于FPGA实现FIR数字滤波电路的设计及应用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用FPGA构建的数字滤波器设计方案

基于FPGA实现FIR数字滤波电路的设计及应用

基于DSP的FIR 数字滤波器设计

基于FPGA的FIR滤波器设计与实现

基于FPGA的FIR数字滤波器该怎么设计?

基于FPGA的FIR数字滤波器的优化设计

FPGA是如何设计并实现了32阶FIR数字滤波器的硬件电路?

FIR数字滤波器设计

基于FPGA实现FIR数字滤波器

基于FPGA实现FIR数字滤波电路的设计及应用

基于FPGA实现FIR数字滤波电路的设计及应用

评论