引言

低温蚀刻在低温下去除高纵横比器件中的材料,尽管它一直是一个具有挑战性的过程。低温蚀刻难以控制,并且需要在晶圆厂中使用专门的低温气体,这很昂贵。(江苏英思特半导体科技有限公司)

低温蚀刻开发于 1980 年代,有一些优点,但它主要用于 MEMS 和其他设备的研发,而不是生产。该行业实际上并不销售低温蚀刻系统。但多年来,一些工具供应商销售了具有低温功能的蚀刻工具。纯粹主义者认为,在负 100°C(负 148°F)或更低温度下进行的蚀刻构成低温蚀刻。(江苏英思特半导体科技有限公司)

低温蚀刻,有时称为低温蚀刻,是在设备中实现深硅或高纵横比 (HAR) 蚀刻的两种方法之一,其中的特征是长、窄和深。另一种也是最流行的方法是两步博世工艺,您可以蚀刻掉结构的一部分,然后在环境温度下对其进行钝化。然后重复该过程,直到蚀刻完成。(江苏英思特半导体科技有限公司)

图 1:高纵横比的低温蚀刻

什么是蚀刻?

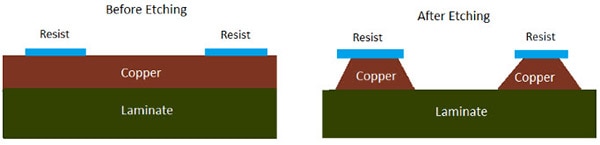

蚀刻是从晶圆上蚀刻或去除材料以创建设备特征的工艺步骤,分为湿法和干法两类。湿法蚀刻使用液体化学品去除材料。通常,低温蚀刻、原子层蚀刻和其他类型属于此类。然而,低温蚀刻不同于ALE。正在投入生产的 ALE 可以在原子尺度上选择性地去除目标材料。(江苏英思特半导体科技有限公司)

然而,在许多干法蚀刻系统中,晶圆位于蚀刻系统的反应器中,等离子体用作来源。系统中引入气体,等离子体分解气体,产生离子和反应性中性物质。然后,离子和物质轰击晶圆的选定部分,从而去除器件中的材料。(江苏英思特半导体科技有限公司)

等离子蚀刻系统配置有几种类型的反应器之一,例如电容耦合等离子体 (CCP) 和电感耦合等离子体 (ICP) 等。基于 CCP 等离子源的蚀刻机由一个反应器和两个金属电极组成。晶圆位于两个电极之间的平台上。使用射频电源,在电极之间产生电场,从而释放离子。在工厂中,最先进的蚀刻机是基于 ICP 的。这些蚀刻机类似于 CCP 系统,但 ICP 源通过电磁感应产生能量。

冻结的内存和逻辑

然而,现在低温蚀刻正从实验室逐渐接近晶圆厂。该技术正在针对 3D NAND进行评估。与今天的2D结构平面NAND不同,3D NAND类似于垂直摩天大楼,其中存储单元的水平层堆叠,然后使用微小的垂直通道连接。3D NAND 通过器件中堆叠的层数来量化。随着添加更多层,位密度增加。

如今,3D NAND 供应商正在出货64层设备,96层产品也在不断增加。在幕后,供应商正在开发128层和256层产品。3D NAND 流程从衬底开始。然后,使用化学气相沉积,在基板上沉积一层材料,然后在顶部沉积另一层。该过程重复几次,直到给定的设备具有所需的层数。(江苏英思特半导体科技有限公司)

然后是流程中最困难的部分——HAR蚀刻。为此,蚀刻工具必须从器件堆叠的顶部钻出微小的圆形通道到底部基板。此步骤使用RIE蚀刻机执行。蚀刻机通过用离子轰击表面来创建微小的通道。但随着蚀刻工艺深入通道,离子数量可能会减少。这减慢了蚀刻速率。更糟糕的是,可能会出现不需要的 CD 变化。理论上,对于这种应用,低温蚀刻机将在低温下钻出微小的孔。这使得侧壁在蚀刻过程中保持低温,从而允许离子在不中断的情况下进一步向下移动孔。

审核编辑 黄宇

-

半导体

+关注

关注

336文章

29977浏览量

258110 -

晶圆

+关注

关注

53文章

5344浏览量

131679 -

蚀刻

+关注

关注

10文章

428浏览量

16463

发布评论请先 登录

时序约束问题的解决办法

晶圆蚀刻扩散工艺流程

晶圆蚀刻后的清洗方法有哪些

电子电路百科全书

什么是高选择性蚀刻

想做好 PCB 板蚀刻?先搞懂这些影响因素

ADS1118低温下出现异常的原因?

耐低温铠装网线有哪些

深入探讨 PCB 制造技术:化学蚀刻

导电线路修补福音:低温烧结银浆AS9120P,低温快速固化低阻值

蚀刻基础知识

低温蚀刻重新出现_

低温蚀刻重新出现_

评论