摘要: 现代信号处理系统通常需要在不同处理器之间实现高速数据通信,SRIO协议由于高效率、低延时的特性被广泛使用。本文研究了在FPGA和DSP两种处理器之间实现SRIO协议的方法,并通过电路设计和利用处理器的开发工具编程实现了两种处理器间的高速通信。经测试,该系统具有较高的传输效率。

引言

随着高性能信号处理系统对运算速度、通信速率等要求的不断提高,单独的处理器(如FPGA或DSP)无法满足高速实时信号处理的需求。TI公司的多核DSP处理性能强大,但是并行性不强,难以适应计算异常密集的应用,另外集成性的DSP接口也影响了数据传输的灵活性;FPGA具有极强的并行性,适合密集计算应用,而且可配置I/O和IP核支持多种数据传输接口,但FPGA的内部逻辑资源和存储资源有限,并且开发难度大,实现复杂算法也比较困难。

因此,结合多核DSP和FPGA的优势,构建基于异构处理器的信号处理系统成为当前一种发展趋势。异构处理器间的高速通信成为高速信号处理系统的关键问题之一,本文基于SRIO协议设计和实现了DSP与FPGA之间的高速数据通信。

异构处理器电路

1.1DSP处理器

在处理器领域,多核DSP在处理性能、功耗和面积上都有很大优势,得到了广泛应用。TI公司的8核处理器TMS320C6678,基于KeyStone多核结构,具有高性能的浮点、定点计算能力,单核具有1 GHz的主频,运算速度可达320 GMACS/160 GFLOPS。该DSP采用同构多核架构,每个核可以独立地执行不同的计算任务,具有512 KB的私有内存。芯片具有4 MB共享内存供8个核心访问,而且具有SRIO、PCIe等多种接口,能够满足各种数据传输的需求。

1.2FPGA处理器

FPGA因其功能强大、接口灵活,成为当前的主流处理器之一,FPGA与DSP芯片有机结合不仅能够高效地实现复杂算法,而且还可以提高系统数据传输的效率和结构的灵活性。Xilinx公司Virtex6 LXT系列FPGA芯片XC6VLX550T,是一款具有高级串行数据传输功能的高性能逻辑器件,基于硬件GTX串行收发器,可以实现多种高速数据传输接口。采用SRIO IP核可以实现FPGA和DSP之间的SRIO协议通信。

1.3异构处理器电路互连

RapidIO[3]协议是一个开放的点对点分组交换标准,是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的互连技术。串行RapidIO[4](SRIO)是采用串行差分模拟信号传输的RapidIO协议,基于SerDes(Serialize Deserialize)技术,采用差分交流耦合信号(具有抗干扰能力强、速率高、传输距离较远等优点),所以SRIO是一个针对嵌入式系统应用的高性能、低引脚数的高速互连接口。

SRIO协议分为3层:逻辑层、传输层和物理层。逻辑层定义了操作协议;传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。SRIO是基于包交换的高速互连技术,其数据包是由包头、有效的数据载荷和16位CRC校验组成。包头的长度根据包类型不同,可能为十几到二十几个字节,最大的有效载荷长度为256字节。由于包长度短,所以传输延时较小,硬件上也易于实现,适合数字信号处理场合对传输延时要求较高的应用。

TMS320C6678集成了支持SRIOv2.1通信协议的4通道SRIO接口,可以实现每条通路1.25 Gbps、2.5 Gbps、3.125 Gbps、5 Gbps的通信速率。XC6VLX550T的GTX模块嵌入Serial RapidIO IP核,可支持线速率为1.25 Gbps,2.5 Gbps~3.125 Gbps,因此可实现异构处理器DSP与FPGA之间的SRIO高速串行通信。

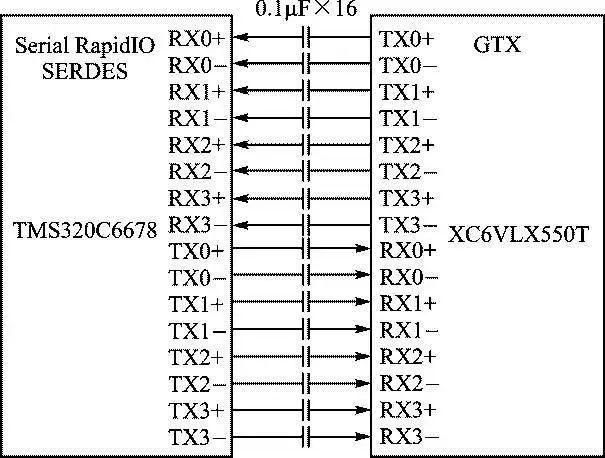

为了最大程度地体现RapidIO串行接口的性能,本设计中采用3.125 Gbps的线速率,处理器之间采用4xSRIO连接方式, 1个1x接口即是一个差分对的一对读/写信号,一个4x接口即4个此类差分对的结合,因此采用4x SRIO连接可实现最高12.5 Gbps的数据传输速率。电路连接方式如图1所示,只需要将DSP的TX、RX端口与FPGA的RX、TX端口对应相接,由于SRIO采用差分线对实现数据传输,所以需要在异构处理器的RX端口的差分线上串联一个0.1 μF的电容,做交流耦合使用。

图1 异构处理器连接方式

SRIO设计

DSP和FPGA作为SRIO连接的端点器件,两者可互为从属[5]。主设备需要管理通信的发起、配置、结束等一系列过程,从设备只需要被动地响应通信。基于DSP的编程比FPGA简便,为了降低开发难度和工作量,采用DSP作为主设备,是通信的发起端;FPGA作为从设备,是通信的目的端。

2.1 DSP端的SRIO配置

DSP端SRIO的软件设计基于SYS/BIOS操作系统,使用TI公司提供的多核软件开发套件(MCSDK),主要组件是开发平台中的芯片支持库(CSL)工具。CSL是TI公司为其DSP产品提供的API函数,提供了一个用于配置和控制片上外设的C语言接口,在程序设计过程中利用CSL库函数可以方便地访问DSP的寄存器和硬件资源,提高DSP软件的开发效率和速度。

2.1.1 SRIO初始化

实现SRIO重要的一步是SRIO的初始化,一般分为以下几步:

① 打开SRIO的电源和时钟:为了降低功耗,默认状态下SRIO模块的电源和时钟是处于关闭状态的,因此 SRIO 初始化首先要调用CSL_SRIO_OPEN函数将SRIO模块的电源和时钟打开。

② 配置SRIO的串并转换器:将125 MHz的参考时钟通过串并转换器内部的锁相环倍频至1.25 GHz,串并转换器采用半速率时钟模式,利用这个时钟信号的上升沿和下降沿对4路8位数据分时移位输出,即每个时钟串并转换器的串行输出端将输出2位的数据,采用该模式降低了对时钟信号的要求,降低了电路设计难度。

③ 设置4x工作模式:C6678有4个SRIO端口,将4路串并转换器使能。定义SRIO通信链路端点器件的ID,C6678提供了8个LSU模块用于SRIO数据操作的处理,每组LSU都有7个32位寄存器,通过配置LSUx_reg4将源器件DSP的ID设为0x00,目的器件FPGA的ID设计为0xFF。

④ 等待SRIO初始化完成:通过配置SP_ERR_STAT寄存器,检测SRIO的端口状态是否OK,如果OK,则表示可以进行SRIO通信,否则提示初始化不成功或者其他情况导致不能通信。在SRIO初始化前需要FPGA端完成SRIO逻辑的配置,否则DSP在初始化SRIO期间无法和FPGA进行握手,会导致初始化失败。

2.1.2 SRIO的读写操作

SRIO初始化完成后,通过DSP对SRIO端口的读写操作实现和FPGA之间的数据传输。DSP读写支持的操作通过数据包格式中的Ftype和Ttype两个字段描述,I/O逻辑操作是简单实用的传输方式,使用该模式的前提是主设备要知道被访问端的存储器映射,可以直接读写从设备的存储器。I/O逻辑操作在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。表1所列为I/O操作的几种事务类型。本文使用的读操作事务是NREAD。在3种写操作事务中:NWRITE_R是带响应的写操作,效率较低;SWRITE要求数据载荷长度在8~256字节之间,且为8字节的整数倍。因此本文采用NWRITE写操作,配置简单且易于实现。

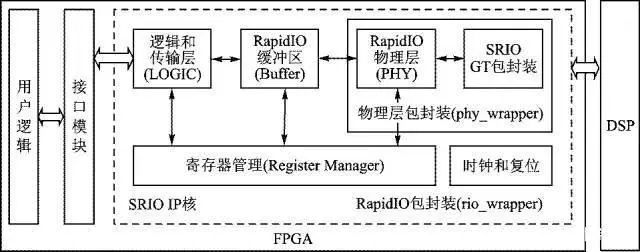

图2 FPGA端的SRIO实现结构

I/O逻辑操作使用了SRIO的功能模块LSU(Load Store Unit)和MAU(Memory Access Unit)。LSU实现I/O逻辑操作数据包的读写;MAU提取数据包中的源地址、目的地址、数据长度等信息,从而将数据包的有效数据载荷写入指定位置。DSP端SRIO的I/O逻辑操作可以分为4个部分:

① 锁定LSU寄存器:CSL_SRIO_IsLSUFull函数读取LSUx_reg6寄存器中的FULL位,为1,则LSU所有的影子寄存器已经写入配置文件等待数据发送,暂时没有可用的影子寄存器。

② 配置寄存器:配置LSU寄存器0~4,获取传输信息,包括源地址dspAddress、目的地址rapidIOLSB、数据长度bytecount等,程序使用的函数是CSL_SRIO_SetLSUTransfer。

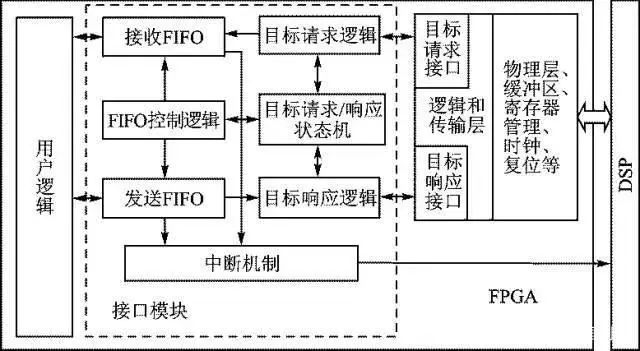

图3 RapidIO接口模块实现方案

③ 释放寄存器:完成锁定和配置LSU寄存器后,最后配置LSU寄存器5,确定数据包的事务类型,配置完成后通过CSL_SRIO_IsLSUBusy函数检测LSUx_reg6寄存器中的BUSY位。若BUSY为0,释放LSU控制权,该影子寄存器进入等待状态,最终将数据发送出去;若BUSY为1,则将数据存放在影子寄存器中,等待LSU完成当前传输至空闲再发送数据。

④ 等待传输完成:通过CSL_SRIO_GetLSUCompletionCode函数读取寄存器SRIO_LSU_STAT_REG的状态,判断是否所有数据均传输完毕。

2.1.3 通信流程

C6678使用中断控制器(INTC)管理和分配多个外部中断源,其中有来自FPGA的中断源。本文中SRIO工作于主模式状态,FPGA通过GPIO向DSP发送中断,当DSP接收到来自FPGA的中断后,对FPGA相应的内存区域进行读写操作。本设计中,中断使用了GPIO8和GPIO9两个中断触发事件,分别将其映射到DSP的CPU中断4和中断5。在此状态下程序主要执行两种操作:在 DSP 收到中断4以后进入中断4服务函数, 完成从FPGA端读取数据的操作;在收到中断5以后进入中断5 服务函数,完成将数据写入FPGA端的操作。

2.2 FPGA端的SRIO配置

FPGA端的SRIO基于Xilinx公司的Serial RapidIO IP核[6]来实现,IP核底层硬件基于FPGA的GTX收发器。图2所示为FPGA端的SRIO实现结构,SRIO IP核左侧通过接口模块与用户逻辑相连,右侧通过输出引脚与DSP相连。IP核可划分为5个部分:RapidIO逻辑和传输层(LOGIC)模块、 RapidIO物理层(PHY)模块、RapidIO缓冲区(Buffer)模块、寄存器管理(Register Manager)模块、参考时钟和复位模块。根据不同的需求,用户可以选择使用物理层包封装(phy_wrapper)或者RapidIO包封装(rio_wrapper),本文选择使用RapidIO包封装。

本文以IP核为基础,采用已有的整体框架,围绕目标用户接口设计接口模块。中断作为FPGA和DSP之间的握手信号,FIFO作为用户逻辑和IP核之间的数据缓冲接口。图3所示为Rapid IO接口模块实现方案。

由于FPGA在通信中作为从设备,因此接口模块中不再需要IP核接口中发起用户的功能,只保留目标用户的功能,其中目标请求/响应状态机控制各模块的时序变化。接口模块左侧与用户逻辑接口相连,右侧与IP核目标用户接口相连。

中断机制部分,向DSP发送数据时采用发送FIFO的半满标志作为读中断,从DSP接收数据时采用接收FIFO的半空标志作为写中断。发送FIFO中数据超过一定量时触发DSP读数据,接收FIFO中数据低于一定量时触发DSP写数据。用户及时有效地控制FIFO的状态,可以保证FIFO不会被写满或者被读空。用户也可以产生中断逻辑,控制DSP对FPGA内部存储空间进行读写。本文引入了中断机制和数据缓冲FIFO,利于接口对接和功能拓展,实现数据在不同芯片之间的高效传输。

传输性能测试

本文对DSP与FPGA之间的SRIO通信进行性能测试。DSP的工作频率为1 GHz,SRIO 接口工作速率设置为3.125 Gbps,经过物理层8B/10B编码,数据包的实际传输速率为2.5 Gbps,传输方式设置为4x 模式,则理论数据传输速率应为10 Gbps。由于数据包的打包和解包等操作,实际速率会小于理论值。

表2是使用NWRITE和NWREAD对不同数据包进行通信速度测试的结果。在传输数据为32 字节时,考虑到数据包操作时的开销,与理论值比率仅为1.1%,很大一部分时间被花费在数据包的打包和解包的处理中,随着传输数据量的增加,SRIO的实际传输效率不断增大,最终维持在7 800 Mbps。经过多次反复实验,该统计结果稳定可靠,并且没有出现丢包误码的情况。

结语

本文针对当今高速信号处理系统对芯片间数据传输的需求,研究异构处理器DSP和FPGA间的数据传输技术。DSP端基于CSL库实现了SRIO的主设备通信,FPGA端基于RocketIO IP实现了从设备通信,并采用中断实现异构处理器之间的握手信号,经测试达到较高的传输速率。本文研究内容也适用于同系列的其他处理器之间的数据通信,具有较高的应用价值。

扫描二维码获取

更多精彩

FPGA设计论坛

未来的高性能FPGA是否会优于GPU?

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

原文标题:在FPGA和DSP两种处理器之间实现SRIO协议的方法

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22503浏览量

639290

原文标题:在FPGA和DSP两种处理器之间实现SRIO协议的方法

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

别让协议成为渣抓取的绊脚石EtherNet/IP转Modbus RTU网关,一次握手,两种语言

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

MAX8620Y:便携式设备微处理器或DSP的理想µPMIC

使用TFTP实现IAP的方法

基于DSP与FPGA异构架构的高性能伺服控制系统设计

利用Verdi调试协处理器的实现步骤

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

在FPGA和DSP两种处理器之间实现SRIO协议的方法

在FPGA和DSP两种处理器之间实现SRIO协议的方法

评论