前言

数字经济已成为继农业经济、工业经济之后的主要经济形态。算力作为数字经济的核心生产力,将直接影响数字经济发展的速度,决定社会智能的发展高度。存算一体作为一种新型算力,有望解决传统冯·诺依曼架构下的“存储墙”、“功耗墙”问题。存算一体将存储与计算有机融合以其巨大的能效比提升潜力,有望成为数字经济时代的先进生产力。存算一体芯片设计迭代和投产的效率至关重要,如何能够设计出更低损耗、更低噪声、更低能耗,并符合信号完整性、电源完整性指标性能的存算一体芯片,从而提高存算一体芯片的设计效率呢?

存算一体芯片市场概况

据IDC预测,2025年全球物联网设备数将超过400亿台,产生数据量接近80ZB。在智慧城市、智能家居、自动驾驶等诸多场景中超过一半的数据需要依赖终端本地处理,单设备算力需求约在0.1~64TOPS之间,海量数据将在边缘侧进行处理,流量模型逐渐从云侧扩展到边侧。边缘计算场景下对单设备算力需求约在64~256TOPS之间,时延要求高。到2030年将带动智能算力需求增长500倍,以AI算力为核心的智算中心将成为算力基础设施主流,大规模的AI芯片集约化建设带来高功耗挑战,每机架平均功耗将由3~5kw逐渐升至7~10kW。未来智算中心呼唤新型AI芯片,以满足云侧大算力、高带宽、低功耗等特性。 与传统方案相比,存算一体在深度学习等领域有独特优势,可以提供比传统设备高几十倍的算效比。此外存算一体芯片通过架构创新可以提供综合性能全面的芯片及板卡,预计将在边侧推理场景中有着广泛的应用。存算一体可通过多核协同集成大算力芯片,结合可重构设计打造通用计算架构,存算一体作为智算中心下一代关键AI芯片技术,正面向大算力、通用性、高计算精度等方面持续演进,有望为智算中心提供绿色节能的大规模AI算力。

存算一体芯片设计中的挑战

1. 基于3DIC架构的三维堆叠芯片

电磁场求解挑战

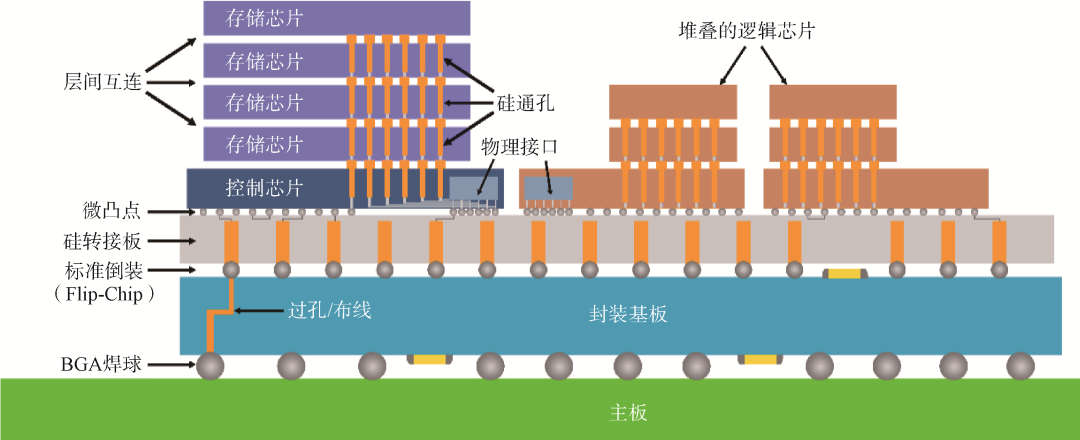

在存算一体芯片中,按照封装结构可以分为2D、2.5D 和3D。不通过额外中介层,直接在有机基板上互连芯片的形式称为2D 封装,该方案成本低,但互连线的密度不高,采用高速串行互连技术一定程度上可以弥补低带宽问题。台积电的CoWoS芯片(Chip on Wafer on Substrate, CoWoS)技术是典型的2.5D 封装技术,即通过硅转接板实现多颗芯片的互连和集成。3D封装是指两颗或多颗芯粒通过硅通孔、以面对背(Face-to-Back)的形式,或通过微凸点或混合键合技术、以面对面(Face-to-Face)的形式,在垂直方向直接堆叠,并实现芯粒间和对外界的信号连接的技术(图1)。目前主流的3D 封装技术主要包括台积电的系统整合芯片(System on Integrated Chip, SoIC)技术和英特尔的Foveros3D 封装技术等。3D 封装互连密度更高,距离更短,速度更快,但是成本更高且存在散热和应力等问题。

图 1

3DIC示意图

基于3D架构的存算一体芯片,通过混合键合(Hybrid Bonding)技术进行存储芯片和ASIC之间的高密度互连通信,Bump数量达到数千甚至数万、几十万的级别,Die内的RDL和Via数量更是庞大,整个结构的电磁场求解未知量规模是一般求解器难以进行计算的,如何对模型进行合理的堆叠,内部细节如何合理有效简化对仿真速率和求解精度将至关重要。

2. um尺寸级别下仿真精度挑战

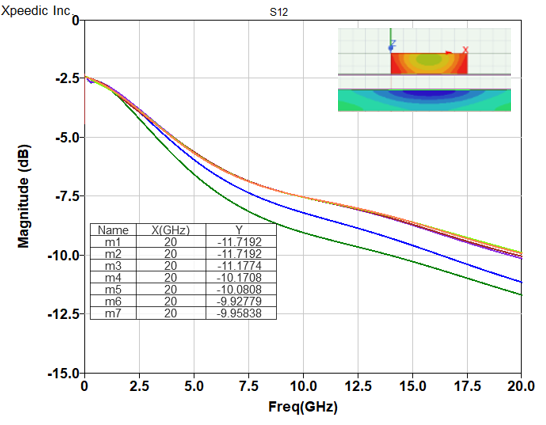

在2.5D/3D的存算一体芯片中,芯片间的高密度互连将进入um阶段,基于CoWoS封装的互连走线线宽甚至能到达到0.4um。由于趋肤效应,传统PCB和有机封装基板中的传输线电流大多流经导体的表面(图2)。当线宽接近于趋肤深度时,传输线截面基本上全部有电流经过,这使得我们在采用传统电磁场仿真引擎时,需要设置对导体内部进行求解,这会导致整体模型的网格数量急剧增加,同时对工程师的操作经验要求极高。

图 2

20Ghz时,典型CoWoS-S工艺下导体截面

电流分布和网格密度对损耗的影响

以TSMCCoWoS-S为例,Metal层的厚度在0.6um左右,RDL层布线一般在2um左右,最小可达0.4um。在该尺度下,如何能够兼顾仿真精度与效率,将考验电磁场仿真算法和工程师的设置技巧。

3. 大规模求解对高性能运算(HPC)的需求

对于3DIC架构的存算一体芯片来说,传统RC提取工具无法满足精度要求,大量高速SerDes和Memory互连线需要强大的全波三维电磁仿真引擎进行快速分析。由于互连结构的复杂程度,需要在进行网格剖分和未知量求解时采用多机器、多核心、多任务来进行仿真任务管理,SI/PI仿真分析时间在很大程度上决定产品的迭代周期。

芯和存算一体芯片仿真解决方案

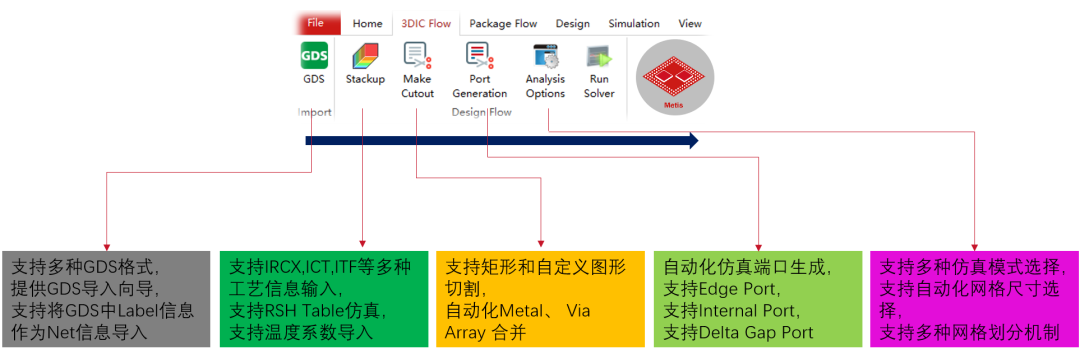

芯和半导体针对3D封装存算一体芯片提供了完整的信号完整性解决方案。Metis 作为整个解决方案中的关键电磁场求解引擎,是一款应用于3DIC先进封装联合仿真的 EDA 仿真平台,其内置了操作友好的3DIC先进封装仿真流程(图3),同时与3DIC Compiler 设计环境无缝集成,用户在设计的任何阶段都可以调用Metis工具来进行版图的电磁仿真;三维全波高精度电磁仿真可以满足异构集成中高速高频等应用的精度要求,并可以支持纳米到厘米级别的跨尺度仿真,实现芯片、封装的联合仿真;被用户广泛应用于CoWoS-S/CoWoS-R/FOCos/等3DIC先进封装的电磁场建模。

图3

Metis提供的3DIC建模流程

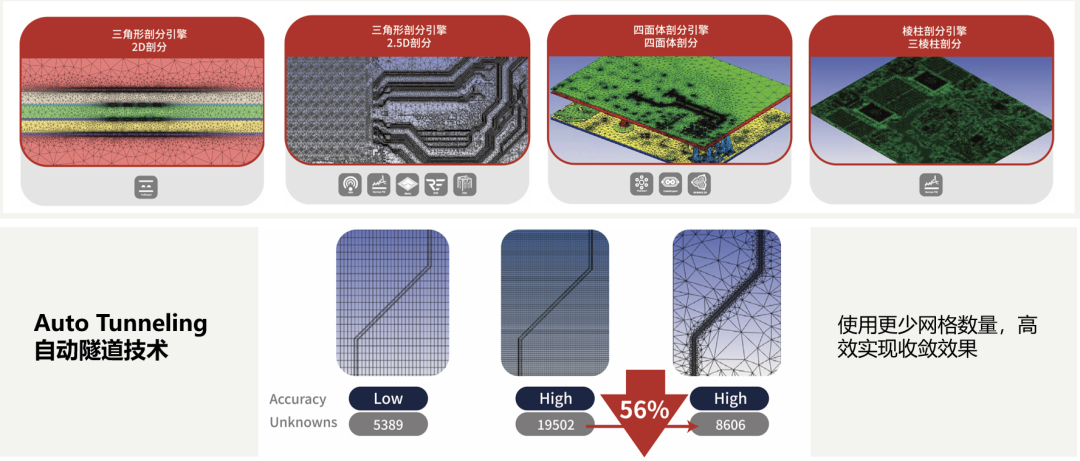

1.支持从0-100um多尺度跨越的

电磁场求解器

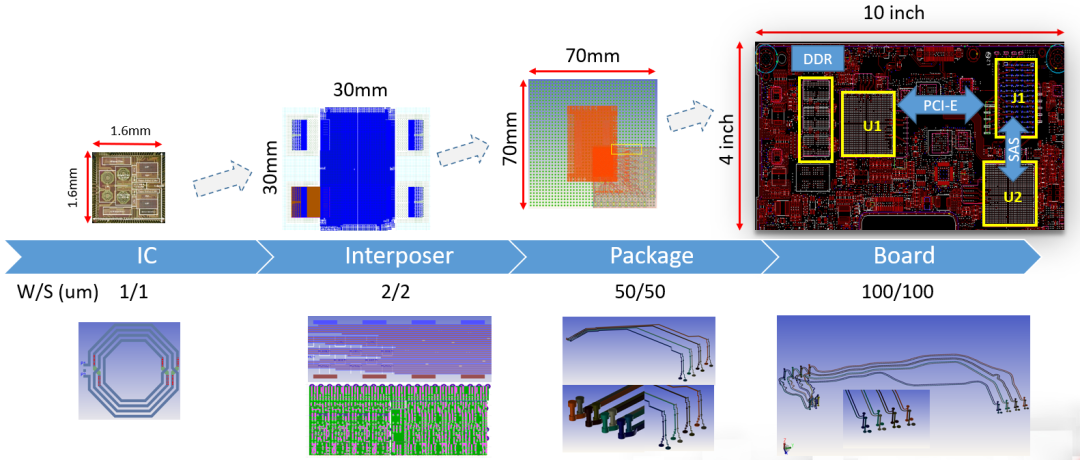

在芯片、封装和系统的电磁联合仿真上,由于模型尺寸跨度太大,难以进行统一的网格剖分。芯片走线的宽度和间距在1um以下级别,硅载板走线在2um左右,基板封装走线在50um左右,而PCB走线能达到100um左右(图4),如果对芯片使用基板封装的剖分机制,精度显然是不够的,同样,如果对基板封装使用芯片的网格剖分机制,那么对规模和速度上又会是巨大的挑战。

图4

芯片、封装和系统的物理尺度

针对这一场景,Metis平台有其自身的优势和特点,它内置了芯和的AI智能网格剖分融合技术(图5)能够根据结构的特点自动选择合适的网格尺寸,集成的多尺度快速电磁场求解算法,可以解决芯片、硅载板、有机封装到PCB的不同尺度所带来的联合仿真问题。

图5

AI智能网格剖分融合技术

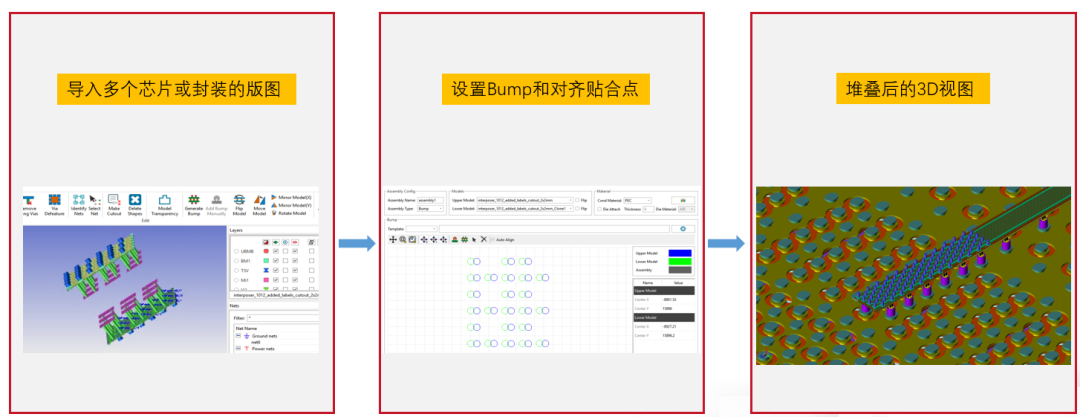

2.支持多Die三维堆叠建模和联合仿真

基于3D堆叠的存算一体芯片中,异构集成的芯片通过混合键合技术进行高密度互连,芯和半导体的Metis提供了多芯片堆叠的建模向导(图6),用户可以导入多个芯片GDS或封装版图,然后设置用于连接的TSV和bump的尺寸、填充材料等属性,这时也可以对芯片进行flip,mirror等操作,之后,可以进行坐标定位,或是bump位置的自动对齐,实现多个芯片的堆叠互连。最后使用堆叠后的3D互联结构,进行统一的网格划分和电磁求解,可对互联结构的电磁场分布和损耗、串扰等进行精确模拟。

图 6

Metis三维堆叠建模流程

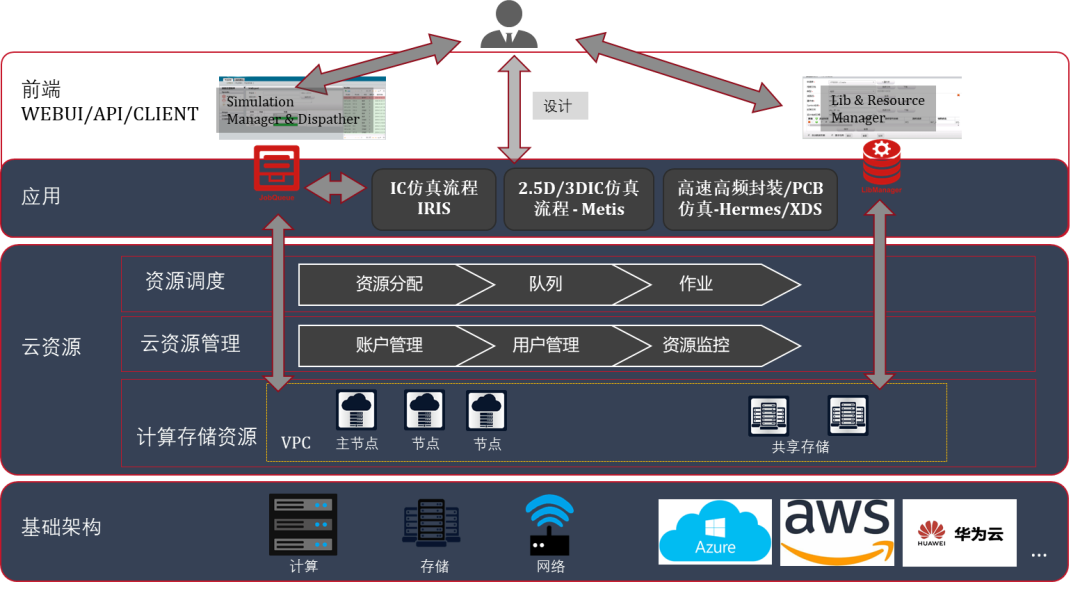

3.支持云平台的高性能计算

多芯片或Die+Package的堆叠建模仿真中,其网格密度高,普通单台服务器难以快速仿真并得到结果。芯和电子系统设计仿真云平台已登录微软、亚马逊、华为云等领先平台(图7),其解决方案集成核心差异化的电磁场仿真技术与软件、本地集群仿真技术、MPI仿真技术、云计算技术和分布式集群管理技术,使芯片、封装、系统设计大规模电磁仿真EDA的资源管理和资源统一调度使用成为了可能,通过使用优秀的管理系统和管理策略,达到资源统一分配和管理,不仅增加了各计算中的资源利用率,降低了计算中心的维护和部署成本,同时发挥芯和仿真软件的Intelligent Mesh、Scalable EM Solver多尺度电磁引擎、Parallel Computing并行计算能力,为电子系统设计中的芯片,封装,PCB,系统进行大规模复杂电磁场仿真提供了可能。

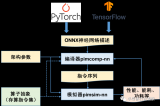

图 7

Xpeedic EDA 云平台架构

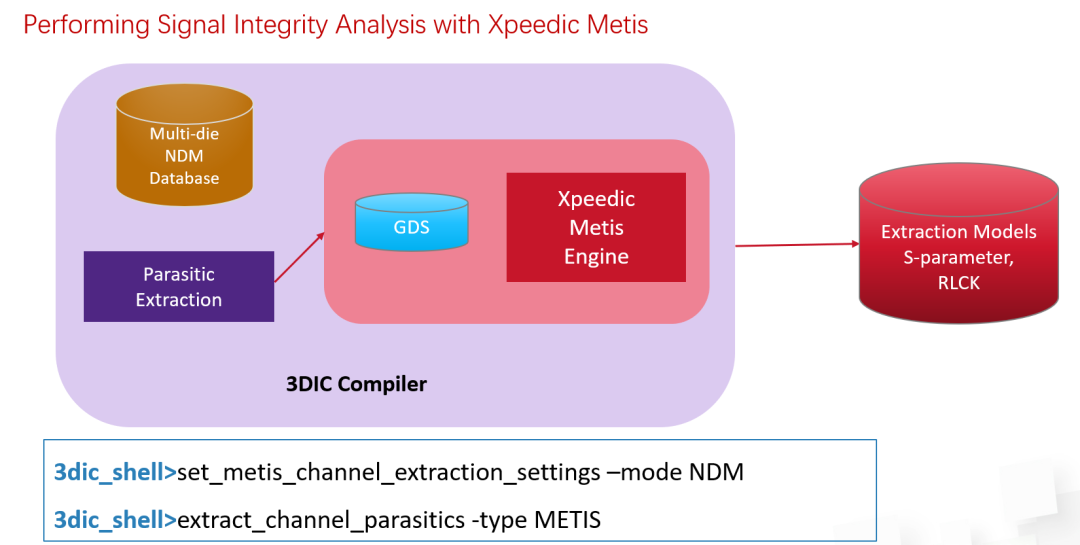

4.支持从3DIC设计到仿真的全流程解决方案

传统的EDA流程在进行2.5D、3DIC集成设计的时候,需要在多个工具的图形用户环境中设计、分析及交换数据。存在全系统分散式管理,多种点工具的协作交互繁琐,系统容量和结构形式受限,设计和分析工具之间的第三方接口不够顺畅等问题。

芯和半导体的2.5D/3DIC先进封装分析方案Metis与3DIC Compiler现有的设计流程无缝结合,为客户构建了一个完全集成、性能卓著且易于使用的环境(图8),提供了从开发、设计、验证、信号完整性仿真、电源完整性仿真到最终签核的3DIC全流程解决方案。突破了传统封装技术的极限,该方案能同时支持芯片间几十万根数据通道的互联。

图 8

在3DIC Compiler中调用Metis电磁场求解引擎

总结

本文首先讲述了存算一体芯片的发展现状和市场情况,然后总结了存算一体芯片仿真分析中所面临的挑战。针对这些挑战,芯和半导体推出的存算一体芯片仿真方案集成了差异化的电磁场仿真技术、内置了AI智能网格剖分融合技术、多尺度快速电磁场求解算法、3DIC流程化建模向导、HPC加速技术,使存算一体芯片、封装、系统设计大规模电磁仿真成为可能。同时,3DIC Compiler到Metis工具中的无缝对接,大大减少数据交换风险,统一的设计、仿真、验证平台减少了用户芯片的设计迭代。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54429浏览量

469362 -

仿真

+关注

关注

55文章

4535浏览量

138664 -

AI

+关注

关注

91文章

41115浏览量

302602 -

3DIC

+关注

关注

3文章

92浏览量

20167 -

存算一体

+关注

关注

1文章

121浏览量

5216

原文标题:【解决方案】基于3DIC架构的存算一体芯片仿真解决方案

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

存算一体大算力AI芯片将逐渐走向落地应用

新思科技推出3DIC Compiler平台,转变了复杂的2.5和3D多裸晶芯片系统的设计与集成

现在3DIC设计面临哪些挑战?

基于RISC-V开放架构的存算一体化芯片解决方案

基于3DIC架构的存算一体芯片仿真解决方案

基于3DIC架构的存算一体芯片仿真解决方案

评论