在电子数据管理刚出现的时候,数据还是相对比较安全的。但如今,数据世界已经发生了变化,现在的数据环境互联且相互依赖,比以前复杂多了。以前从没想过的安全漏洞现在层出不穷,所以软硬件保护必须两手都要抓。

现在越来越多的开发者选择把作业放到超大规模数据中心的服务器上来运行。但部署大量服务器的超大规模数据中心也存在一定的风险,并不能完全保障数据的安全。首先数据中心上会有大量客户的作业,他们各自使用不同的设备,数据中心会根据每位客户的业务量来分配特定数量的内存和处理器内核,以供客户完成所需的作业和任务。

其次,这些运作并不由开发者们本人直接控制,所以不能确定数据中心内是否会有人使用示波器和逻辑分析仪来探测大家所用服务器的内部信号,也无法得知是否有人窥探客户的硬件和虚拟机。

因此,虚拟服务器内部需要硬件加密,即利用安全加密密钥交换来在虚拟机和硬件之间进行通信。这样一来,任何第三方便都无法访问加密设备了,即便是拥有、管理和日常运行数据中心的第三方也无法访问。

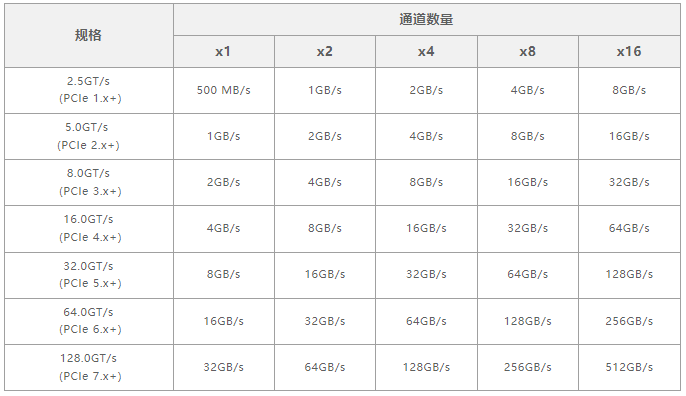

TEE设备接口安全协议(TDISP)是一种用于保护I/O虚拟化的新框架和架构,它通过工程变更通知(ECN)引入最新的PCI Express(PCIe)6.0规范当中。虽然PCIe 6.0规范引入了新的64GT/s信号传输速度,但TDISP可以在任何速度下使用。无论数据中心建在哪里,也不管谁可以访问其中的服务器,该标准化接口框架都定义了如何保护虚拟主机和设备之间的互连。

网络攻击目标

从软件拓展到硬件

网络攻击目标现在已经不再局限于软件,硬件现在也容易出现安全漏洞。要对此进行防范,关键在于:每台设备都需要执行功能并进行加密,以便与数据中心中的虚拟机交换密钥。但这个过程其实相当复杂。

比如说,A公司是家CPU供应商,而数据中心的虚拟机硬件已经与该CPU兼容。这种情况下虚拟机已经知道该CPU的硬件加密了,因此无需安全接口框架,但如果使用的是共享虚拟服务器,插接的设备可能来自A公司、B公司、C公司……在这种情况下就需要让软件了解每种设备,才能确保正确加密。

过去如果想要确保正确加密,就必须以专有的方式进行,而企业通常在这方面做得都不太好。那么问题来了,如何让保护接口防范攻击的能力实现标准化,而又不必为每种设备构建独特的接口呢?

借助TDISP实现

安全的密钥交换

TDISP的主要作用是密钥管理。它就像一个控制面板,能够打开和关闭加密,这样就可以在接下来1小时、10分钟或任何其他时间段刷新密钥。TDISP框架使得该过程实现标准化,并能够管理整个密钥交换,开发者无需为每种不同的设备构建独特的接口。

在硬件方面,当连接完成并安全建立链路后,如果发现存在TDISP之外的寄存器操作,开发者便可以确定连接已经不再安全了。通过TDISP,开发者可以检测企图拦截通信的行为,从而向软件发送信号,让它知道出现了问题,以便在出现安全漏洞之前修复链路。

TDISP是一种先进的框架,可以作为整体安全战略的一部分,通过将IO互连安全方案实现标准化来防范攻击,降低风险。

业界首个支持TDISP

的控制器和IDE模块

新思科技一直在安全相关领域保持领先,现已推出了首个支持TDISP的控制器与可靠性和数据加密(IDE)安全IP模块,该模块适用于PCIe和CXO.io。它包含在设备上实现TDISP所需的所有硬件挂钩和构建模块,是完整的PCIe安全解决方案的一部分。

PCIe TDISP(也适用于CXO.io)包括以下功能:

-

PCIe控制器与IDE功能以及其他寄存器

-

T位数据包支持(TX和RX)

-

针对入站请求和完成情况的规则检查

-

针对TEE限流附加检查

-

让设备安全管理器(DSM)能够跟踪TEE-Device-Interface-owned(TDI-owned)配置更改的接口

-

TDISP特定的错误状况更新

-

以避免配置寄存器更新的信号锁定

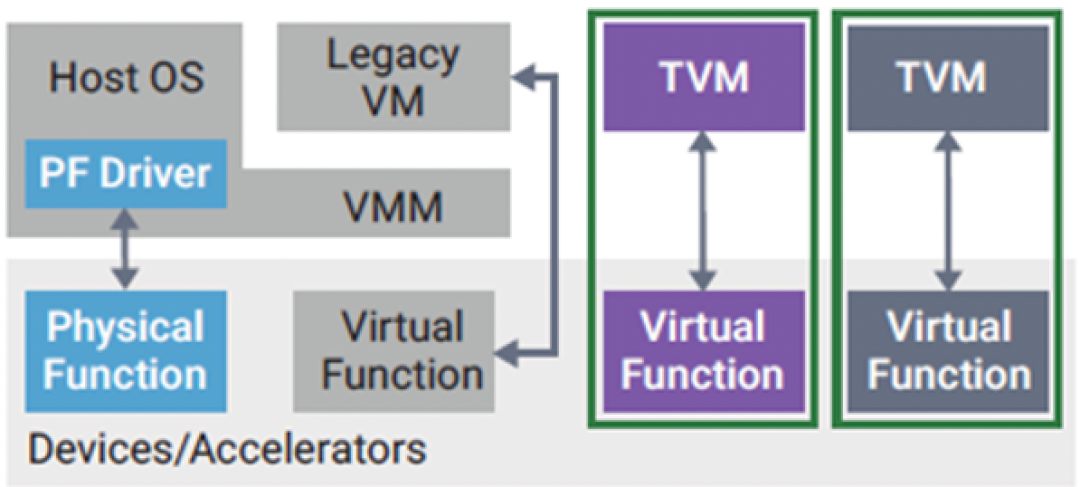

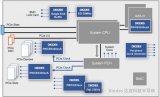

▲TDISP 全面支持将虚拟功能中的可信分配与可信虚拟机 (TVM) 的互相交互

新思科技的IP解决方案可以帮助开发者实现此框架来抵御攻击和降低相关风险。

扫描下方二维码,进一步了解TDISP框架如何帮助保护数据。

PCI Express 6.0的IDE安全IP模块

PCIe Express 6.0的控制器IP

原文标题:PCIe 6.0接口新架构下,如何确保数据安全?

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

新思科技

+关注

关注

5文章

923浏览量

52631

原文标题:PCIe 6.0接口新架构下,如何确保数据安全?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

【PCIE725G】青翼凌云科技基于 PCIe x16 总线架构的 JFM9VU9P FPGA 高性能数据预处理平台(100%国产化)

【PCIE737】青翼凌云科技基于全高PCIe x8总线的KU115 FPGA高性能硬件加速卡

【PCIE723】青翼凌云科技基于 VU3P FPGA 的 100%全国产化高性能 PCIe 数据预处理载板

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

嵌入式接口通识知识之PCIe接口

PCIe协议分析仪在数据中心中有何作用?

PCIe协议分析仪能测试哪些设备?

Diodes公司PCIe 6.0时钟缓冲器介绍

PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

【高清视频案例分享】CameraLink接口的PCIe采集卡 ,基于FPGA开发平台

是德科技PCIe 6.0发射机合规性测试解决方案

PCIe 6.0时代的测试挑战和解决方案

PCIe 6.0 互操作性PHY验证测试方案

PCIe 6.0接口新架构下,如何确保数据安全?

PCIe 6.0接口新架构下,如何确保数据安全?

评论