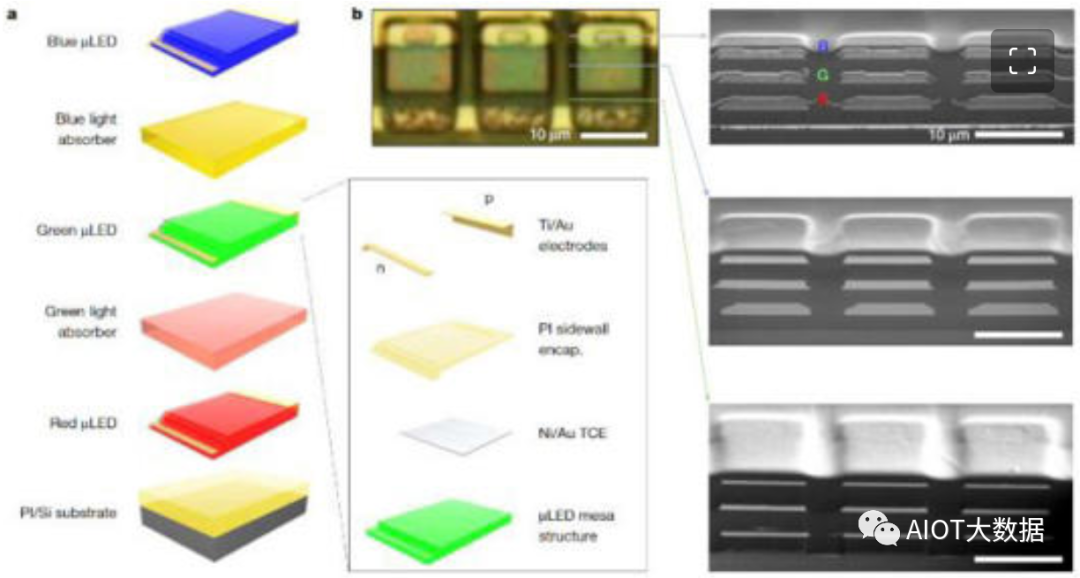

继韩国成功开发出垂直堆叠MicroLED技术后,麻省理工大学(MIT)近期发表在《Nature》上发表论文显示,正在开发采用垂直堆叠的 MicroLED 技术,将像素密度推高到 5000 PPI。

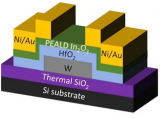

这项研究由 Jeehwan Kim 领导,他是一位专门制造超薄高性能膜的工程学教授。该团队在过去的科研成果基础上,在二维膜材料上制造红色、绿色和蓝色子像素的膜。

接下来从刚性基层上剥离薄膜,然后将它们堆叠在一起,形成了只有 4 微米宽的垂直全彩色像素。

论文第一作者Jiho Shin解释说道,“对于VR来说,现在市场中显示屏的真实程度是有限的。有了我们的垂直MicroLED,你就可以拥有一个完全沉浸式的体验,而且无法区分虚拟和现实。”

除了垂直堆叠LED之外,该团队还使用了一种新的制造技术,旨在让LED“生长”在晶圆上,然后将它们剥离出来进行堆叠。他们声称这比竞争对手的方法要更快,尽管单个像素的尺寸为4微米。

不过,目前这项技术只在小范围内得到了验证。而且,理论上MicroLED能够实现的像素密度的大屏幕显示仍然是一个未解决的问题。“你需要一个系统来分别控制2500万个LED,”Shin解释说,“在这里,我们只是部分地证明了这一点。有源矩阵操作是我们需要进一步研究的技术。”

"LED发出的光的颜色(能量)取决于LED的带隙--蓝色LED的带隙最宽(因此蓝光的能量最高),红色LED的带隙最小(能量最低)。"一种材料不会吸收能量小于带隙的光(光子),因此红光和绿光将穿透蓝色LED层而不被吸收,这就是为什么我们按照R(底部)、G(中部)、B(顶部)的顺序垂直堆叠这些层。

此前在2022年柏林国际IFA展会上,首尔半导体旗下光半导体设备制造企业Seoul Viosys宣布推出了基于层压结构的多层microLED技术,可用于制造对角线尺寸在100-200英寸之间的4K高分辨率显示屏。

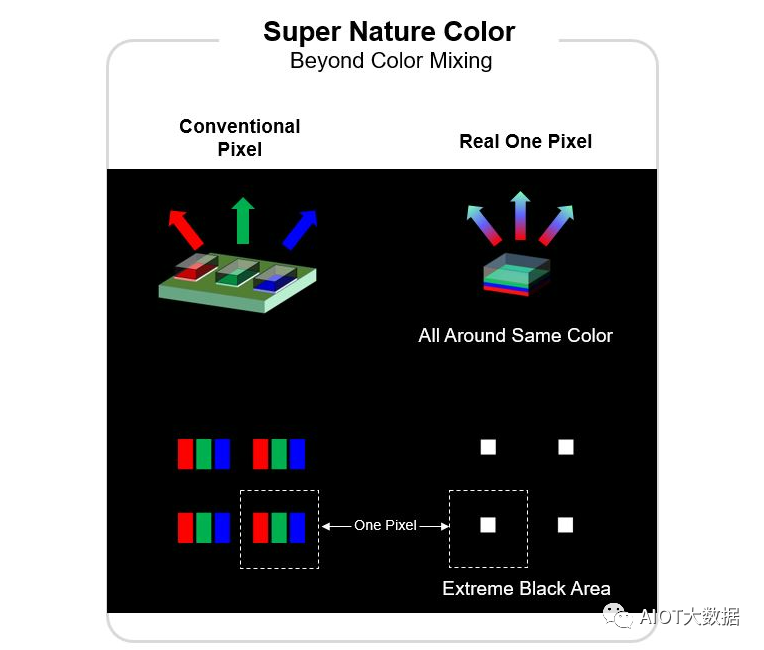

这一技术的特别之处在于,它使用显示红色、绿色和蓝色(R/G/B)的三个芯片垂直堆叠,而不是通常的水平阵列。它与传统microLED的主要区别是,堆叠结构中的R/G/B LED通过完美的颜色混合(包括白色)发出颜色,就像它们构成了一个像素。

(图片来源:Seoul Viosys)

目前,研究人员还不清楚在堆叠中发生了多少光吸收,以及是否必须通过使更深的层变得更硬来解决这个问题。

Seoul Viosys公司表示,他们使用一种成型技术来控制莫尔条纹(Moiré pattern)现象,并使用低反射技术来创造出深黑色形成高对比度,有助于在光线下浏览microLED显示屏。同时,从像素内部向外发射结合了R/G/B的颜色,因此无论从哪个方向看,都不会产生失真,可以欣赏到清晰的图像。

本次IFA展会上,Seoul Viosys将展示两款microLED显示器,包括一款54英寸高分辨率、间距0.625mm (P0.625)的显示器和一款81.5英寸、间距0.9375mm (P0.9375)的显示器。另外,包含其microLED核心生产工艺的各种产品也将亮相。

与此同时,首尔Viosys还将展示与microLED技术相配套的显示LED技术,如控制莫尔条纹现象并突出黑色细节的成型技术、在光线下实现鲜艳色彩和高对比度的低反射技术、可以轻松安装和更换微显示器,并可以改变大小的自由形状定制设计机柜显示器等。

现代显示屏的每个彩色像素由3个或更多的子像素组成,这些子像素通常是红色、绿色和蓝色。通过改变每个子像素的光输出,可以控制整个像素的颜色。但这样做必须把三个子像素并排放在一起,这就限制了一个像素的大小。

审核编辑 :李倩

-

显示器

+关注

关注

22文章

5159浏览量

144760 -

MicroLED

+关注

关注

31文章

636浏览量

40727 -

半导体设备

+关注

关注

5文章

428浏览量

16686

原文标题:美韩相继开发出垂直堆叠MicroLED技术

文章出处:【微信号:AIOT大数据,微信公众号:AIOT大数据】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MicroLED概念股全线爆发下铜缆的命何去何从

不同于HBM垂直堆叠,英特尔新型内存ZAM技术采用交错互连拓扑结构

博世碳化硅垂直沟槽蚀刻技术的核心优势

单相继电保护测试仪用途是什么?

SK海力士HBS存储技术,基于垂直导线扇出VFO封装工艺

真空共晶炉/真空焊接炉——堆叠封装

【置顶公告】视美泰开源鸿蒙系列产品业务咨询与商务合作通道正式开启!

东芝硬盘率先完成 12 盘片堆叠技术验证

200万尼特红光!鸿石智能QDPR+混合堆叠破局,MicroLED全彩化加速

美光宣布:停止移动 NAND开发,包括终止UFS5开发

Micro LED制造工艺中四大关键技术难点

美光12层堆叠36GB HBM4内存已向主要客户出货

领跑MicroLED赛道:鸿石智能单绿色量产,全彩化2026年落地

美韩相继开发出垂直堆叠MicroLED技术

美韩相继开发出垂直堆叠MicroLED技术

评论