随着摩尔定律的放缓,芯粒(Chiplet)和异构集成 (HI:heterogenous integration) 提供了一种令人信服的方式来继续改进性能、功耗、面积和成本 (PPAC),但是选择连接这些设备的最佳方式以使它们以一致且可预测的方式运行是随着选项数量的不断增加,这成为一个挑战。

更多的可能性也带来更多潜在的连接方式。因此,虽然 AI、5G、高性能计算、移动和可穿戴设备中的下一代应用都受益于不同设备在紧凑封装中的各种组合,但仅对不断增加的互连选择进行分类是一项挑战。但有利的一面是,该行业不再受一套规则的束缚,定制和优化系统的可能性正在呈爆炸式增长。

Promex工程副总裁 Chip Greely 说:“异构集成的美妙之处在于它现在并不总是适用于电气。” “你也可以将机电设备放入你的封装中。对于我们的一些产品领域——例如,医用相机——我们将机械和电气功能整合在一个很小的空间内。如果你想拥有一个稳健的制造过程,你就会试图让你包括机械接口在内的接口尽可能容忍任何未对准或放置精度的任何变化。”

三星、英特尔、台积电和许多其他设备制造商正专注于优化各种架构中的芯片到芯片(die-to-die)和芯片到封装(die-to-package)互连,无论是使用微凸块、混合键合和桥接的垂直构建,还是使用扇出重新分布的水平构建层。决定如何以及在何处形成互连正在成为系统集成的重要组成部分。

封装选项的数量正在增加,因为许多新设计都是针对特定应用高度定制的。因此,它们的构造和连接方式通常取决于需要处理的数据量和类型、需要处理的位置以及可用功率。例证:特斯拉的 D1 Dojo 芯片是一块 500 亿晶体管芯片,用于在特斯拉数据中心内训练 AI 模型。特斯拉低压电子产品副总裁皮特·班农 (Pete Bannon) 在最近的一次演讲中表示,这里的重点是海量数据吞吐量,使用具有内置灵活性的高度并行计算。

特斯拉的设备基于台积电的集成扇出(InFO) 技术,在阵列中包含 25 个 D1 芯粒。Bannon 表示,该设备可以达到 9 petaflops,使用 576 通道的 I/O 环以每秒 36 TB 的速度移动。它还包括 3 个窄 RDL 层和 3 个厚 RDL 层。

与此同时,台积电的路线图要求采用可将电阻降低 40% 的新型低电阻互连。台积电高级副总裁Yuh Jier Mii 表示,该方案不是通过大马士革(damascene)制造,而是通过带气隙而不是电介质的减法金属反应离子蚀刻(subtractive metal reactive ion etch)制造,可以将电容降低 20% 至 30%,并最终用 2D 互连材料取代铜互连。Mii 在最近的一次演示中表示:“随着电阻率降低,未来有可能通过增强的互连性能进行扩展。”

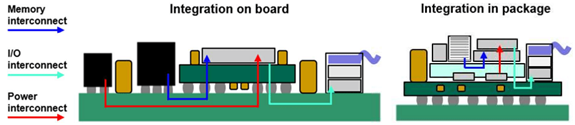

图 1:从板上芯片到异构集成的重新配置和互连路径

异构集成的路线图正在通过混合键合、更多地使用硅桥、二氧化硅和尺寸越来越大的聚合物中介层转向更多的芯片堆叠。为了满足不同的最终用途,体系结构和封装类型不断增加。

不同的架构,优先级

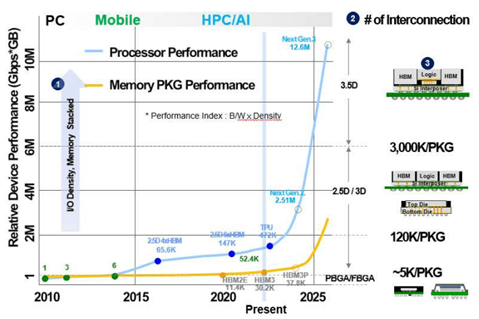

“先进封装架构有望导致 I/O 互连呈指数级增长,”三星电子公司副总裁 Seung Wook Yoon 说(见图 1)。Yoon 在 IEDM上详细介绍了该公司用于芯粒集成的先进封装 FAB 解决方案 (APFS),重点介绍了先进封装流程中的四个关键工艺——薄晶圆切割、混合键合、薄晶圆剥离(零应力)和垂直互连. “对于芯粒技术,晶圆厚度和凸点间距是关键参数。目前,最先进的 HBM 封装的晶圆厚度小于 40μm,并将超过 16 个裸片堆叠到一个封装中。”

三星有四种不同的封装配置:2.5D RDL (R-Cube)、2.5D 硅中介层 (I-Cube)、3D-IC堆叠、采用混合键合的 X-Cube 微凸块和混合中介层(H-Cube)。

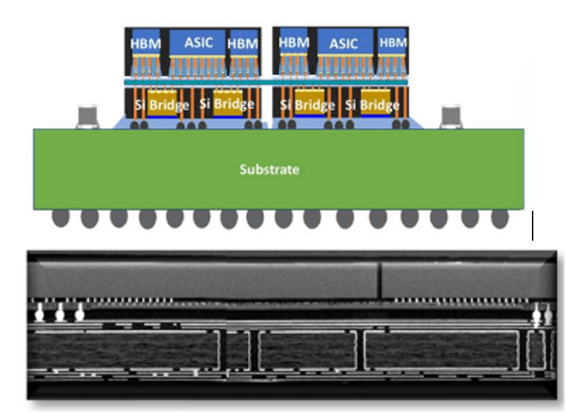

图 2:高带宽内存和 AI/高性能计算中不断增加的互连数量

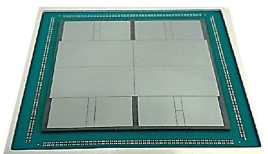

不断增加的电气、机械和热问题也在推动 HI 工艺解决方案的发展。例如,TSMC 展示了它如何解决由 4 个SoC 和 8 个 HBM 在 78 x 72mm 基板上的 50 x 54 mm 有机中介层上组成的系统中的噪声问题(见图 3)。在此设计中,用于芯片间连接的微凸块的最小凸块间距为 35μm。有机中介层(50 x 54 毫米或 3.3X 光罩尺寸)包含大约 53,000 条再分布层线(redistribution layer lines)。

图 3:约 53,000条细间距 2um RDL 线形成总长 140 米,将 4 个 SOC 和 8 个 HBM 与层压基板 (CoWoS-R) 上的有机中介层连接起来

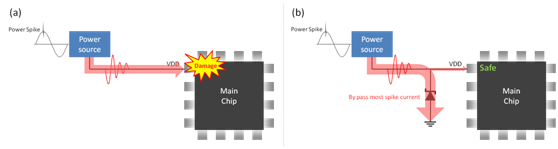

台积电在其中介层电介质的 C4 凸点侧集成了一个分立式去耦电容器,非常靠近 SoC 器件,以确保快速抑制电源域噪声。这反过来又增强了 HBM 在高数据速率下的信号完整性。

热问题虽然对半导体行业来说并不新鲜,但当更多的计算和电源管理设备彼此靠近放置时,热问题会变得更加严重。Greely 指出了内存和电源管理 IC 等组合,它们通常必须在一个封装内隔离。“电源管理就像一个老式的暖手器,而内存不喜欢超过 85°C,更不用说 100°C。”

中介层,无论是基于硅还是基于聚合物的薄膜,都有助于互连并充当异质芯片堆栈的应力消除缓冲器。压力管理以及芯片移位最小化是晶圆厂开始从架构规划和工艺方面着手解决的持续性问题。

ASE 在 IEDM 上展示了其三个垂直集成扇出封装线的详细信息。“对于 2.5D 和 3D,我们看到了密度和带宽的增加。但我们也看到成本增加,这导致我们开发和引入了 ViPak 平台,” ASE工程和技术营销高级总监 Lihong Cao 说。“通过使用硅桥,L/S 芯片到芯片互连可以扩展到 0.8μm,甚至 0.65μm。所以在这个过程中,你最后放上die,但将桥接die放在载体上并使用铜柱连接。并且有两个成型步骤。首先是保护桥接die。所以我不使用 RDL 进行互连,连接是通过桥接裸片,你可以使用 65nm 工艺设计桥接裸片,然后最后贴上芯片。”

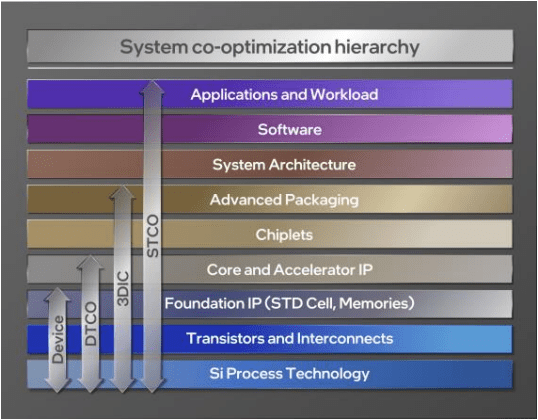

异构系统本身就是系统或子系统。他们需要系统技术协同优化 (STCO),这是 IEDM 庆祝晶体管发明 75 周年并展望下一个 75 年的主题。英特尔技术开发总经理 Ann Kelleher 表示:“庆祝晶体管的最佳方式是期待我们如何确保在未来 75 年内带来尽可能多的创新。”“基于系统的技术协同优化 (STCO) 是摩尔定律的下一步发展。”

STCO 将设计技术协同优化提升到系统级,为一个或多个制造流程优化设计工具。根据 Kelleher 的说法,下一阶段“就是我所说的从工作量开始工作。” 这包括系统和软件的所有方面,直至整个制造过程(见图 4),同时优化系统设计、软件、设备、互连、晶体管等。

图 4:STCO 从工作负载开始,考虑晶圆厂和封装制造和设计以及软件和系统架构的所有方面

在工艺技术方面,Kelleher 指出晶体管将在 2023 年转变为环栅 FET,在2025 年转变为高 NA EUV,下一代互连金属、铁电材料,以及光学互连的最终结合。

混合键合

混合键合之所以称为混合键合,是因为它同时键合了铜对铜焊盘(copper-to-copper pads)和电介质对电介质场(dielectric-to-dielectric fields),提供了终极的垂直连接。相对于铜微凸块,混合键合可将信号延迟降至接近零,同时使凸块密度提高 1,000 倍。微凸点间距目前在 35μm 以上。对于混合键合,正在评估小于 20μm的间距。

“我们正在与客户就几个有趣的混合绑定用例进行交流,包括高带宽边缘 AI 设备和 RF 组件。根据应用的不同,应用混合键合的好处可以是更高的性能和/或更强大的功能,在外形尺寸限制内,” UMC技术开发总监 Tony Lin 说。

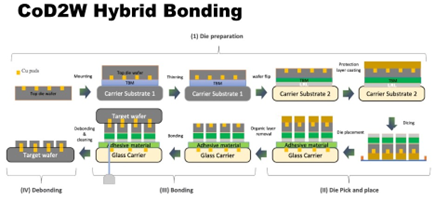

清洁界面和精确对准是具有生产价值的混合键合工艺的关键要素。晶圆对晶圆(W2W)键合和芯片对晶圆(C2W)键合工艺均可用。W2W更成熟,但它需要相同尺寸的芯片,几乎没有灵活性。芯片到晶圆的流程更加复杂,并且容易受到芯片放置对齐不准确的影响。提高贴装精度的一种方法是同时对多个裸片执行集体 D2W 键合(见图 5)。也有多种脱粘方法,重点是最大限度地减少基板应力、降低成本和提高产量。

例如,热方法成本低,但会引入压力,并且产量低。Brewer Science副主任 Alvin Lee 表示,化学方法可以在室温下进行,但通量仍然很低。激光剥离提供更快的吞吐量和低应力,但设备成本高。下一代光子剥离使用高强度光从玻璃上快速剥离晶圆,以更适中的工具成本引入很小的应力,Lee 指出。集体 D2W 混合键合是扇出封装的使能技术。

图 5:集体芯片到晶圆混合键合的工艺流程提供了比单独拾取和放置更高的吞吐量和卓越的对准精度

混合绑定的早期采用者的额外好处之一可能是他们能够实现相当于技术节点转换的性能提升。“我们的客户继续需要在他们的 IC 设计中实现更快的性能、更高的电源效率和更低的成本,这在过去是通过缩小晶体管来实现的,”UMC 的 Lin 说。“随着跟上摩尔定律变得更具挑战性和成本更高,混合键合可以提供我们客户寻求的性能改进,使其成为技术节点迁移的灵活替代解决方案。”

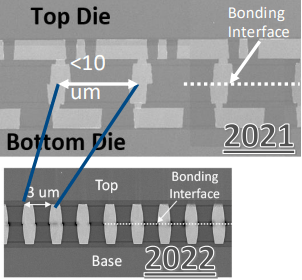

英特尔透露了其在混合键合方面的研发进展,从2021年的10μm间距铜-铜键合扩展到上个月的3微米间距键合(见图6)。一些专门针对混合键合优化的新工艺模块包括调整 PECVD 氧化物沉积工艺以沉积厚 (20μm) 的低应力薄膜,改进氧化物 CMP 浆料以加快抛光速度,以及创建高纵横比蚀刻和填充工艺对于通过电介质过孔。

图 6:2021 年演示了间距为 10μm的混合铜-铜键合,2022 年演示了间距为 3微米的混合铜-铜键合,密度增加了 1,000 倍

但这些过程也有一些问题需要解决,这需要时间。例如,芯片移位可能是先进封装和异构集成的一个重要问题。Greely 说:“也许您的互连焊盘尺寸过大,这样您就可以为任何芯片移位做出妥协。” “当你放下 RDL 层时,registration将是关键。”

插入结构(An interposing structure)

插入器(interposing)本身不是分立元件。它是芯片(或芯片)和下面的层压基板之间的中间结构。尽管业界经常提到硅中介层,但构成硅中介层的材料都是电介质,即二氧化硅。基于聚合物的中介层比硅中介层便宜得多,但它们在某些应用中缺乏可靠性。

台积电探索了有机中介层在电气性能、翘曲控制、良率和可靠性方面的优势。“传输损耗是线路长度的函数。对于固定的每比特能量功耗设计预算,需要缩短互连长度以实现高带宽,”台积电后端技术服务部总监 Shin-Puu Jeng 说。

该代工厂一直致力于提高其堆叠技术的可靠性。“当你进入高速时,CoWoS-R的优势更大,因为 RC 的优势在高频下衰减得更慢,”Jeng 说。CoWoS-R 中的有机中介层由聚合物中的铜线组成(介电常数 = 3.3)。“非常密集的垂直连接可实现低阻抗电力传输网络。从铜/氧化物模拟眼图可以看到,氧化物中较薄的铜,聚合物中的铜,表明聚合物中铜的线长具有更大的灵活性。在 CPU 到 HBM 互连的情况下,长RDL 互连(L/S = 2μm/2μm)变厚(4μm)以减少高速数据传输的负载,同时也改善 IR 压降用于供电网络。与薄或厚 TSV 相比,聚合物通孔的插入损耗更低。RC 延迟会影响功耗。电力传输具有水平和垂直传输组件。非常密集的垂直连接提供低阻抗PDN。去耦电容器对于抑制电源噪声和实现稳定的电压供应很重要。”

建立桥梁

英特尔和台积电一直在使用专有的硅桥技术来互连高带宽内存模块和CPU/GPU。ASE 最近推出了一个带有嵌入式桥的封装平台,能够以 0.8 微米的线和间距 (FoCoS-B) 连接芯粒到芯粒。

“由于固有的扇出 RDL 工艺限制,FOCoS-CF 和 FOCoS-CL(先芯片后芯片)解决方案在制造具有高层数(>6 层)和细线/间距(L /S = 1μm/1μm),适用于需要高密度 die-to-die 连接、高输入/输出计数和高速信号传输的应用,”ASE 的 Cao 说。FOCoS-B 为多个桥接芯片集成提供了多种选择。在一个示例中,8 个硅桥芯片嵌入到两个相同的扇出 RDL 结构中,具有 2 个 ASIC 和 8 个 HBM2e 模块。它们使用两个相同的扇出模块进行安装,这些模块组装在 MCM 中的一个倒装芯片 BGA 基板上(见图 2)。FO 模块均为 47 x 31mm,封装体尺寸为 78 x 70mm。

图 7:基板桥上的扇出芯片 (FOCoS-B) 原理图(上图)和横截面图(下图)实现了比 RDL 更小的芯片到芯片连接 (0.8μm)

Cao 解释说,ASE 工程师通常还比较了 2.5D 与芯片在后和芯片在前的 FOCoS 方法的插入损耗、翘曲和可靠性。由于消除了硅中介层并减少了寄生电容和串扰,两种 FOCoS 方法都展示了优于 2.5D Si TSV 的电气性能。封装级翘曲,主要由芯片和基板以及扇出模块之间的 CTE(热膨胀系数)不匹配引起,显示出更好的翘曲控制,并且所有封装都在组装前通过了开路/短路和功能测试,以及可靠性压力测试 JEDEC 条件。

但这仍然不简单。“当我设计 BGA 基板时,铜平衡(copper balance)被敲打到我身上,以确保我们制作出良好的直板基板,”Promex 的 Greely 说。“现在,铜平衡是单个封装级别的问题,我将 7、10、12 个不同的器件放入不同的温度下,将它们贴附到基板上,我得到 12 到 14 微米从一个温度到另一个温度的翘曲变化。如果我有一个 50 毫米的基板,它有 250 微米的偏转,在室温下是凹面的,而在 300 度时则相反,现在它是凸面的。我正在尝试将一块漂亮的 25 微米背景硅放在那个东西上,并希望它在冷却回室温后保持一体。这可能是一个极端的例子,但这些都是严峻的挑战。”

热管理

在封装中,超过 90% 的热量通过封装从芯片顶部散发到散热器,通常是带垂直鳍片的阳极氧化铝基散热器。具有高导热性的热界面材料(TIM)放置在芯片和封装之间以帮助传递热量。用于 CPU 的下一代 TIM 包括金属板合金(如铟和锡)和银烧结锡,它们分别传导 60W/mK 和 50W/mK。

工程师和材料供应商继续探索替代 TIM。Amkor Technology的高级机械工程师 Nathan Whitchurch 说:“过去稀有的材料正变得越来越稀有”. “因此,对于烧结银,您最终会在盖子和管芯之间形成导热性非常高的银合金基体。另一种是较软的 TIM——铟基类型的东西。几年前,我们经常谈论相变材料。这似乎已经消失,因为人们意识到可靠性和优势并不存在。石墨垫之类的东西具有难以克服的工程挑战。单一方向上的石墨具有高导热性,但将其装入封装中是一项艰巨的挑战。所以这就是我们看到随着时间的推移,更奇特的材料变得不那么奇特的地方。”

结论

先进封装中的芯粒通过焊料、微凸块、RDL 和混合键合进行电气互连。所有这些连接都需要在模块的使用寿命内保持可靠。随着封装类型的激增和压力更低的新工艺的出现,工程师们发现异构集成提供的灵活性可能值得所有挑战。

关于芯粒和异构集成的讨论通常不会提及该行业采用这种新范式的时间有多早。“UCIe是一个非常好的开放标准,”ASE 首席执行官 Bill Chen 说。“有些人跑得比标准还快。但随后会有用户的反馈。” 然后,该反馈循环将更深入地了解未来需要什么。此外,供应商-客户生态系统将了解哪种类型的异构集成、组装技术、流程、设计工具等最有效。这将是一个过程。

三星的 Yoon 表示:“半导体才刚刚开始其芯粒和异构的旅程,因为设备缩放变得如此困难和昂贵,而且 PPAC 正在随着每个先进节点而缩小。”“芯粒设计标准将变得更加普遍,将这些设备组合在一起的更可预测的方式将接管。但所有这一切都需要数年时间,需要收集大数据、合作伙伴之间的协作以及跨价值链实验来确定什么是有效的。”

审核编辑:汤梓红

-

芯片

+关注

关注

462文章

53581浏览量

459705 -

cpu

+关注

关注

68文章

11223浏览量

223076 -

晶圆

+关注

关注

53文章

5349浏览量

131748 -

封装

+关注

关注

128文章

9153浏览量

147959 -

三星

+关注

关注

1文章

1738浏览量

33733

原文标题:芯片内部,如何互联?

文章出处:【微信号:TenOne_TSMC,微信公众号:芯片半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA资源与AISC对应关系

光电共封装

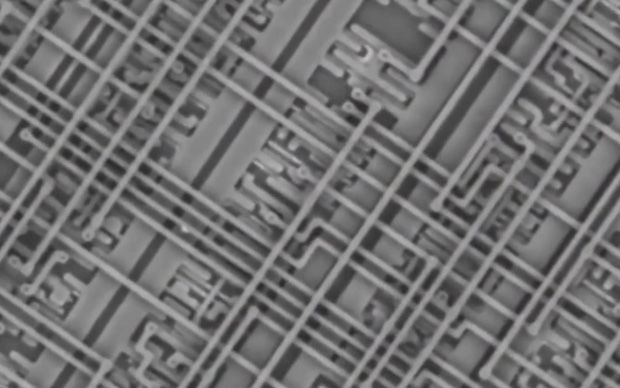

设计好的芯片内部是怎样的

芯片的内部线路图如何设计

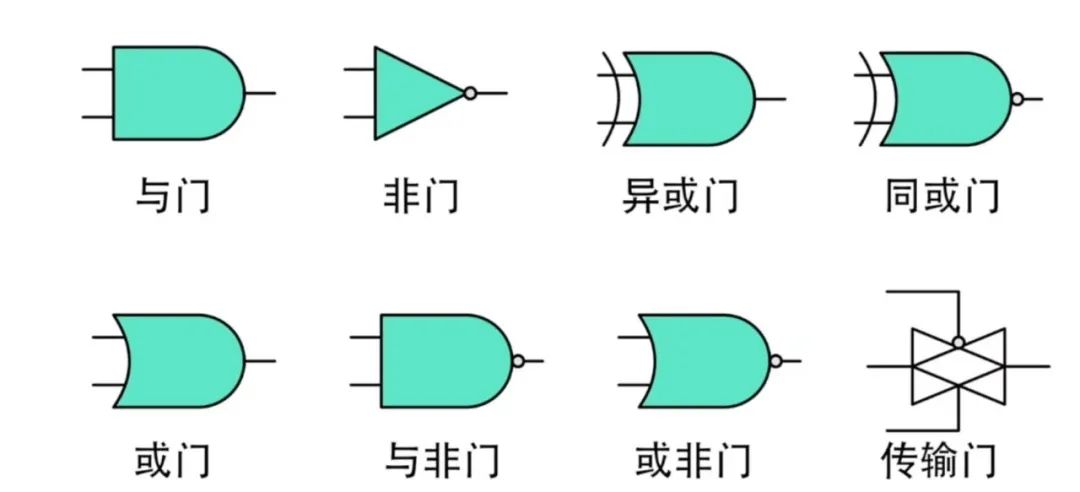

芯片内部电路的基本组成部分

芯片内部,如何互联?

芯片内部,如何互联?

评论