本文是有关ISE跟Moldelsim联合仿真的,大家在做联合仿真的时候,必须将两个软件同时启动才可以,这样不仅不方便,效率还非常低,每次更新一个文件,都需要从头开始把所有代码都编译一遍。同时,如果把这个联合仿真工程拷贝给别的同学,那么新环境下两个软件的版本也最好跟原版本的版本号一致才行。鉴于以上的诸多不便,最近研究了一下,找到了一种较为合适的方法,可以把联合仿真很方便的转换为用ModelSim的单独仿真。就可以有效的避免上述问题。

详细操作步骤

在把FPGA设计转化为ASIC设计的过程中,有一个非常重要的步骤必不可少,那就是替换掉原FPGA工具自动生成的IP核,在替换的过程中,需要做的一个非常重要的步骤就是需要用仿真工具单独对设计进行仿真,因为原来的仿真可能是用FPGA工具的联合仿真。本文就介绍一种ISE联合仿真转换为Moldelsim单独仿真的方法,欢迎探讨。以下是详细操作步骤。

1、复制所需文件。

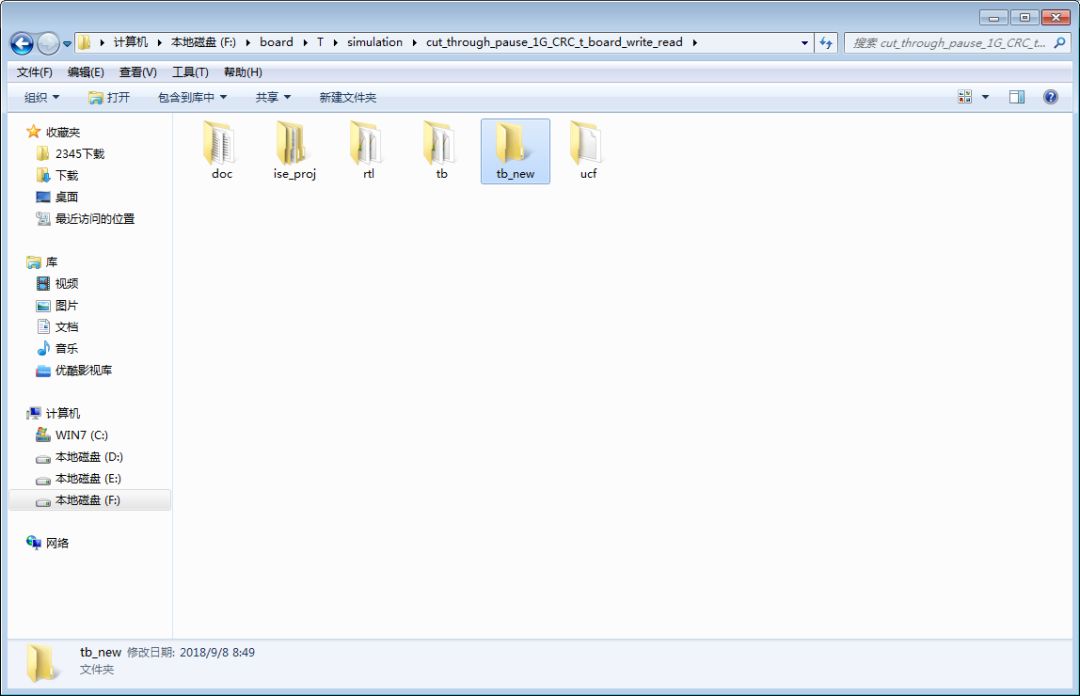

在ISE工程里面某个位置建立新文件夹,我的文件夹名为tb_new。

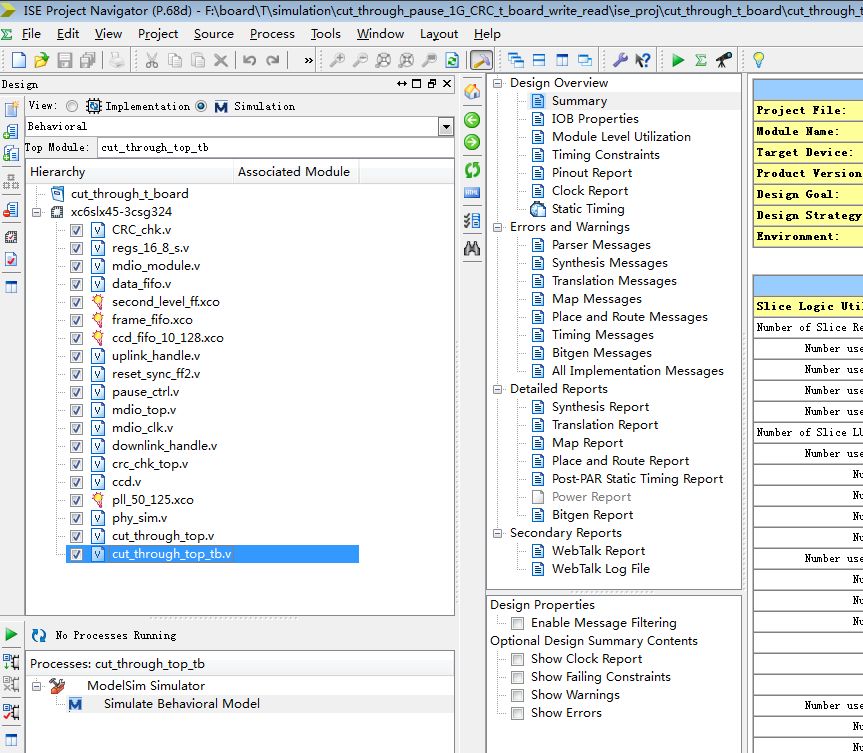

找到仿真顶层的tb文件,cut_through_top_tb。

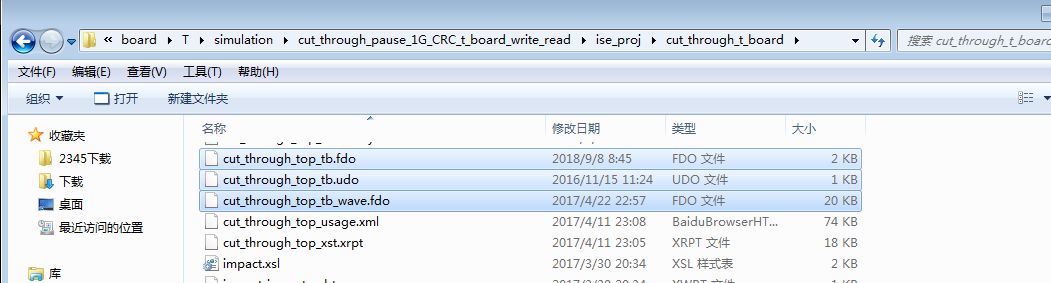

在ise的工程目录下,注意是工程目录下,找到跟顶层cut_through_top_tb相关的以下三个文件,拷贝只新建的modelsim仿真工程目录下。

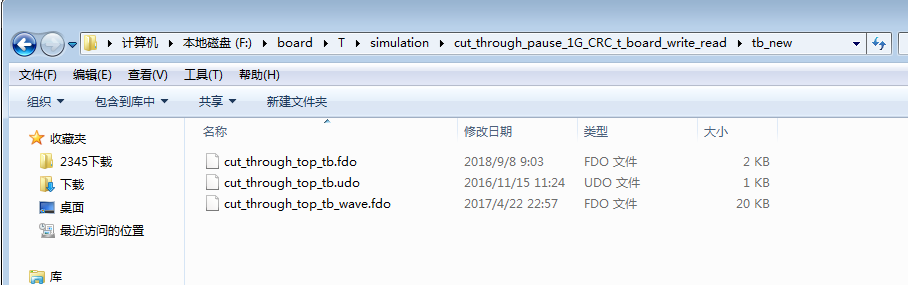

在ISE工程文件夹中找到所需的文件,并复制到tb_new中,所需的文件见下图所示。

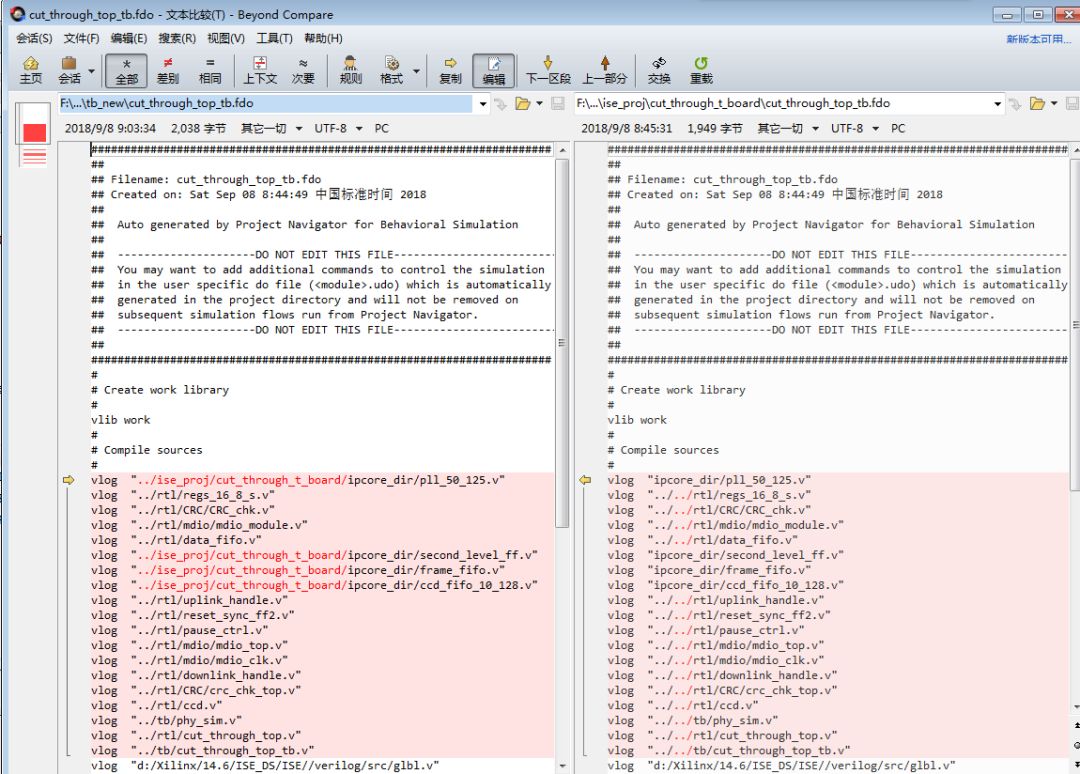

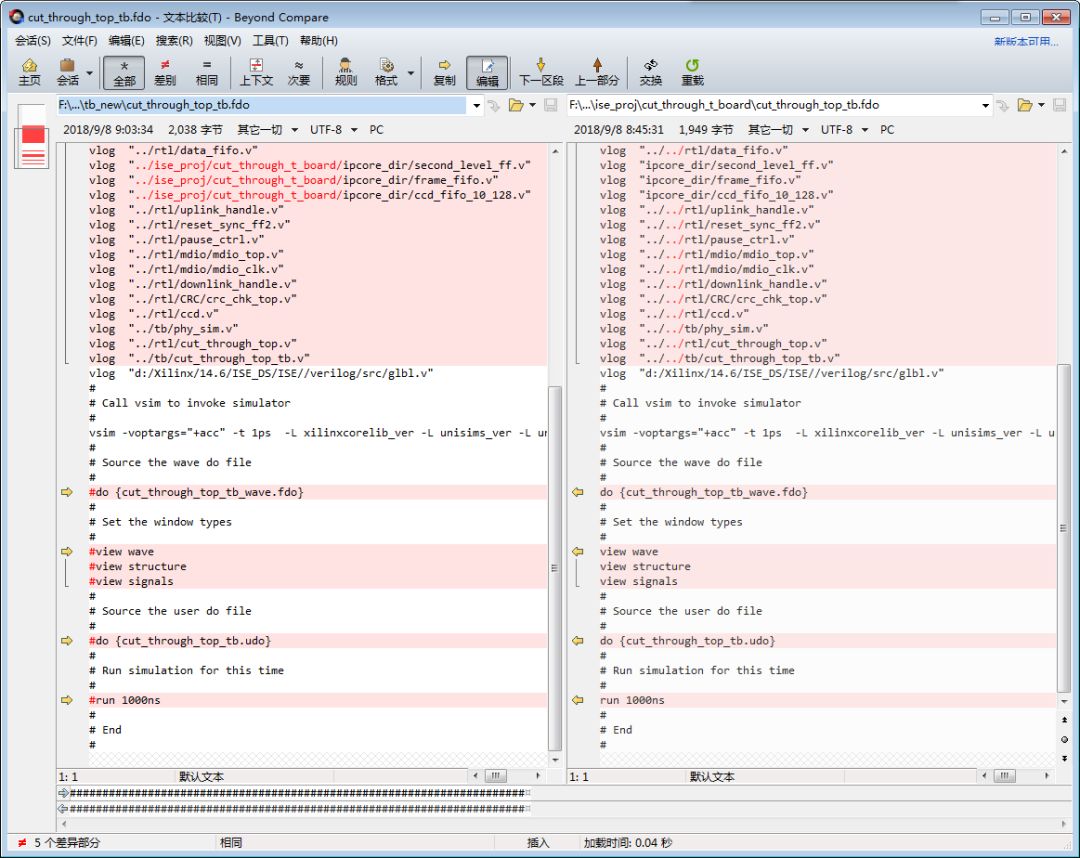

2、将cut_through_top_tb.fdo中的路径修改为绝对路径或者是相对tb_new目录下的modelsim工程的相对路径。

后续的查看波形的命令,我选择注释掉。

这样子可以很方便的自主操作。

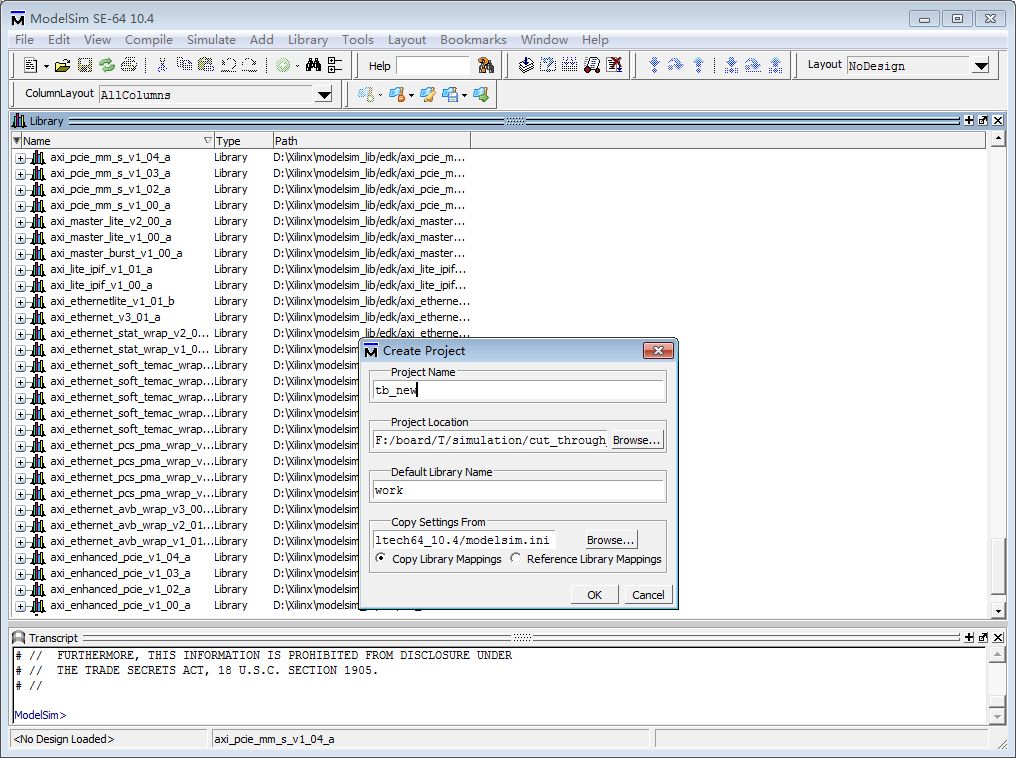

3、启动modelsim,新建工程,在Project_location选步骤1新建的文件夹tb_new

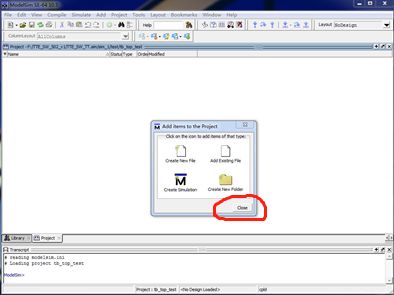

4、点击close,关闭窗口。

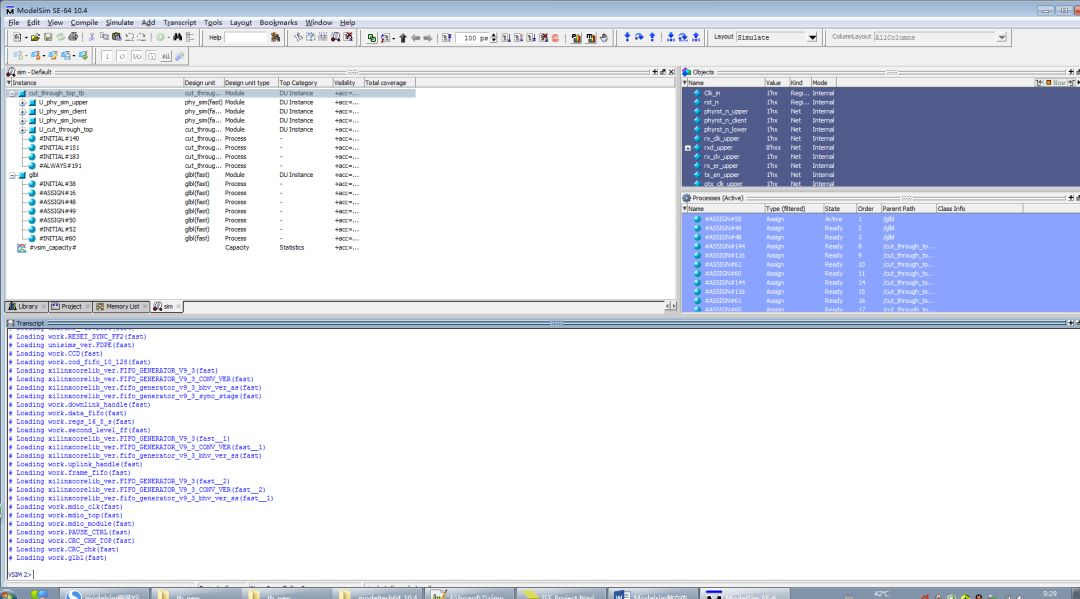

5、在命令行里输入do cut_through_top_tb.fdo,运行,即可看到编译等过程。

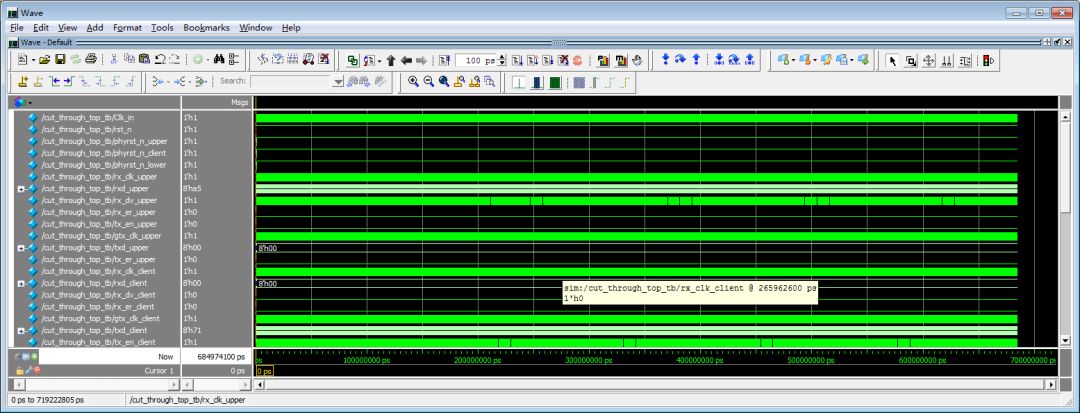

6、添加波形信号,run,就能看到仿真波形了。

遇到的问题

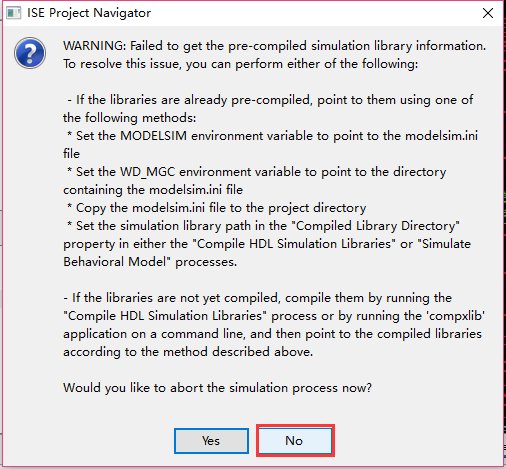

1、用ISE调用modelsim仿真可能出现这个问题:

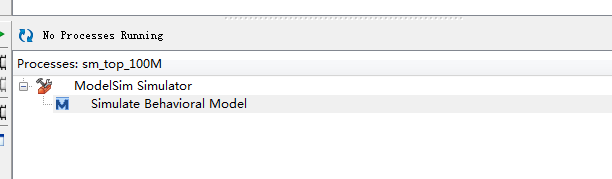

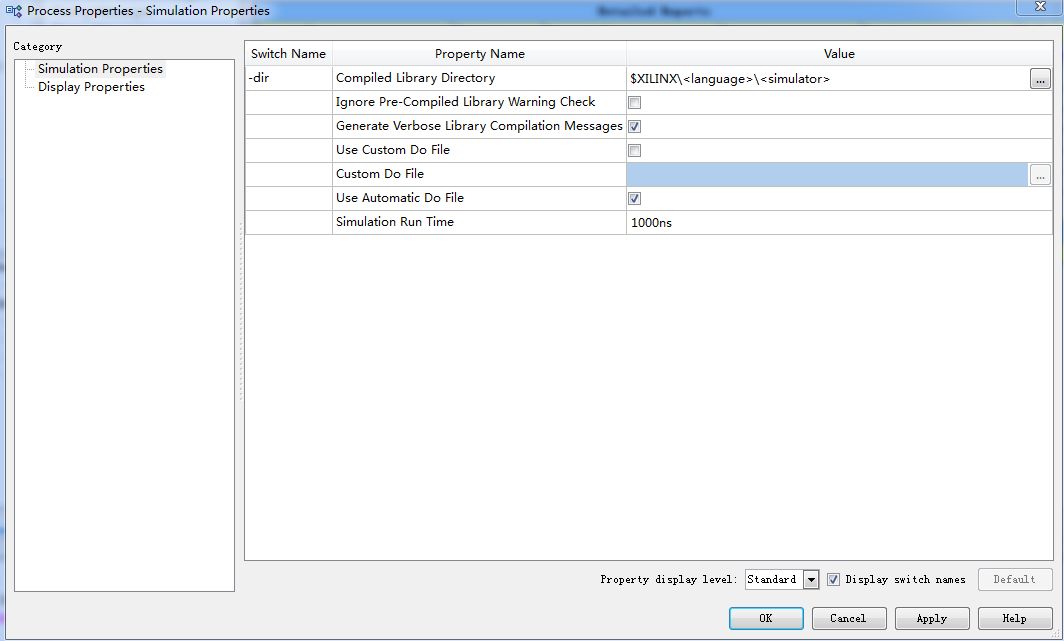

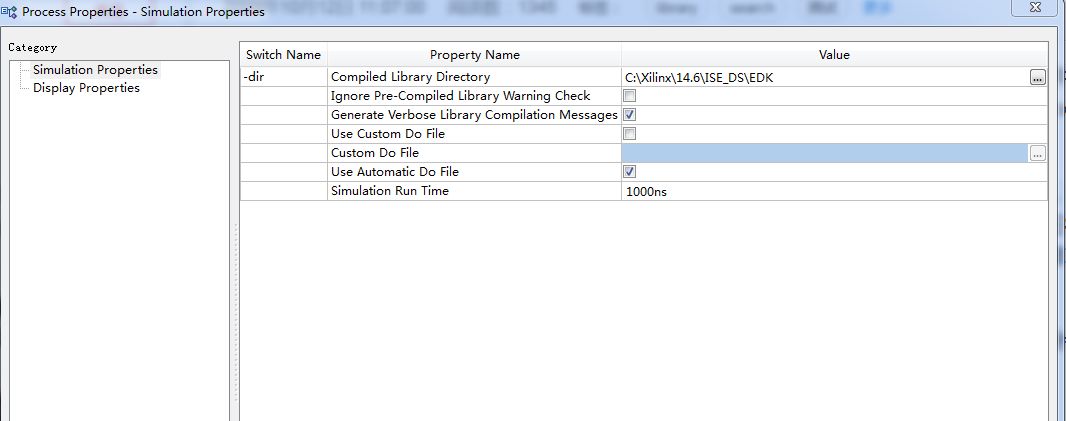

打开ISE工程,右击SimulateBehavioral Model

找到Compliled Library Directory

将路径改为ISE的库文件所在目录,然后就可以仿真了。

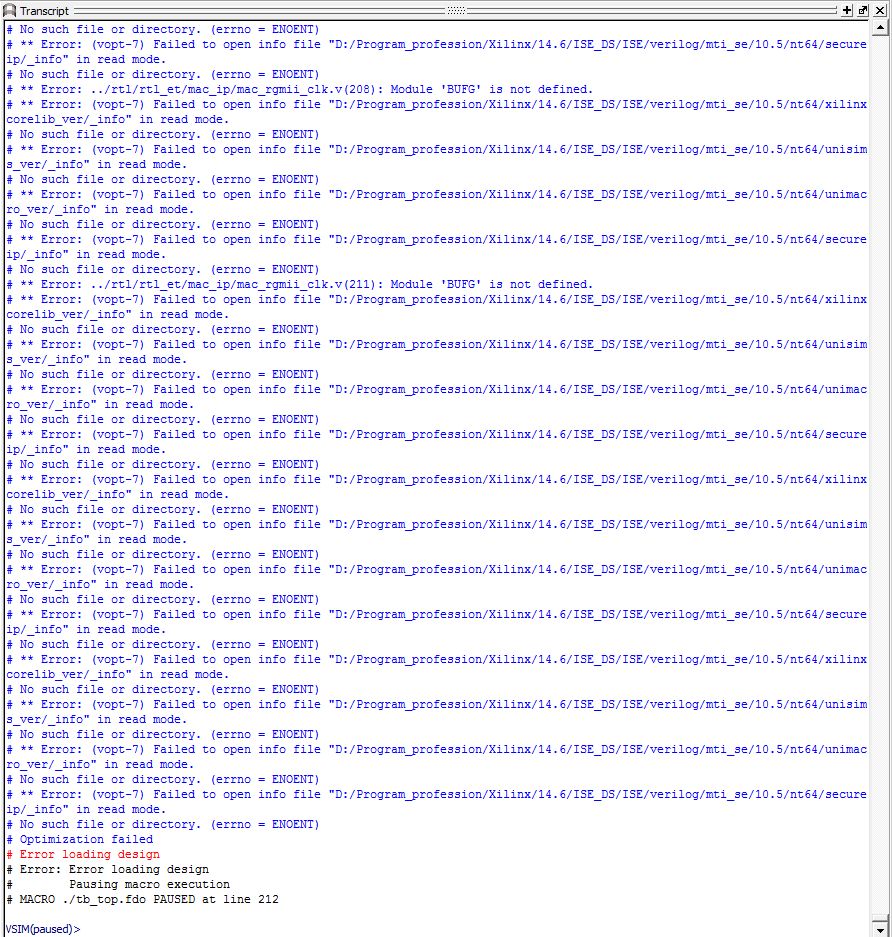

2、如果出现下图的问题,则把modelsim安装路径里的modelsim.ini拷贝到工程目录下就能解决。

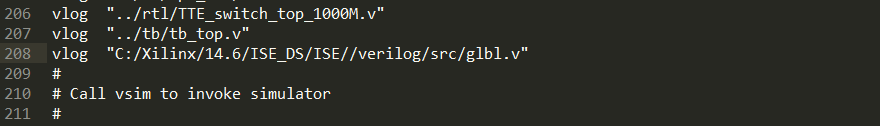

3、如果仿真时点击run等没反应,则打开tb_top.fdo文件(本文档的仿真工程为tb_top),把208行的路径修改之后就能运行了。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

429浏览量

28001 -

asic

+关注

关注

34文章

1269浏览量

124052 -

ModelSim

+关注

关注

5文章

174浏览量

48881 -

ISE

+关注

关注

1文章

103浏览量

38500 -

MODELSIM仿真

+关注

关注

0文章

15浏览量

7671

原文标题:如何用ModelSim 独立仿真ISE的仿真工程

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

介绍一种通过SystemC做RTL/C/C++联合仿真的方法

【转】基于ISE的仿真

关于ISE14.7联合modelsim仿真出现的问题

一种数模混合SoC 设计协同仿真的验证方法

一种数模混合SoC 设计协同仿真的验证方法

一种通信信号传输仿真的实现方法

减少Xilinx Ise与Modelsim联合仿真的错误方法

基于Xilinx ISE结合MATLAB对数字系统进行联合设计与仿真的方法设计详解

介绍一种ISE联合仿真转换为Moldelsim单独仿真的方法

介绍一种ISE联合仿真转换为Moldelsim单独仿真的方法

评论