高K介质 (High-k Dielectric)和替代金属栅 (RMG)工艺

2007年,Intel 公司宣布在 45nm CMOS 工艺节点上成功地使用高k氧化铪基(Hf-oxide Based)介质和金属栅工艺,可以显著减少栅介质泄漏电流和增加栅导电能力。

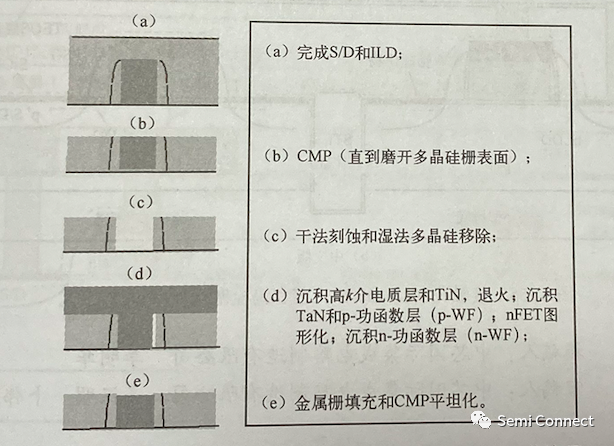

但高k氧化铪基栅介质较易被源漏退火步骤的热过程引起结晶化,导致较大的泄漏电流,因此高k介质金属栅模块工艺需要在源漏之后再形成,这被称为后栅(Gate Last)工艺或替代金属栅 ( Replacement Metal Gate, RMG)工艺,如图所示。

因此,高k介质(如 HfO2、HfSiOx、HfSiON)和金属栅(如TiN、TiAl、Al 或W等)模块便成为 32nm/28nmn 和更先进节点上的标准配备;后栅工艺或替代金属栅工艺也成为产业界先进 CMOS 工艺节点(28nm 节点之后)采用的主流工艺方案。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

6233浏览量

243389 -

AMOL

+关注

关注

0文章

2浏览量

8752 -

RMGI

+关注

关注

0文章

2浏览量

5500

原文标题:中段集成工艺(MOL Integration Flow)- 2

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

高k金属栅(HKMG)工艺详解

随着集成电路工艺技术不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低

什么是本体偏压/次临界漏电 (ISUBTH)/High-k

什么是本体偏压/次临界漏电 (ISUBTH)/High-k 电介质/High-k 电介质/GIDL

本体偏压通过改变电路上的电压来减少电流泄漏的技术。将电路

发表于 03-05 15:29

•868次阅读

高介电常数栅电介质/金属栅极的FA CMP技术

高介电常数栅电介质和金属栅极技术(以下简称HKMG)使摩尔定律在45/32纳米节点得以延续。目前的HKMG工艺有两种主流整合方案,分别是先栅

发表于 05-04 17:11

•8223次阅读

IMEC发布后栅极HKMG制式细节,英特尔、三星受益

电子发烧友网讯:纳米电子研究中心IMEC (Leuven, Belgium) 正评估用未来新型三极管替代金属栅极(RMG)技术和当前高K金属

发表于 06-14 11:45

•1916次阅读

现代集成电路芯片14nm节点FinFET的制造工艺流程详细资料说明

—LDD注入—侧墙主隔离—漏源极形成(应变硅技术)—金属硅化物—器件与金属间介质层ILD—置换高k金属

发表于 04-10 08:00

•161次下载

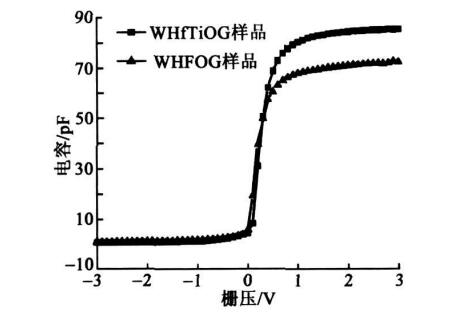

一文读懂HfTiO高栅介质GeMOS电容

采用反应磁控溅射方法和湿氮退火工艺在Ge衬底上分别制备了HfO2和HfTiO高介电常数(k)栅介质薄膜。电特性测量表明,HfTiO样品由于T

发表于 03-29 10:24

•27次下载

集成电路制造工艺的演进

为了提高晶体管性能,45nm/28nm以后的先进技术节点采用了高介电常数栅介质及金属栅极(High-k Metal Gate,HKMG)

高K金属栅工艺(HKMG)

目前,高K栅介质与金属栅极技术已广泛应用于 28mmn 以下高性能产品的制造,它在相同功耗情况下可以使集成电路的性能大幅度提高,泄漏电流大幅

高k栅介质NMOSFET远程声子散射对沟道迁移率的影响

器件沟道长度为1μm,HFO2栅介质厚度为4.88nm;SiO2栅介质厚度为2nm;P衬底掺杂浓度4E15cm^-3;栅电极为铝

发表于 07-05 16:45

•1646次阅读

High-k栅极堆叠技术的介绍

的尺寸持续缩减,二氧化硅层的厚度也相应变薄,这引发了严重的漏电问题,进而影响了元件的性能表现和功耗效率。High-k栅极堆叠技术则通过引入具备高介电常数的材料,对传统二氧化硅栅极绝缘层进行了革新性替代。

集成电路新突破:HKMG工艺引领性能革命

随着集成电路技术的飞速发展,器件尺寸不断缩小,性能不断提升。然而,这种缩小也带来了一系列挑战,如栅极漏电流增加、多晶硅栅耗尽效应等。为了应对这些挑战,业界开发出了高K金属栅(

高K介质(High-k Dielectric)和替代金属栅(RMG)工艺介绍

高K介质(High-k Dielectric)和替代金属栅(RMG)工艺介绍

评论