锁相环,顾名思义,基本功能是实现交流信号相位的跟踪和锁定。在交流变换器中,为了实现变换器有功功率和无功功率的输出的可控,需要实时获取交流侧的电压相位信息。锁相环的性能也是直接影响到变换器的稳定性。

从实现方式上,分为软件锁相环和硬件锁相环,从应用场合上又主要分为单相锁相环和三相锁相环。本文主要介绍软件的锁相方案。

过零锁相

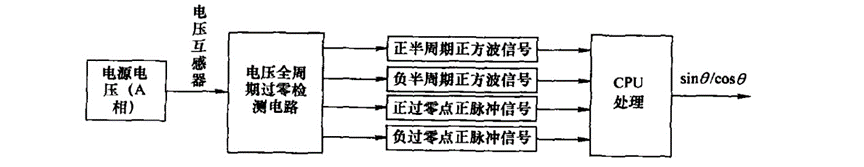

过零锁相是一种简单的开环的锁相技术,基本原理是通过实时检测网侧电压的过零点和频率信息来跟踪电网的相位,进位实现锁相。原理图如下所示

在实际应用中,可以使用互感器,也可以直接用分压电阻获取交流信号。这里面比较重要的就是过零检测电路,个人认为比较好的方案还是使用运算放大器组成一个比较器来实现过零比较。检测电路输出端接到单片机,利用输入捕获功能,通过读取定时器的计数值即可知道相位。

闭环锁相

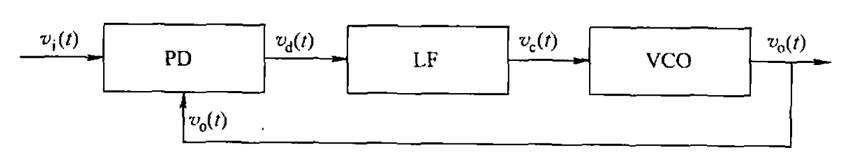

乘法鉴相法是比较基本的闭环锁相法。其控制回路一般由鉴相器(PD)、环路滤波器(LF)和压强振荡器(VCO)组成,如下图所示:

其中鉴相器采用乘法器,将输入信号vi和输出信号vo进行相位比较从而输出误差电压vd。环路滤波器的作用是滤除误差电压中的二次谐波分量和噪声,以确保控制系统的稳定性。压强振荡器的作用是完成电压/频率的转换,即压强震荡器的输出信号频率与误差电压vd的大小成正比。

基于二阶广义积分的锁相环

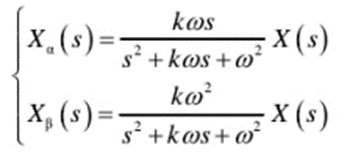

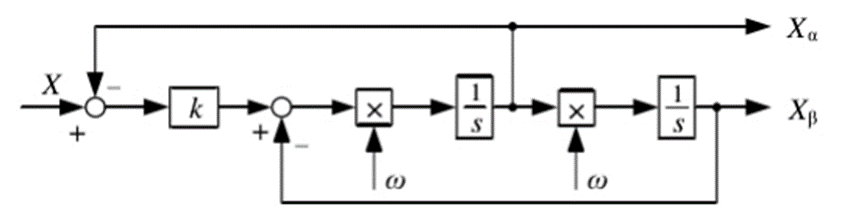

四分之一周期延时法、全通滤波器法以及微分法在构建虚拟正交分量的原 理,然而这些方法都存在一些问题,比如动态响应较慢、对电流谐波敏感、系 统稳定性差等。采用二阶广义积分(Second-orderGeneralized Integrator,以下简称 SOGI)法构建虚拟正交分量,SOGI 法结构简单,实现对输 入信号的 90°相角偏移时响应速度快,滤波性能好,可以改善系统稳态性能。 SOGI 法在 s 域的传递函数为

式中 k 为阻尼系数,是输入信号与反馈信号差值的放大系数,k值的大小 直接影响 SOGI 的性能,性能最优时取值为 k=1.57。ω 为 SOGI 的谐振频率,应与被跟踪的交流信号频率一致,SOGI 原理框图如下图所示:

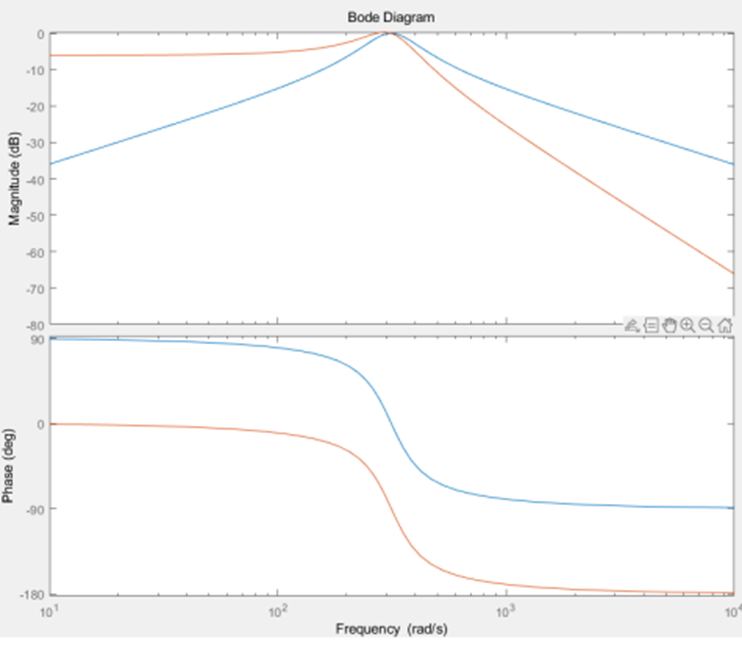

将上述的传递函数在 MATLAB 上画出伯德图,由图可得,系统对输入信号频率为 50HZ 的信号有很大的增益,对不等于 50HZ 的信 号有很好的削弱作用。同时可以看到,SOGI 输出的信号在相位上相差 90 度, 输出一对正交分量。

当控制系统开环传递函数中包含正弦信号的s 域模型时,可以使控制系统 在某一频率处的控制增益趋于无穷大,从而实现对频率为 ω 的给定正弦信号 的无静差跟踪。此外,由于系统只能跟踪相应频率的正弦信号,对其它频率的谐波信号起到滤波作用,所以系统与带通滤波器的作用效果是等效的,从而使系统具有更好的滤波性能。需要注意的是,当SOGI 的谐振频率与交流信号的 频率不相等的时候,SOGI 的输出就会存在跟踪误差。所以,SOGI 的谐振频 率需要跟随锁相环输出频率而变化。

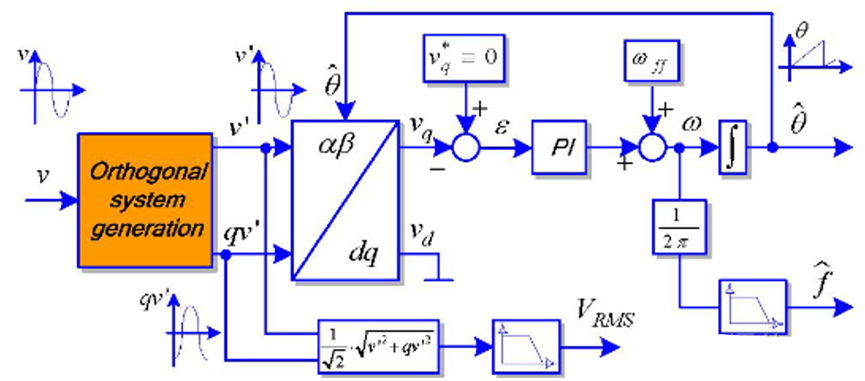

二阶广义积分只能产生正交向量,还需要将这组正交亮进行Park变换,然后将q轴的分量作为实际值,0为目标值进行PI运算,得到的结果与目标频率相加,就得到了相应的角频率,经过积分后就是正弦信号的角度,具体过程与三相的锁相过程相似。原理图如下图所示

三相电的锁相-单同步坐标系

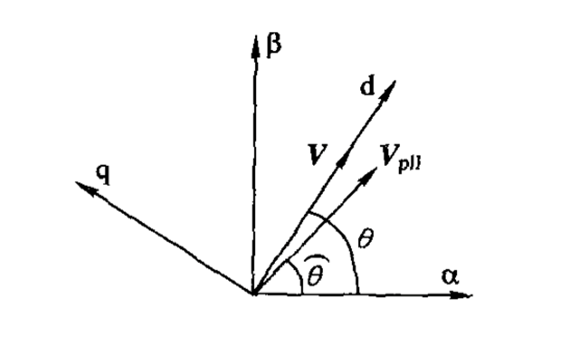

三相的锁相一般使用单同步坐标系的方法进行锁相,实际电压矢量以同步坐标系中的d轴定向,显然当锁相环准确锁相的时候Vpll应该和V是完全重合。如果没有重合,Vpll就会在d轴产生分量。

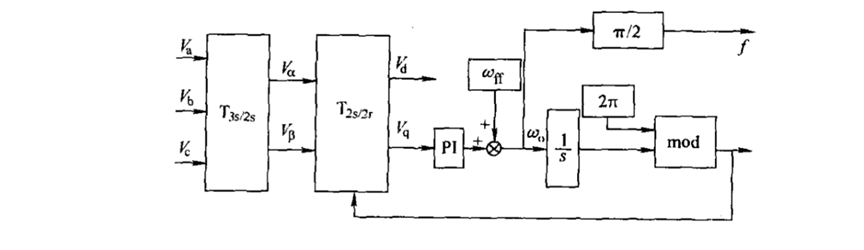

控制原理图如下图所示

这里没有把Vq与零做差,PI控制器的参数应该负的。

首先对电网电压进行Clark 变换( abc→αβ)和Park 变换( αβ--dq)变换,即将三相静止abc 坐标系的电压变量变换成两相同步旋转dq坐标系的电压变量,这种变换的优势在于能将三相静止abc坐标系的中正弦量变换成两相同步旋转d坐标系中的直流量。在同步旋转坐标系中,根据锁相环工作的基本性能要求,即必须使矢量Vpll、V完全重合才能实现相位锁定,显然只要通过闭环控制,使Vq=0即可实现锁相。实际上,在上图所示的结构中,将Vq输人PI调节器,当频率锁定时,Vq必为一直流量,由于PI调节器具有直流无静差调节特性,因此通过对Vq的PI调节,即可使Vq趋于零,从而实现锁相。而将PI调节器的输出与实际电网额定频率相叠加以获得锁相环的输出频率。

-

电能变换

+关注

关注

1文章

7浏览量

1374

发布评论请先 登录

高性能低噪声锁相环LTC6948:设计与应用全解析

Altera公司锁相环IP核介绍

探索CDC516:高性能3.3V锁相环时钟驱动器

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC509:高性能3.3V锁相环时钟驱动器

CDCVF2505 3.3 - V 时钟锁相环时钟驱动器:设计与应用指南

CDCVF25081:高性能锁相环时钟驱动器深度解析

TLC2932A高性能锁相环芯片详解:设计与应用指南

探索TLC2933A高性能锁相环:特性、应用与设计要点

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDCVF25081 3.3-V 锁相环时钟驱动器技术文档总结

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结

基于锁相环的无轴承同步磁阻电机无速度传感器检测技术

如何实现高效双向电能变换

高压放大器在锁相环稳定重复频率研究中的应用

电能变换--锁相环

电能变换--锁相环

评论