Microchip Technology FPGA 和基于 SoC 的 RISC-V 生态系统简介

介绍

RISC-V 是一种精简的 ISA(指令集架构),旨在为广泛的应用程序和用例提供可扩展性和多功能性。RISC-V 作为更成熟的指令集架构 (ISA) 的开源替代方案正在迅速获得认可,并提供更高的处理速度和更低的延迟,同时降低功耗。围绕 RISC-V 的支持框架也在不断发展,Microchip Technology正在构建生态系统以支持其 RISC-V 软计算机处理单元 (CPU) 和PolarFire ®片上系统 (SoC) FPGA产品组合。因此,基于 RISC-V 的设计具有更低的功耗、更高的灵活性、更快的上市时间,并提供 Linux 支持,而无需其他解决方案所需的折衷。

Microchip Technology Mi-V 生态系统

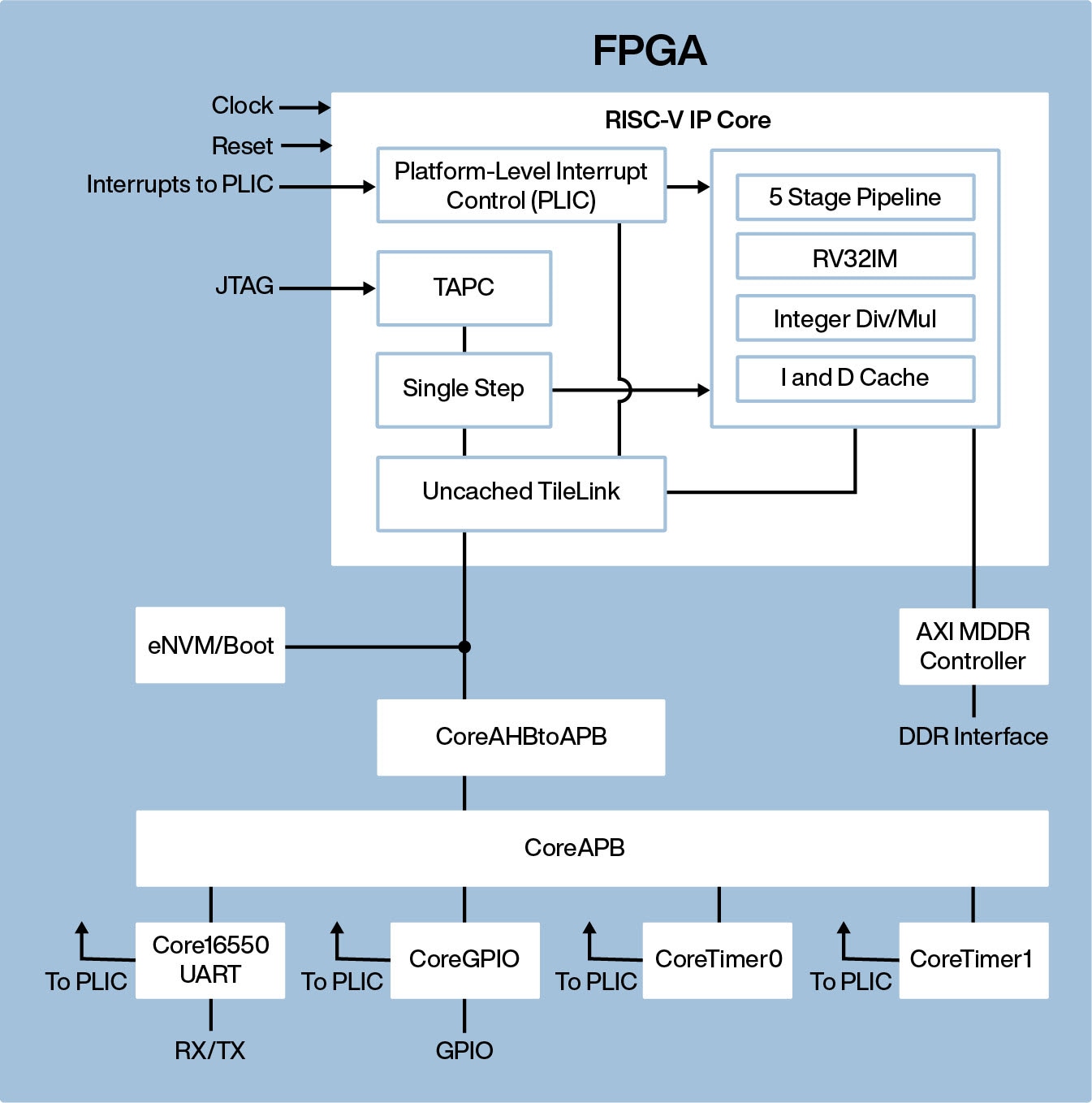

不断扩展的生态系统对于为开发人员提供完整的设计解决方案至关重要,这对于缩短产品上市时间至关重要。Microchip Mi-V 生态系统包括针对 FPGA 结构的软核 RISC-V CPU(图 1 )和在 PolarFire SoC FPGA 中实现的硬核 CPU。此外,Mi-V 还提供了由 Microchip 及其合作伙伴开发的一套广泛的设计工具和资源,以帮助开发人员采用和改进 RISC-V 应用程序设计。这些工具可与各种硬件套件结合使用——用于 PolarFire FPGA 的 PolarFire 评估套件和Icicle 套件PolarFire SoC FPGA——以及相关的 IP 和库,用于简化高速接口、数字信号处理、内存、电机控制,甚至嵌入式视觉的实施,以加速解决方案的开发。对实时 Linux 的支持是 Microchip Technology RISC-V 实施的重要优势,具有确定性执行,这对实时应用程序至关重要。Mi-V 还为范围广泛的开发工具和资源提供了多个第三方支持。

图 1:带有 RISC-V IP 内核的 FPGA(来源:Microchip Technology)

Microchip Technology 的 RISC-V CPU 产品组合

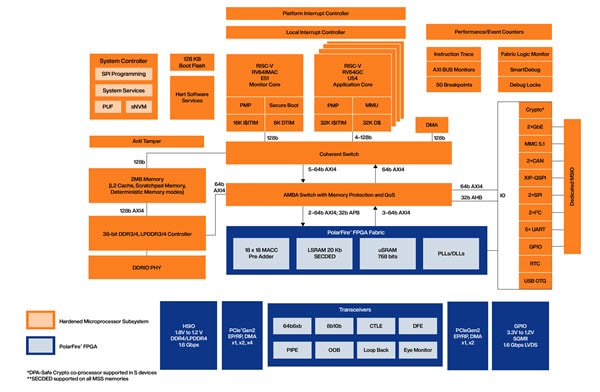

Microchip Technology 的 RISC-V 软 CPU 产品组合面向具有更低功耗和小尺寸的 FPGA 结构。当只需要一个 CPU 时,基于 FPGA 的实现可能是有利的。FPGA 实现还提供额外的灵活性和定制,包括在 CPU 附近添加专用硬件加速的选项。当需要多个 CPU 时,也许是在高可靠性或高性能应用中,PolarFire SoC FPGA 提供了五个强化 RISC-V 内核。这种支持 Linux 的 SoC 具有跨内核的一致性内存子系统和可配置的分支预测功能,允许在每次都按时执行的单个多核 CPU 集群中灵活地混合确定性实时系统和 Linux。Mi-V 生态系统中软 RISC-V 内核和硬内核的可用性使 Microchip Technology 产品组合成为业内最灵活的产品组合之一。硬核 CPU 实现的能效和 PolarFire FPGA 架构固有的低功耗特性确保 Microchip Technology RISC-V 解决方案在降低功耗方面处于领先地位(图 2)。

图 2:PolarFire SoC FPGA 框图(来源:Microchip Technology)

PolarFire SoC FPGA 扩展了 RISC-V 应用

大多数 FPGA 仅实现单个软处理器,但在单个 FPGA 上利用多个内核允许集群共享资源并分配计算负担。多核处理器已被证明能够比其前身更高效地执行复杂的功能和操作,例如内存计算和大规模并行。PolarFire SoC FPGA 系列基于 Microchip 著名的中端 PolarFire FPGA 架构,提供高端安全性,同时为各种应用降低高达 50% 的功耗。SoC FPGA 具有确定性 RISC-V CPU 集群和确定性 L2 内存子系统,用于 Linux 兼容性和其他实时应用程序,范围从 25k 到 460k LE(逻辑元素)。根据嵌入式微处理器基准联盟' s (EMBC) 基准评分系统 CoreMark——本质上是一个反映处理器内核整体功能的个位数——25k LE 系列中的 PolarFire SoC FPGA 在 105W 时提供 5.5 CoreMark,而基于 SRAM 的 SoC 使用相同的功率交付零 CoreMarks。100k 和 460k LE 范围内的 PolarFire SoC 在 CoreMark 规模上与竞争对手相比具有相似的优势。PolarFire SoC 是一种安全且节能的解决方案,适用于从人工智能 (AI) 和机器学习到汽车和工业实施(包括物联网和工业物联网 (IIoT))的各种应用。而使用相同功率的基于 SRAM 的 SoC 的 CoreMark 为零。100k 和 460k LE 范围内的 PolarFire SoC 在 CoreMark 规模上与竞争对手相比具有相似的优势。PolarFire SoC 是一种安全且节能的解决方案,适用于从人工智能 (AI) 和机器学习到汽车和工业实施(包括物联网和工业物联网 (IIoT))的各种应用。而使用相同功率的基于 SRAM 的 SoC 的 CoreMark 为零。100k 和 460k LE 范围内的 PolarFire SoC 在 CoreMark 规模上与竞争对手相比具有相似的优势。PolarFire SoC 是一种安全且节能的解决方案,适用于从人工智能 (AI) 和机器学习到汽车和工业实施(包括物联网和工业物联网 (IIoT))的各种应用。

MI-V 开发工具和设计支持资源

高效且易于使用的设计工具对于设计基于 RISC-V 的系统以及加快上市时间至关重要。Mi-V 生态系统包括用于使用 PolarFire FPGA 和 SoC FPGA 以及其他 FPGA 进行开发的 Librero SoC 设计套件。Mi-V 生态系统由基于 Eclipse 的 SoftConsole 集成开发环境 (IDE) 组成,并配有 GCC 编译器和调试器。Librero 和 SoftConsole 提供开发人员将 Microchip Technology 的 RISC-V 软 CPU 移植到 FPGA 以及测试和调试嵌入式固件所需的一切。

大量设计支持资源——包括教程、设计示例、数据表、功耗估算工具、白皮书、网络研讨会、视频、来自 GreenHills、Mentor 和 WindRiver 的操作系统、Yocto 和 Buildroot Linux BSP、Hart 软件服务、各种中间件和其他资源——完善 MI-V 生态系统并加快上市时间。

结论

RISC-V 是嵌入式计算的下一个前沿领域,而 Microchip Technology 在为应用程序设计人员开发完整解决方案方面处于领先地位。“Microchip 及其 Mi-V 合作伙伴推出业界首款基于 RISC-V 的 SoC FPGA 以及我们的 Mi-V 生态系统,正在推动嵌入式领域的创新,使设计人员能够开发全新的节能应用, ”Microchip Technology FPGA 业务部副总裁 Bruce Weyer 说。“反过来,这将使我们的客户能够在网络边缘为通信、国防、医疗和工业自动化添加前所未有的功能。”

审核编辑黄昊宇

-

FPGA

+关注

关注

1664文章

22503浏览量

639269 -

soc

+关注

关注

40文章

4624浏览量

230198 -

RISC-V

+关注

关注

49文章

2948浏览量

53550

发布评论请先 登录

直击玄铁RISC-V生态大会,看ALINX FPGA+RISC-V解决方案

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

新思科技邀您共赴2026玄铁RISC-V生态大会

2026丙午年 RISC-V 十大进展预测

高通收购Ventana Micro Systems,深化RISC-V CPU技术专长

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区

2025 RISC-V中国峰会 | 匠芯创SoC芯片引领工业应用新潮流

2025RISC-V中国峰会|进迭时空RISC-V AI CPU驱动智能化应用发展

RISC-V 图形领域的发展与挑战:从技术突破到消费端落地

RISC-V 在数据中心软件生态系统中的机遇与挑战

x264 的 RISC-V 生态构建与优化探索

RISC-V 工具链的版本更新、开发动态及生态建设愿景

RISC-V 发展态势与红帽系统适配进展

Microchip FPGA 和基于 SoC 的 RISC-V 生态系统简介

Microchip FPGA 和基于 SoC 的 RISC-V 生态系统简介

评论