为了可靠地捕获高频信号和快速瞬态脉冲,示波器和有源探头等宽带宽数据采集系统需要满足以下要求的高性能模拟前端(AFE)信号链:

(至少)支持1 VPP信号,以确保高信噪比。

支持直流到500MHz的高输入阻抗(高阻态),以防止加载待测器件。

提供低噪声和低失真,以保持高信号保真度。

提供高直流精度。

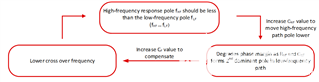

克服这些设计难题的一种方法是建立基于复合环路的方案,使低频和高频信号链交错,以获得直流精度和较宽的大信号带宽。

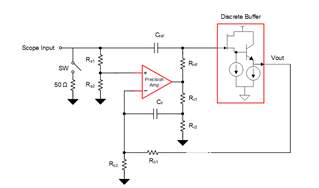

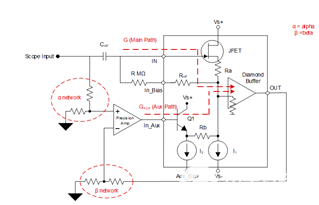

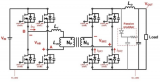

由于部署满足系统要求的基于复合环路的电路非常复杂,工程师通常需要设计定制的应用特定集成电路(ASIC)或使用多个分立式元件,如图1所示。这两种方案都存在弊端,包括需要专门的ASIC专业知识,同时还会增加设计复杂性。这两种方案还需要在性能和成本方面进行权衡:分立式实施比ASIC成本低,但不符合性能等级的要求。

图1:具有精密放大器模拟前端的分立式缓冲器复合环路

本文将探讨与全新BUF802 Hi-Z缓冲器单芯片实施相比,分立式缓冲器复合环路实施存在的设计难题。

分立式缓冲器复合环路架构

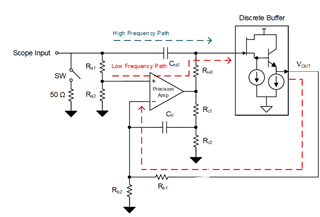

图1中Hi-Z AFE的分立式实施使用在复合环路中配置的精密放大器和基于分立式结型场效应晶体管(JFET)的源极跟随器电路。环路将输入信号分离为低频和高频分量,通过两个不同的电路将两个分量传递到输出(传输功能),并将它们重新组合,呈现为净输出信号,如图2所示。

图2:分立式复合环路低频和高频路径

低频路径提供了网络转输功能良好的直流精度,而基于JFET源极跟随器的高频路径为网络传输功能提供了较宽的大信号带宽以及低噪声和低失真。图2所示电路的一个主要难题是实现两条路径的顺利交错,以确保平坦的频率响应。两条路径的传输功能中的任何不匹配都将导致网络传输功能频率响应中断,从而丧失信号保真度。

复合环路架构的目标

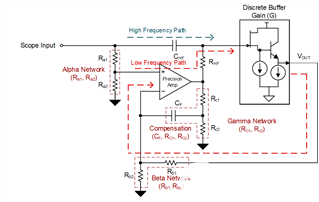

在直流或低频下,CHF(高频电容器)处于开路状态,电压输出(VOUT)由低频路径中的精密放大器控制。α和β电阻网络之比可控制直流或低频增益。

在高频下,由于增益带宽产品的限制,CHF短路和精密放大器会用尽带宽。分立式缓冲器充当JFET源,负-正-负发射极跟随器确定VOUT。在图3中,分立式缓冲器级称为增益(G),用于确定高频路径增益。

图3:分立式缓冲器复合环路架构

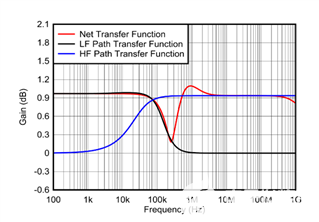

在中频下,由于低频和高频路径可确定输出,因此为了确保平坦的频率响应,请务必对极点和零点的单独增益和交互进行调优。由于具有相同的分量,中频下的增益均衡难以实现,CHF和RHF(高频电阻)将确定低频和高频路径的极点,如图4所示。

图4:分立式缓冲器频率响应

复合环路应具有平坦的频率响应和较高的交叉频率区域,以便降低1/f噪声并实现快速过驱恢复。

分立式实施的复杂性

由于低频路径和高频路径相互依赖(如图5所示),为实现平坦的频率响应,CHF和CF(补偿电容器)的值达到了数十纳法。但这些值致使交叉频率范围从几十赫兹达到几百赫兹,因而限制了信号链的直流噪声性能。

图5:低频和高频路径的相互依赖

以分立方式实施复合环路的另一难题是精密放大器开环增益的极点以及由RHF和CHF 组成的电阻器-电容器网络的极点会导致低频路径中形成双极点网络,从而导致不稳定。在精密放大器(图3中名为“γ网络”)上实施附加网络可以针对这种不稳定现象提供补偿,但为了实现更平坦的频率响应,还需要进行调优,这就导致在工作范围内建立平坦的频率响应时的复杂性进一步增加。

使用BUF802实施复合环路

实施分立式复合环路的主要限制之一是低频和高频路径之间相互依赖,并需要增加γ网络进行补偿,而TI的全新BUF802高阻态缓冲器在器件中内置了辅助路径。将精密放大器的输出连接到辅助路径会形成复合环路,同时可确保低频和高频路径之间相互隔离。隔离不同频率的路径可建立更高交叉频率的区域,并且无需γ网络和补偿电路。低频和高频信号分量在BUF802内部重新组合,在OUT引脚上重新呈现,如图6所示。

图6:具有内部BUF802的复合环路精密放大器

结语

BUF802等集成式Hi-Z缓冲器有助于解决基于复合环路实施的复杂难题。BUF802的集成保护功能(如输入/输出钳位)有助于保护信号链中的后续级,减少过驱恢复时间和输入电容,并提高系统可靠性。

考虑在当下应用场景中使用AFE时,您还必须考虑未来的测量需求,未来通常需要更高的带宽。BUF802具备的功能和优势可显著提高测量精度,确保系统设计投资可满足未来测试要求。

审核编辑 黄昊宇

-

缓冲器

+关注

关注

6文章

2236浏览量

49059

发布评论请先 登录

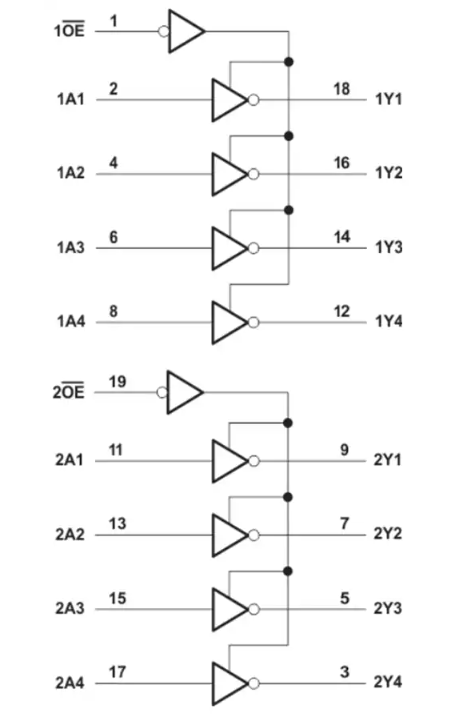

74AHC244:八进制缓冲器/线路驱动器的技术剖析

ISO782xLL 高性能隔离式双 LVDS 缓冲器:设计与应用全解析

探索LMV112:高速双时钟缓冲器的卓越性能与应用

深入解析ISO782xLL:高性能隔离式LVDS缓冲器的卓越之选

时钟缓冲器的应用场景及如何选择合适的时钟缓冲器?

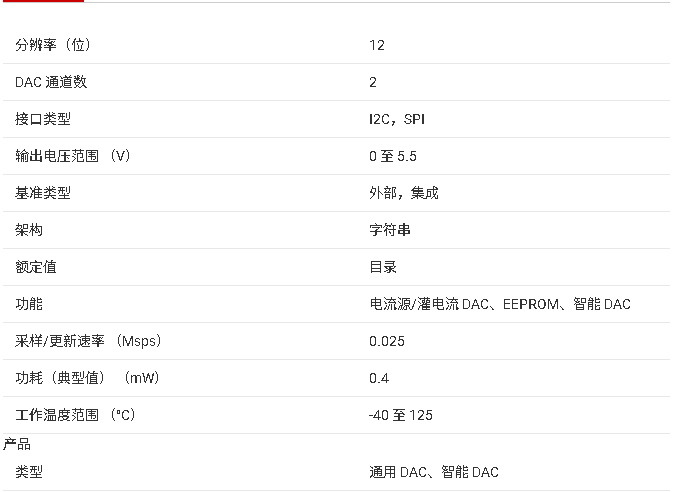

DAC63202W 智能数模转换器(DAC)技术总结

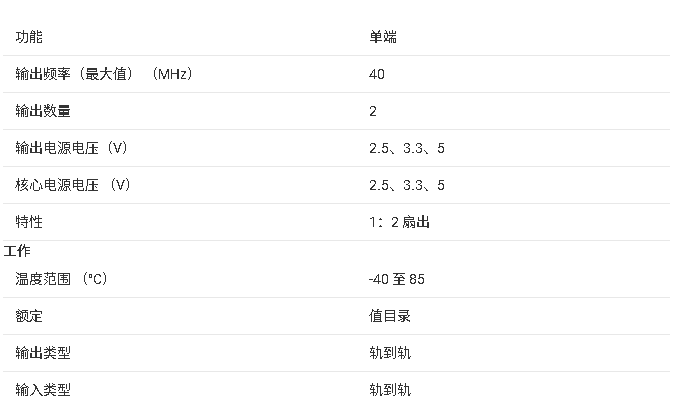

LMV112 40 MHz双时钟缓冲器技术文档总结

LMH2180 75 MHz双时钟缓冲器技术文档总结

浙江赛思电子时钟缓冲器的应用条件

Texas Instruments SN74ACT17六路缓冲器数据手册

Texas Instruments SN74LV8T240-EP八通道反相缓冲器/驱动器数据手册

集成式Hi-Z缓冲器助力于解决复合环路实施的复杂难题

集成式Hi-Z缓冲器助力于解决复合环路实施的复杂难题

评论