近年来,扩频通信技术在移动通信、个人通信、室内无线通信以及卫星通信中得到越来越广泛的应用。对于DS-CDMA(Direct Sequence-Code Division MulTIple Access,直接序列-码分多址)移动通信系统,因其具有较好的抗干扰性能而成为军事通信、民用通信以及宇宙通信的一种重要的通信体制。扩频通信的一项关键技术是扩频信号的设计,以及对它的捕捉和跟踪。在DS-CDMA移动通信中,也正是利用扩频码来实现用户多址,从而使多用户能同时共享同一频带进行通信。

在扩频通信中,通常在伪随机序列(Pseudo-random Noise,PN)的基础上产生扩频码。然而,扩频码(PN序列)的生成一直是通信工程师最关心的问题之一。随着FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)技术的发展,很多人采用FPGA来实现PN序列发生器。通常情况下应用FPGA来实现PN码生成器所采用的方法是利用触发器及逻辑门来组成线性反馈移位寄存器,从而产生所需的PN序列。然而这种方法会占用大量的触发器资源,不利于缩小芯片面积及制造成本。SRL16 E是Xilinx公司Virtex II等系列FPGA的Slice中的基本单元,应用它来实现PN码生成器可以大大降低FPGA中专用触发器的使用量,从而减少FPGA片上面积的占用。

基本原理

PN码生成器的核心是LFSR(LinearFeedback Shift Regisiter,线性反馈移位寄存器),LFSR序列共有(2N-1)种状态(其中N为LFSR中寄存器的个数),寄存器中的数据在每个触发时钟周期右移一位。反馈由预先确定的寄存器引出,共同经过异或逻辑后,加到LFSR的左端。通常寄存器的个数越多生成的PN序列的长度就越长,其中生成的最长的序列成为M序列。

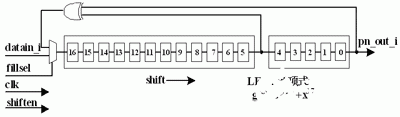

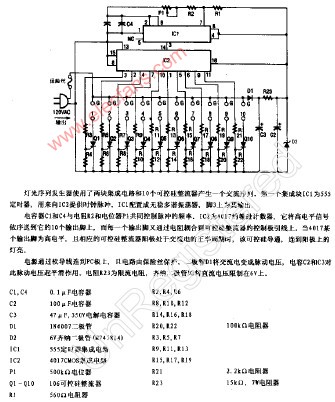

要实现LFSR序列的填充,需要在LFSR的反馈路径中加入一个多路复用器,利用这个多路复用器将实现期望的状态加载进去。需要注意的是在用一个特定的序列来填充时必须事先知道合适新填充的第一位从LFSR中输出。新的填充序列必须在相同的时钟周期内加载到LFSR中,并且新序列的第一位必须在并行加载完成后的第一个时钟周期被移出。如图1所示PN码生成器的原理图,共有17种寄存状态。下面来看并行加载是如何实现的。如果一个并行加载发生在T=0时钟周期,那么在T=17时钟周期时,通过fillsel指示反馈加入。这时,移位寄存器包含反馈加入前的长度为17位原序列,这17位的原序列在反馈加入时并未受影响。在接下来的17个时钟周期(即从T=17到T=0),原序列被移出,新的序列被移出,在T=0周期,新的序列移入完毕,反馈路径被断开,并在下一个时钟周期开始驱动新序列的第一位。这样,就如同新序列在一个单个的时钟周期T=0被并行加载一样。

图1 PN码生成器的原理图

PN码生成器的实现

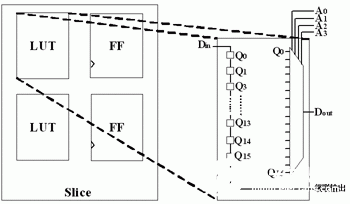

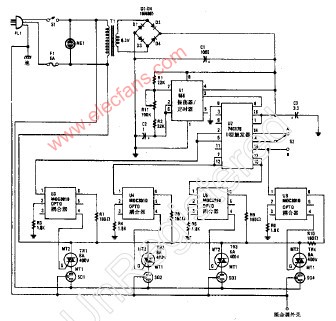

SRL16E是一种基于查找表的移位寄存器,可以非常方便地配置成多个触发器级联输出的形式,因此应用SRL16E来实现PN序列,是非常高效的,并且能够很大程度地减少FPGA资源的占用。原先SRL16E由于在配制时需要注册而被认为比ASIC(ApplicaTIon Specific Integrated Circuit,特定用途集成电路)开销更大。现在,它已成为FPGA中LUT(Look Up Table,查找表)配制模式的基本单元,可以非常方便地应用。并且这些基本单元在设计中应用得越多,那么设计所占用的专用触发器资源就越少。如图2所示为Xilinx公司Virtex II系列FPGA中的基本Slice结构示意图。

图2 Virtex II中的Slice结构示意图

应用SRL16E来实现LFSR时,一个Slice就可以生成一个16阶的LFSR,而用触发器来实现时,所用Slice的数量激增为16个。由此可见,应用SRL16E可以大大降低FPGA资源的占用。

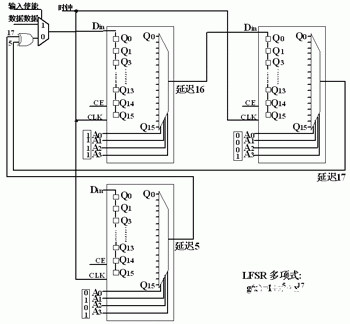

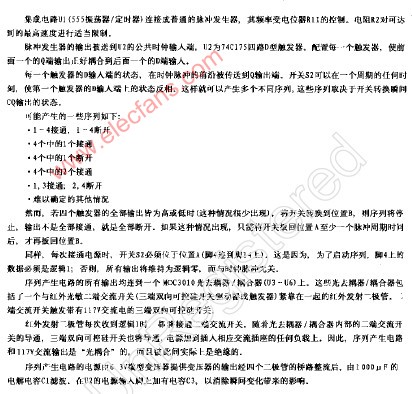

假设LFSR多项式为g(x)=1+x5+x17,即图1所示的PN码生成器,则应用SRL16E来实现PN码生成器的电路图如图3所示。

图3 SRL 16E构成PN码生成器的电路图

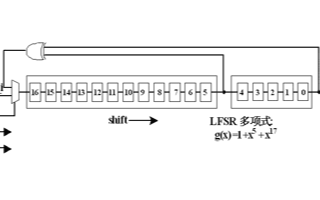

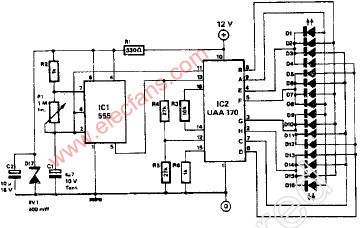

图4为以SRL16E为基本单元,使用ISE软件设计的PN码生成器所得到的模块图。其中输出pn_out_i对应的LFSR多项式为:

图4 PN码生成器模块图

输出pn_out_q对应的LSFR多项式为:

对于图4所示PN码生成器,我们应用ISE软件内嵌的XST(Xilinx Synthesis Technology)综合工具对其进行综合,得到的仿真波形如图5所示。

图5 PN码生成器的XST仿真波形图

根据ISE生成的综合报告可得到图4所示PN码生成器仅仅占用4个Xilinx公司Virtex II系列FPGA的基本Slice单元,可见应用SRL16E来设计PN码生成器可以非常有效地节省FPGA资源。

结论

应用SRL16E来实现PN码生成器的方法可以大大节省FPGA资源的占用量,并且由于SRL16E是被优化设计的模块,相较于传统的方法可提高所设计PN码生成器的效率。同时,SRL16E还可以用来实现滤波器、除法器以及波形发生器等,在大的系统中,例如整个CDMA系统,通过使用SRL16E可有效降低整个FPGA资源的占用量,从而使功耗及成本等得到进一步的降低。

-

FPGA

+关注

关注

1664文章

22503浏览量

639274 -

卫星通信

+关注

关注

12文章

850浏览量

40291 -

无线通信

+关注

关注

58文章

5099浏览量

147030 -

CDMA

+关注

关注

1文章

589浏览量

121424 -

发生器

+关注

关注

4文章

1432浏览量

64674

原文标题:基于FPGA实现PN序列发生器的设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于FPGA实现PN序列发生器的设计

基于FPGA技术的Logistic映射PN序列

【原创】基于FPGA的M序列发生器设计

FPGA的伪随机序列发生器设计

基于TDERCS伪随机序列发生器的FPGA设计与实现

如何使用FPGA实现混沌跳频序列发生器

序列发生器是什么_序列发生器设计步骤

基于FPGA实现PN序列发生器的设计

基于FPGA实现PN序列发生器的设计

评论