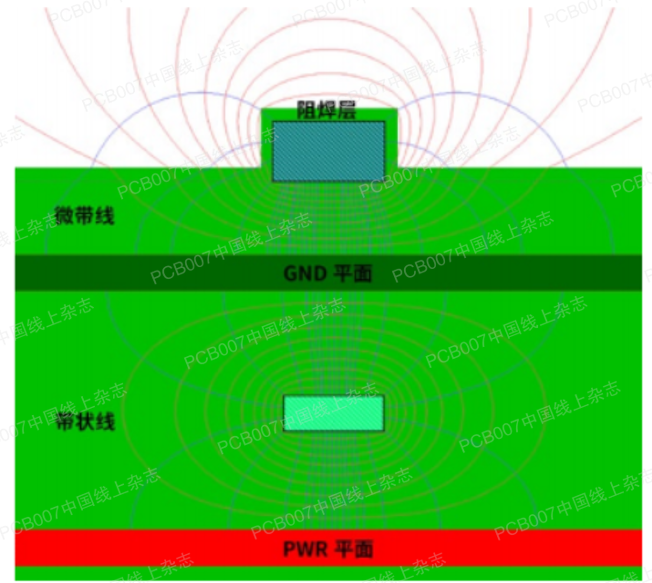

对于内部带状线层(图1),通过由平面之间的信号走线引导的多层PCB介质材料进行电磁(EM)能量传播,但它在外部微带层上的行为略有不同。微带层通常在一侧有完整接地平面,且允许辐射从无边无际的表面进入空气中。经过深思熟虑的布线策略可以避免高达10 dB的基板辐射。在平面之间嵌入信号可以降低对辐射的敏感性,并可提供静电放电保护。因此,不仅可以防止噪声辐射,还可以降低受到外部信号源影响的可能性。

图1:微带电磁场(顶部)和带状线电磁场(底部)

Hewlett-Packard进行的研究发现,与位于外层PCB中心的走线相比,位于PCB边缘走线的辐射要高20 dB。

然而,对埋嵌走线进行的相同测试表明,走线靠近PCB边缘时,辐射没有变化。这意味着在外部微带层布线时,最好远离PCB边缘。阻抗随着走线下方参考面面积的减小而变化。

在多层PCB上,为了减少辐射,关键信号应该布线在与实心参考面相邻的带状线层上。信号走线和返回平面之间的间距应尽可能小,以增加耦合并减少回路面积。

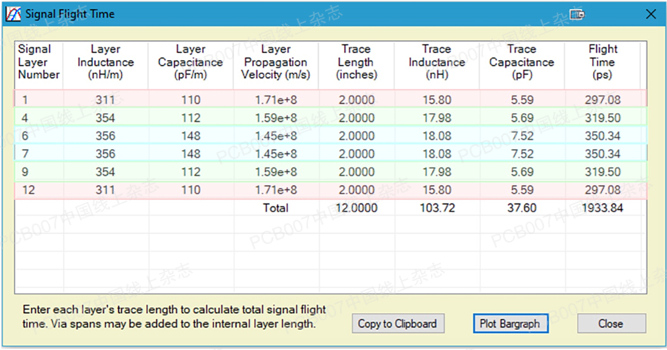

图2:微带线和带状线的相对信号传播(在iCD Design Integrity中模拟)

要牢记3个约束条件:

保持波形的信号与空号脉冲之比相等,因为这样可以消除所有偶数谐波。

在平面之间布线高速信号,在靠近下降到内层的驱动端(200mil)扇出,然后用短扇出再次布线回到负载端。

对返回信号使用相同的参考面(如果可能,使用GND),这样可减少回路面积,从而减少辐射。

微带线周围的电场一部分存在于介质材料中,一部分存在于周围空气中。由于空气的介电常数(Dk)为1,与带状线相比,它将加快信号传播速度。即使调整每层上的走线宽度,以便阻抗相同,微带线的传播速度总是会比带状线快13%~17%。数字信号的传播速度与走线几何形状及阻抗无关。

如果了解这个问题,为了补偿变化的走线延迟,就可以匹配飞行时间(如图2所示),以便在标称温度下,微带或带状线上运行的所有信号可同时到达接收端。或者,目前许多布线器都有匹配延迟布线功能,使设计师能够考虑微带线和带状线结构之间的飞行时间变化。注意,匹配延迟与不考虑飞行时间的匹配长度布线有很大不同。

例如,对于DDR3/4 Fly-by拓扑结构,最好在两个对称的成对层上布线所有关键走线。在本文的案例中,成对层是第1层和第12层、第4层和第9层,再加上第6层和第7层。第4层和第9层是最好的成对层,因为它们嵌入并靠近12层PCB的平面对和有源器件。从微带层到这些层(未显示)有200 mil扇出。这两层具有相同的延迟319.50 ps,并且在平面之间嵌入的堆叠对称。

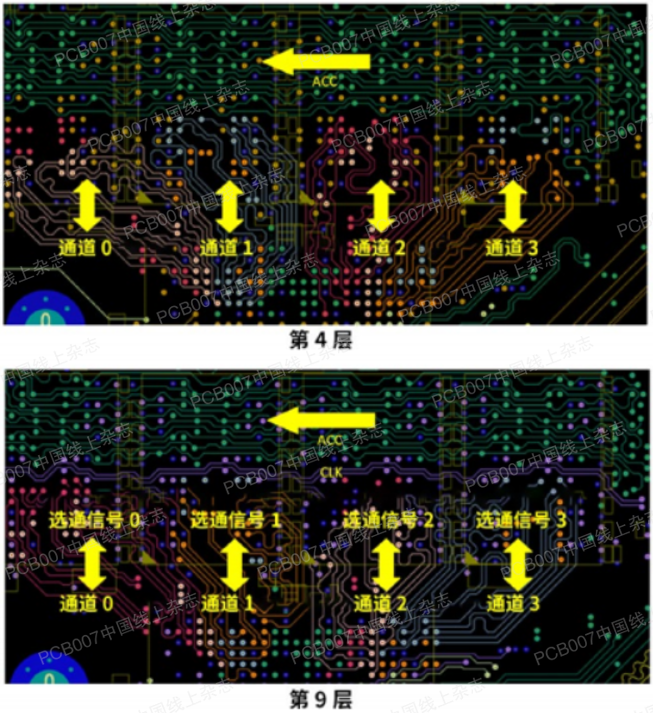

图3显示了数据通道(0—3)的布线方向与相关的差分选通信号相结合以及与差分时钟相结合的地址、控制和命令(address, control and command,简称ACC)信号。不需要担心层引起的飞行时间偏差,因为第4层和第9层是相同的。

图3:DDR3 Fly-by拓扑结构的布线策略

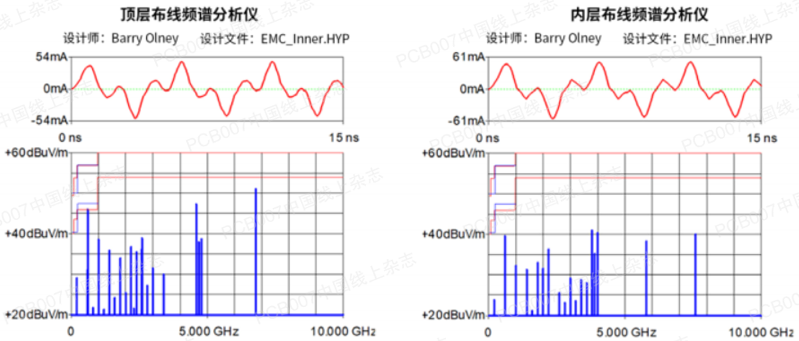

图4显示了外层和内层之间的相对辐射。在该案例中,在第4层内层布线的走线比在顶层布线的走线噪声低4~10 dB。注意,顶层布线上存在40 dB以上的辐射谐波。此外,高频元件更容易辐射,因为它们的波长较短,与用作天线的走线长度相当。因此,尽管谐波频率分量的振幅减小,但随着频率的增加,辐射频率会随着走线特性而变化。

图4:顶部微带层与内部带状线层布线信号的辐射对比

因此,除了较短的200 mil微带扇出外,这种设计的发射远低于FCC/CISPR B级限制(较低的红线)。然而,如果在外层布线,在6.76 GHz时辐射将为49.73 dB,在7.8 GHz时为52.10dB,可能无法通过测试。如果在开始布局之前规划布线策略和堆叠设计,那么电磁兼容性设计只需要很少的额外工作。

要点

在平面之间嵌入信号可减少这些发射和辐射敏感性,并可提供静电放电保护。

在外部微带层布线时,最好远离PCB边缘。

在多层PCB上,关键信号应在与实心参考面相邻的带状线层上布线,以减少辐射。

微带线的传播速度总是比带状线的传播速度快13%~17%。

目前,许多布线器都有匹配延迟的布线功能,使设计师能够考虑到飞行时间的变化。

在第4层内层上布线的走线比在顶层布线的走线噪声小4~10 dB。

审核编辑 :李倩

-

PCB设计

+关注

关注

396文章

4938浏览量

95744 -

电磁兼容性

+关注

关注

7文章

505浏览量

34752 -

电磁场

+关注

关注

0文章

806浏览量

49510

原文标题:PCB设计:使辐射最小化的布线策略

文章出处:【微信号:actSMTC,微信公众号:actSMTC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

微电网经济调度理论:成本最小化与效益最大化的优化模型

沃虎电子:塑料外壳ETH的PCB设计策略

浅谈晶振在PCB设计中的要点

PCB设计 | AI如何颠覆PCB设计?从手动布线到智能自动化的30年演进

PCB设计与打样的6大核心区别,看完少走3个月弯路!

人工智能数据中心的光纤布线策略

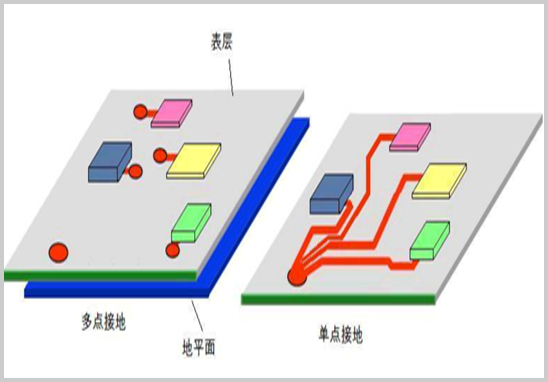

PCB设计中单点接地与多点接地的区别与设计要点

如何在PCB设计中优化MDD高压二极管布线?实现高压系统安全防护

PCB设计:使辐射最小化的布线策略

PCB设计:使辐射最小化的布线策略

评论