在实际的高速电路设计中,我们往往会需要将并行的一组线进行等长,我们希望并行通信的信号从源端出来同时到达终端,避免出现误码。

而在当今的EDA软件中,各自有各自的处理方法。而对于Allegro(以下简称A狗)中,也有这样一个功能,LowHuang觉得是非常棒的。下面介绍如何实现这一功能。

一,建立等长群组

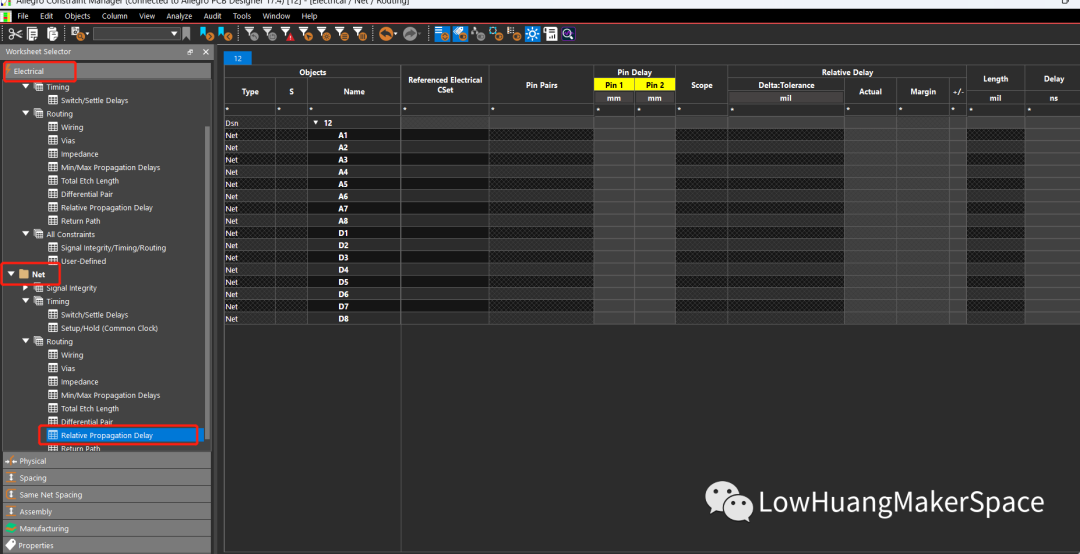

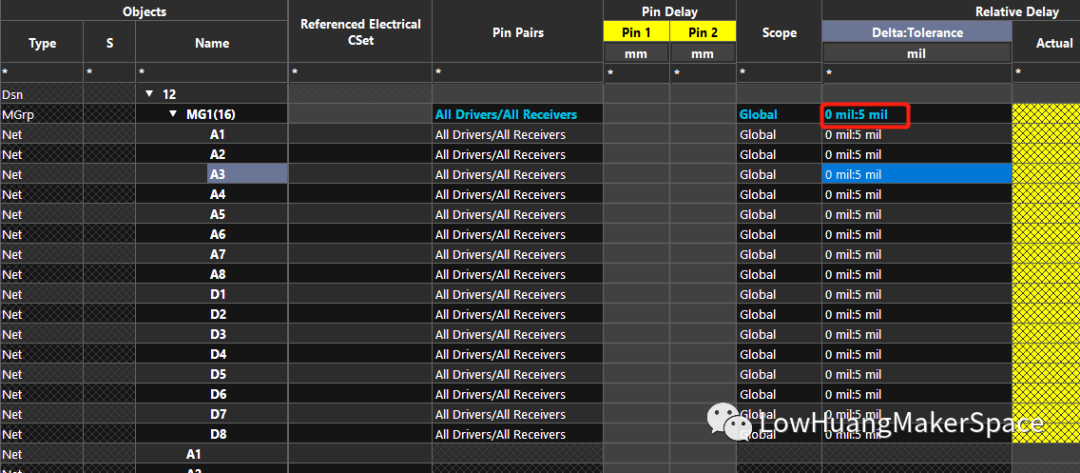

在这里我们说的等长是相对等长,因此我们要用到RelativePropagationDelay这个规则

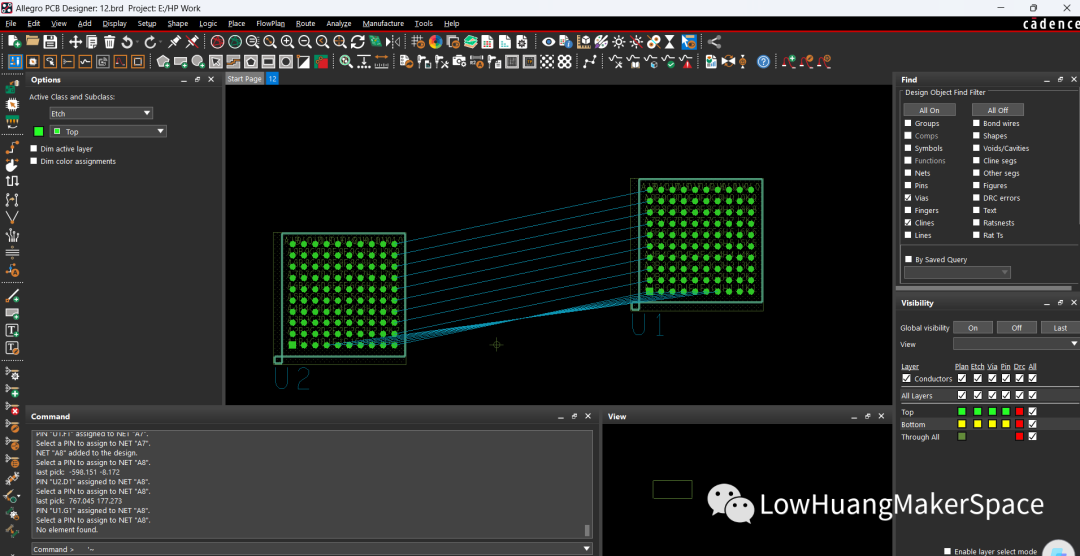

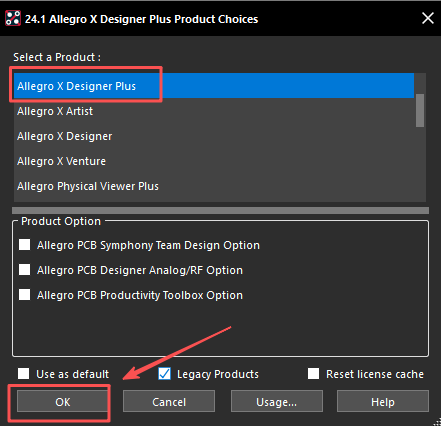

打开A狗--Setup-->Constraint Manager

选择Electrical->Net->RelativePropagation Delay

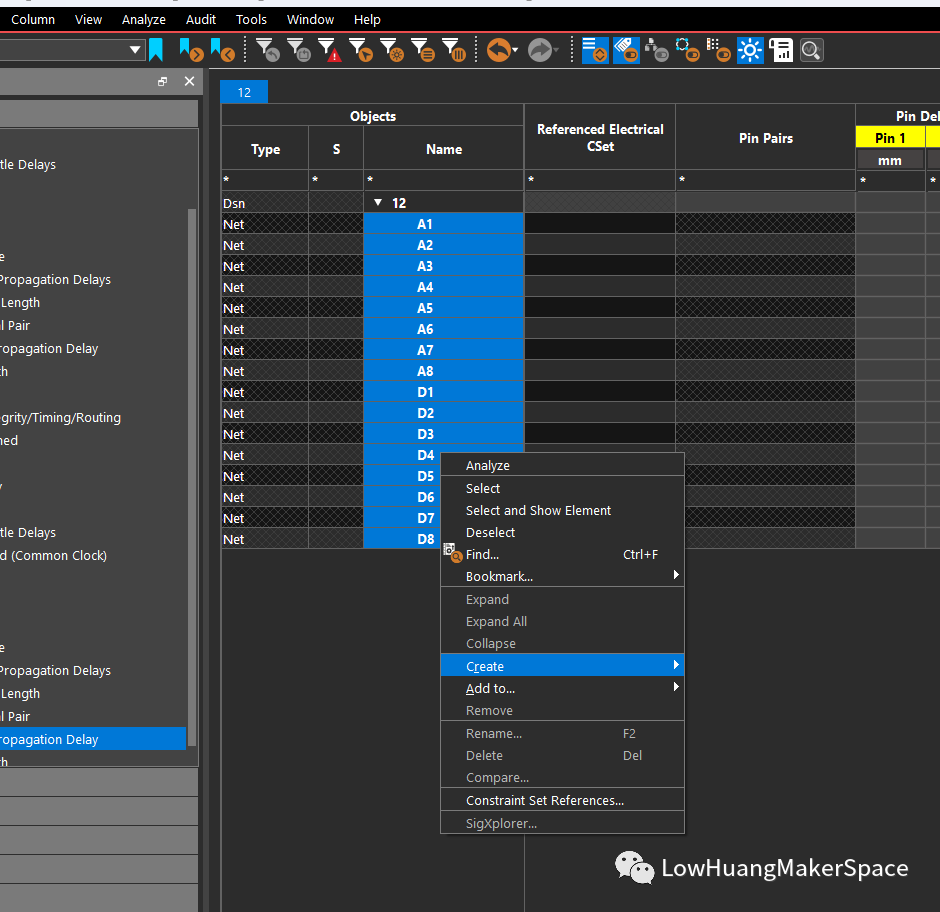

在右边的表格中,我们选择要做等长的网络按SHIFT+单击

选中后右击->Create->MatchGroup

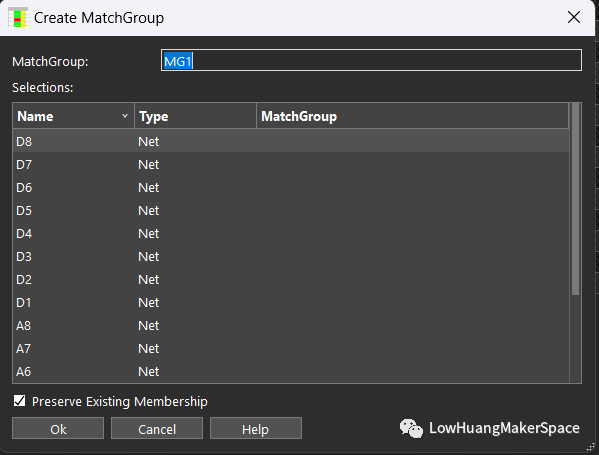

给网络群组取个名字点OK

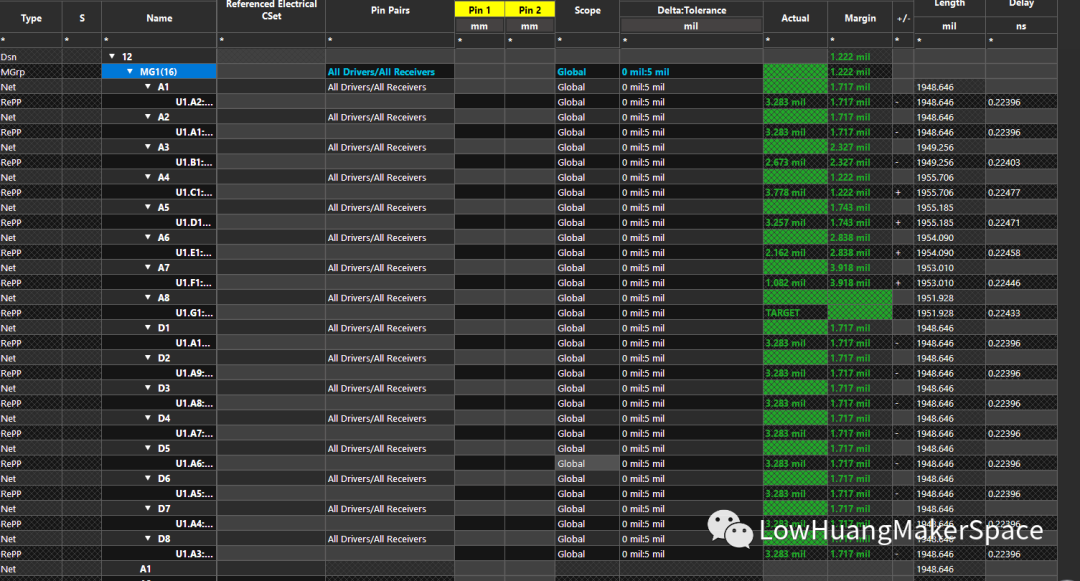

创建完成后这里会多了一个MatchGroup,我们在Delta:Tolerance设计等长群组内允许的误差值,在这里我们设为5Mil

设置完成后关闭ConstraintManager

二,自动延时调整

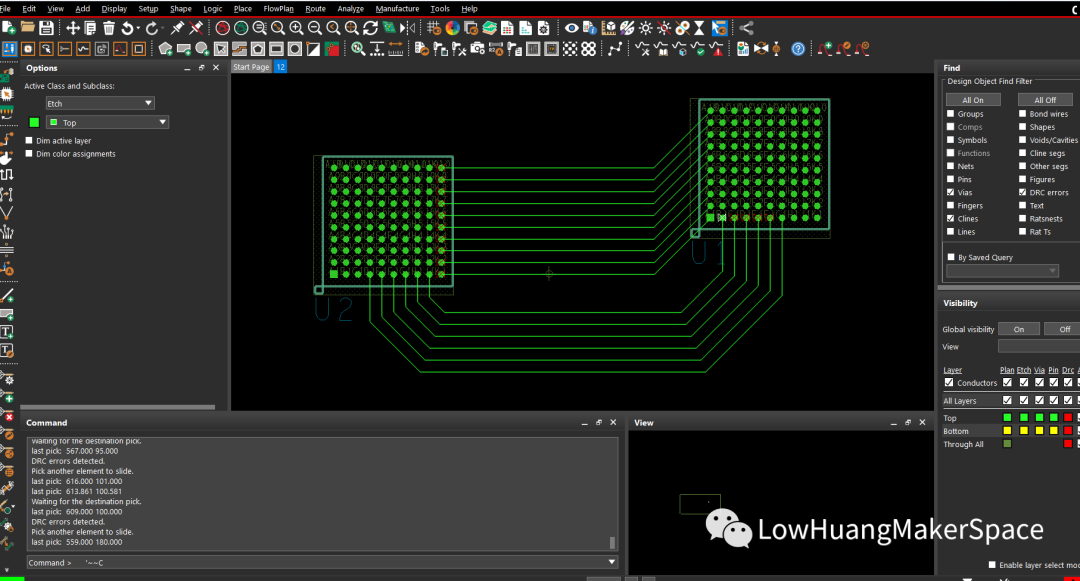

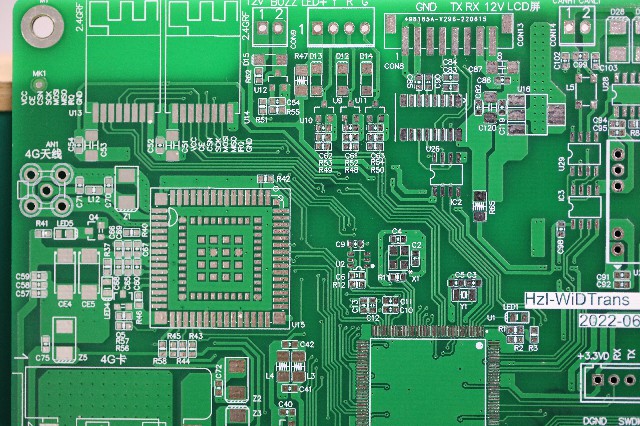

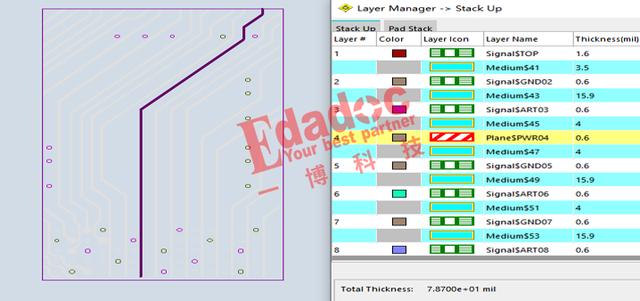

回到Allegro中,先将线拉通,拉线的同时我们对于比较短的线尽量留大线间距,因为后面软件会以最长的为参考,短的线需要绕线

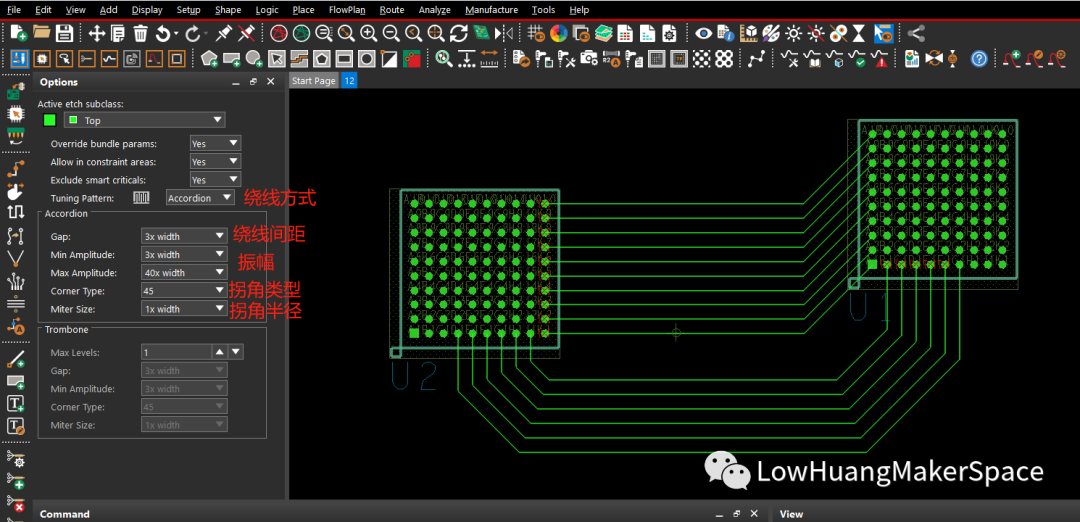

选择Router-->Auto interactive delay tune 设置左边的参数

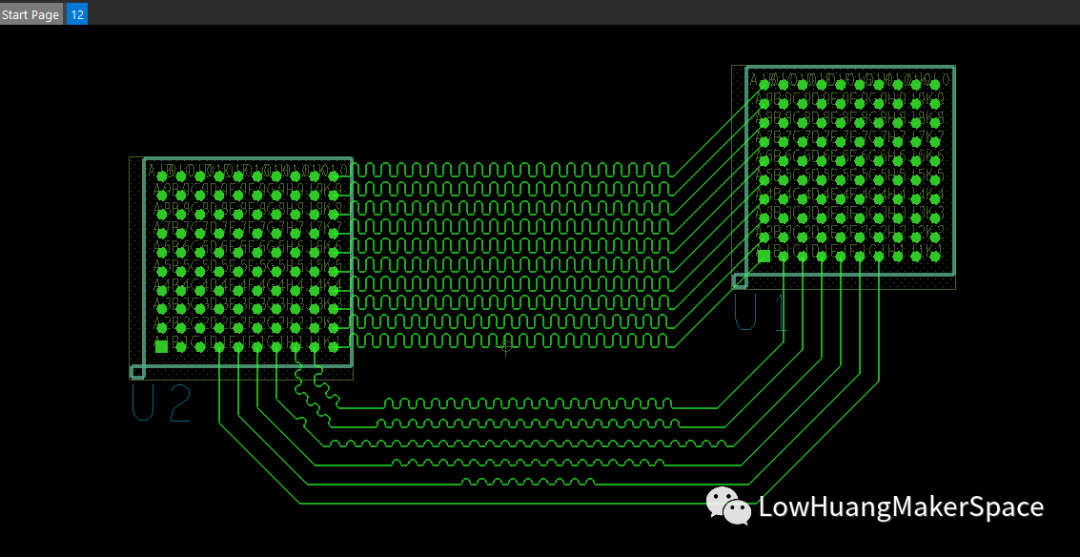

设置完成后选择需要调整的网络即MatchGroup的所有网络 自动调整后效果如下

从图中可以看出,最外的线是最长的,我们没手动设置最外面那边线为参考线,软件会自动以最长的那条为参考,调整其他线。

我们再次打开Setup-->ConstraintManager

选择我们建的MatchGroup右键--》Analyze分析下是否 满足我们设置的条件红色的表示满足条件

都满足条件!

完结 如有不对之处 请指出

如果觉得好 把Lowhuang推荐给你身边的朋友吧

审核编辑:汤梓红

-

allegro

+关注

关注

42文章

773浏览量

150511 -

高速电路

+关注

关注

8文章

170浏览量

24918

原文标题:Allegro应用技巧--自动走线延时调整

文章出处:【微信号:LowHuangMakerSpace,微信公众号:LowHuangMakerSpace】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

05. 如何在 Allegro 中沿着板子轮廓走线?| 芯巧Allegro PCB 设计小诀窍

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

PCB走线“粗、短、直”的根本原理

技术资讯 I Allegro PCB 设计中布线优化

AD7792电流源输出在走线时,如果走线过长,且走线很细10mil,会导致电流源大小衰减吗?

Allegro Skill布线功能之调整差分的线宽线距

Allegro应用技巧--自动走线延时调整

Allegro应用技巧--自动走线延时调整

评论