赛灵思和英特尔都在优先考虑数据中心,这正在推动可编程逻辑研发向高性能插座发展。在某些情况下,这些趋势也影响了嵌入式电子领域应用的发展。但是,对于无数的应用,功耗和散热与性能一样重要,如果不是更重要的话。这些用例通常位于边缘,涵盖从传感器集线器到显示控制器再到图像处理和 AI 推理平台的所有内容。

是的,开发这些解决方案的应用工程师、OEM 和集成商需要提高性能并增加工作负载的多功能性。但它们也需要保持在成本、功耗和热限制范围内。

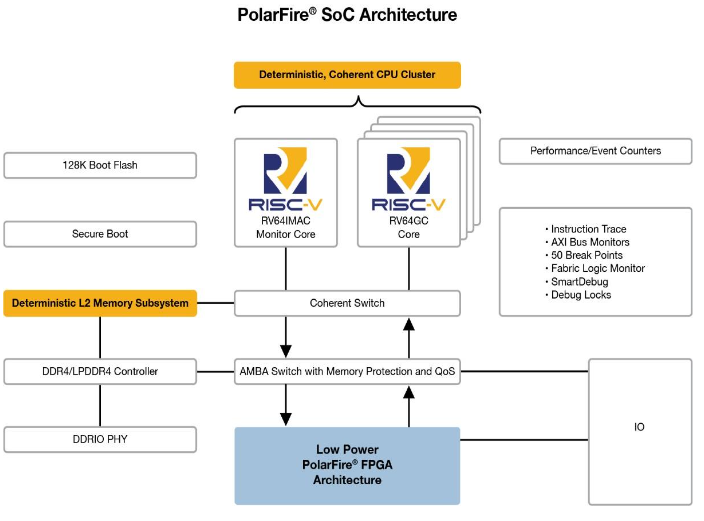

出于这个原因,Microchip继续在其PolarFire FPGA SoC系列中进行创新 - 最近的MPFS025 SoC具有25K逻辑元件和硬化的四核RISC-V CPU。

据该公司称,MPFS025 SoC提供:

功耗比竞争性 SRAM FPGA SoC 产品低 50%

300 MHz 结构和 450 MHz DSP 流水线,可实现领先的 4K60 传输和处理效率

4 个多速率、多协议 12.7 Gbps 收发器

植根于加密控制的供应链的强大 IP 保护

高效的可编程性能

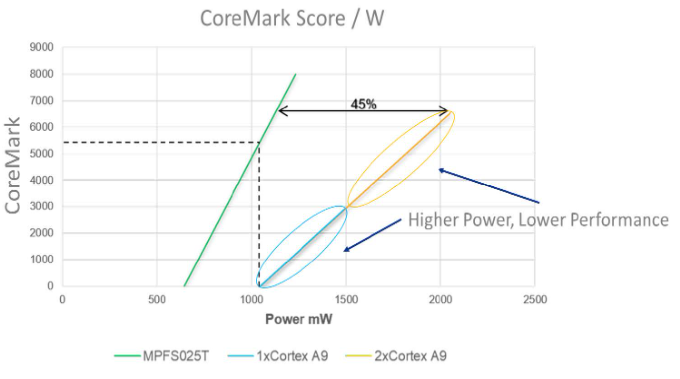

尽管具有性能和安全优势,但Microchip的MPFS025 PolarFire FPGA SoC的效率是最重要的。如下图所示,CoreMark 得分为 5200,功率仅为 1.2 W。

这要归功于主RISC-V RV64GC内核上的32个整数和32个浮点寄存器,以及组织成18 x 18 MACC的68个数学模块。这些查找表是可分馏的,这意味着它们可以减少到两个9x9,因此计算可以优化到不同的位分辨率。

为什么这种效率水平很重要,真的?显而易见的答案是,任何具有固有功耗敏感性的系统设计都将受益。但更深入地考虑,更高的性能通常意味着更高的频率和电压到更多的电路,这会导致产生过多的热量。

Microchip的FPGA产品营销总监Tim Morin表示,散热成本约为1.5美元/瓦,因此,如果能够以尽可能少的电路启动来最大限度地提高性能,则可以降低系统成本或将设计部署到更恶劣的环境中,或两者兼而有之。

RISC-V拯救嵌入式图像处理

但回到RISC-V。除了处理效率之外,片上RISC-V内核的另一个优势是,它们允许一般嵌入式工程师在基于可编程逻辑的器件上运行熟悉的Linux和/或RTOS。

一旦这些开发人员熟悉了使用Microchip Libero 设计套件 2021.2 版等软件工具在 FPGA SoC 上进行开发,他们将发现灵活的 2 MB 二级缓存和 LPDDR4 内存支持可供他们用于应用开发。

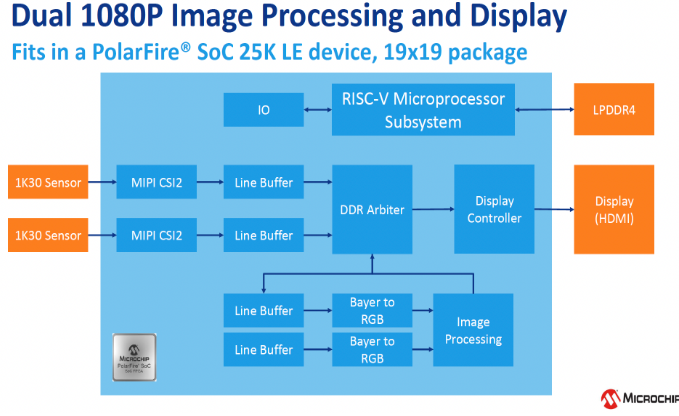

MPFS025 PolarFire FPGA SoC 的功能组合使其在嵌入式视觉系统设计中几乎即插即用。下图显示了位于图像处理流水线核心的SoC,要求工程师只需在前端集成传感器,在输出端集成外部存储器或显示器。

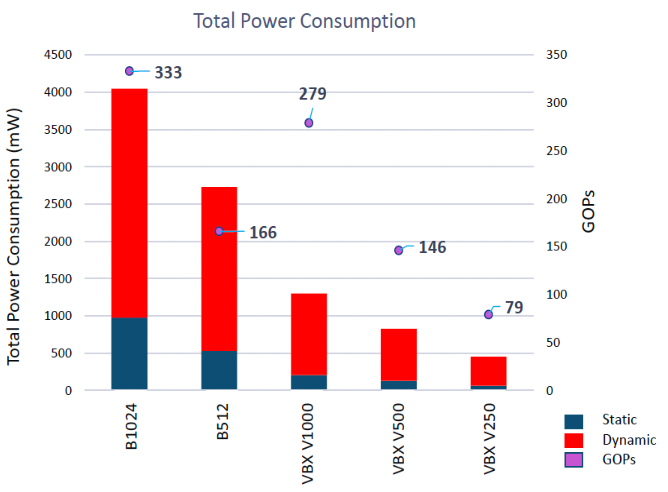

当然,开发人员希望增加更多的价值。在许多情况下,该值将在应用程序级别。为此,Microchip MPFS025 PolarFire FPGA SoC支持OpenVX等开放式开发框架以及VectorBlox加速器软件开发工具包(SDK)等更有针对性的解决方案。

VectorBlox SDK与可在Libero中访问的AI IP配对,以帮助没有机器学习经验的开发人员优化神经网络算法,如无快门补偿或图像增强,以便在PolarFire FPGA SoC上执行。VectorBlox/PolarFire FPGA SoC 组合可实现比其他解决方案高 2-3 倍的能效推理。

同样在工具方面,Microchip在2021年RISC-V峰会之前发布了智能嵌入式视觉平台。智能嵌入式视觉平台集成了RISC-V应用开发人员创建嵌入式视觉或物联网边缘计算解决方案所需的所有构建模块,包括:

HDMI® 2.0 与 FPGA 夹层卡扩展

CoaXPress® 2.0

SDI(6 Gbps 和 12 Gbps)

具有自动协商功能的通用串行 10 GE 媒体独立接口 (USXGMII) MAC IP

USB 3.1 第 1 代和第 2 代协议支持

充分利用中档

应用应该决定技术,而不是相反,因此Microchip将继续通过MPFS025等器件发展其中端FPGA SoC产品组合。硅预计将于2022年第一季度上市。

对于那些刚接触RISC-V的人来说,最后一个重要的考虑因素是不断发展的生态系统,它可以帮助加速和保护你的工程投资。例如,Microchip的Mi-V RISC-V生态系统由AdaCore,Amazon FreeRTOS,DornerWorks,Green Hills Software,Hex Five,Siemens Embedded,Veridify Security和Wind River的免费和商业软件和工具提供支持,以使平台上构建的视觉系统为市场做好准备。

由于它是一个开放标准,为PolarFire器件开发的代码可以扩展和缩减Microchip FPGA SoC产品组合以及其他RISC-V RV64GC目标,而无需从头开始。

审核编辑:郭婷

-

FPGA

+关注

关注

1656文章

22304浏览量

630734 -

soc

+关注

关注

38文章

4520浏览量

227738

发布评论请先 登录

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新

RISC-V 工具链的版本更新、开发动态及生态建设愿景

沁恒微电子:从互连互通应用推动RISC-V落地发展

FPGA与RISC-V浅谈

芯来科技亮相RISC-V Day Tokyo 2025

西门子EDA邀您相约2025玄铁RISC-V生态大会

SOPHGO RISC-V SoC Linux Kernel 社区邮件列表建立,欢迎加入开源社区为RISC-V生态完善添砖加瓦

Microchip RISC-V FPGA SoC工具的应用

Microchip RISC-V FPGA SoC工具的应用

评论