NOR gate

OR操作,即是

C=A+B

NOR操作,即是

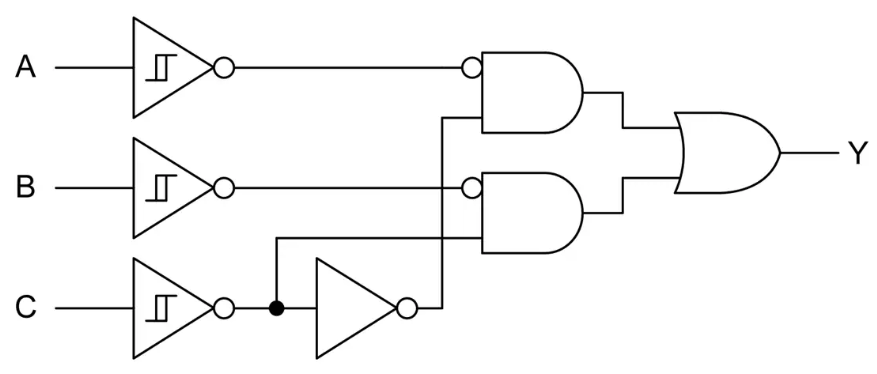

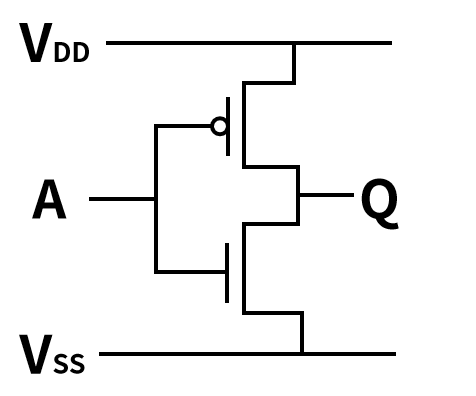

那怎么对CMOS反相器的结构,进行修改,使其变为NOR门呢?

首先,

需要两个NMOS器件或者PMOS器件,而且由两个输入控制

再者,

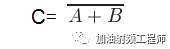

首先考虑NMOS部分,如果其中一个NMOS门是高电平,输出必须保持低电平。如下图所示。

其次,

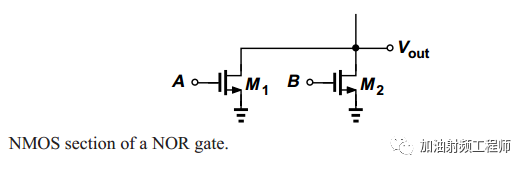

PMOS部分,如果A为高,B为高,或者A、B均为高时,PMOS部分必须处于关断的状态。而且,如果A和B均为低时,PMOS部分必须为ON的状态。

如下图所示,即满足以上的要求。

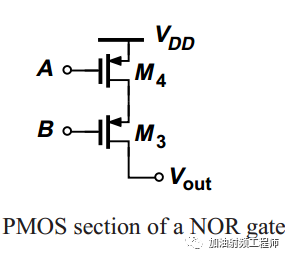

把PMOS部分和NMOS部分,结合起来,就成为一个完整的CMOS NOR gate.

从CMOS反相器来构建电路时,天生就带着反相属性,所以,当想要获得OR 门时,则是在NOR门的后面再加一个反相器。

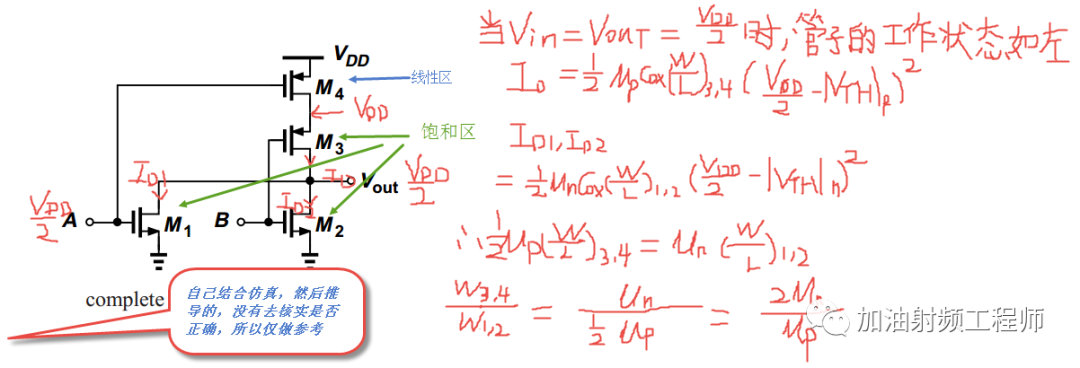

那M1,M2,M3,M4之间的宽度关系是怎么样的呢?

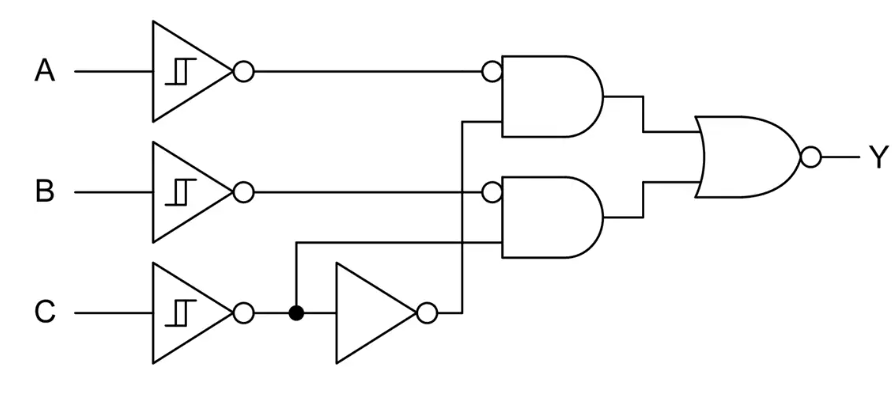

NAND Gate

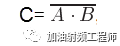

NAND操作即是,

只有输入A和B都为高的时候,C才是低。

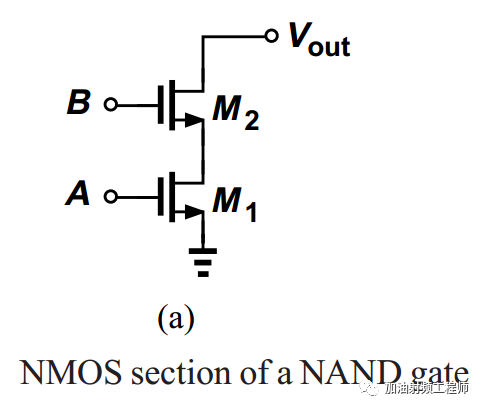

所以,在NMOS部分,应该是,只有A和B都为高的时候,才打通,使得Vout连接到地上。

如下图所示。

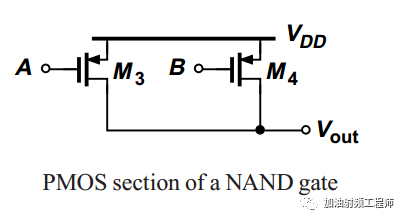

而PMOS部分,当A为低,B为低,或者A、B均为低时,PMOS能够将Vout与VDD连接。

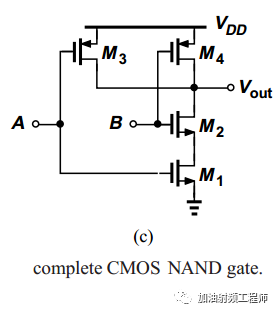

将NMOS和PMOS部分合并,即称为一个完整的CMOS NAND gate,如下图所示。

至于M3,M4,M1,M2之间的宽度关系,推导与NOR gate类似,这边应该都为W。

审核编辑 :李倩

-

CMOS

+关注

关注

58文章

6233浏览量

243394 -

NAND

+关注

关注

16文章

1766浏览量

141303 -

反相器

+关注

关注

6文章

332浏览量

45338

原文标题:CMOS的NOR门和NAND门

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NOR FLASH和NAND FLASH的对比

NOR Flash和NAND flash有什么区别

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异

SPI NOR Flash和SPI NAND Flash存储芯片的区别

探秘SN74AHC238:高速硅门CMOS解码器的设计与应用

SN74ACT238-Q1高速硅门CMOS解码器:设计与应用全解析

HT4125低压CMOS缓冲门器件详解

从NOR转向使用CS SD NAND:为什么必须加入缓存(Cache)机制?

从NOR Flash到NAND Flash和SD NAND,从底层结构到应用差异

霍尔元件在汽车电动尾门中的应用

SN74LV3T97-EP可配置多功能门技术解析

Texas Instruments SN74LV3T98-EP可配置多功能门技术解析

CMOS的逻辑门如何应用在电路中

CMOS的NOR门和NAND门

CMOS的NOR门和NAND门

评论