什么是RAM?

RAM(Random Access Memory)中文是随机存取存储器。为什么要强调随机存储呢?因为在此之前,一些的存储器都是顺序存储(Direct-Access),比较常见的如光碟,老式的磁带,磁鼓存储器等等。随机存取存储器的特点是其访问数据的时间与数据存放在存储器中的物理位置无关。

什么随机读写?

随机和顺序读写,是存储器的两种输入输出方式。存储的数据在磁盘中占据空间,对于一个新磁盘,操作系统会将数据文件依次写入磁盘,当有些数据被删除时,就会空出该数据原来占有的存储空间,时间长了,不断的写入、删除数据,就会产生很多零零散散的存储空间,就会造成一个较大的数据文件放在许多不连续的存贮空间上,读写些这部分数据时,就是随机读写,磁头要不断的调整磁道的位置,以在不同位置上的读写数据,相对于连续空间上的顺序读写,要耗时很多。在开机时、启动大型程序时,电脑要读取大量小文件,而这些文件也不是连续存放的,也属于随机读取的范围。

改善方法:做磁盘碎片整理,合并碎片文件,但随后还会再产生碎片造成磁盘读写性能下降,而且也解决不了小文件的随机存取的问题,这只是治标。更好的解决办法:更换电子硬盘(SSD),电子盘由于免除了机械硬盘的磁头运动,对于随机数据的读写极大地提高。

举个例子,SSD的随机读取延迟只有零点几毫秒,而7200RPM的随机读取延迟有7毫秒左右,5400RPM硬盘更是高达9毫秒之多,体现在性能上就是开关机速度。

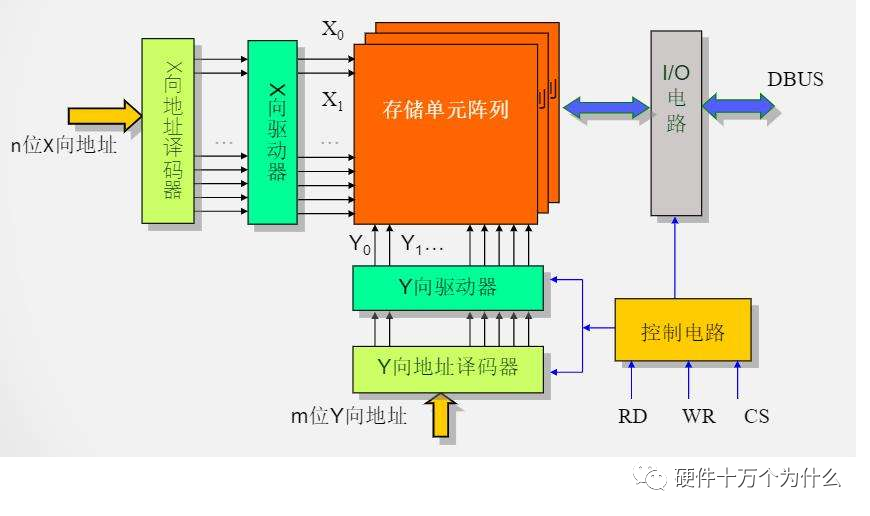

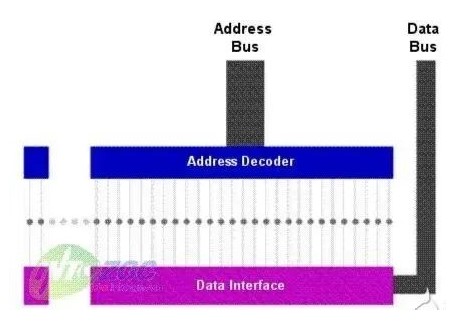

随机存取存储器(RAM)是存储器中最为人熟知的一种。之所以RAM被称为“随机存储”,是因为可以直接访问任一个存储单元,只要知道该单元所在记忆行X和记忆列Y的地址即可定位。

与RAM形成鲜明对比的是顺序存取存储器(SAM)。SAM中的数据存储单元按照线性顺序排列,因而只能依顺序访问(类似于盒式录音带)。如果当前位置不能找到所需数据,就必须依次查找下一个存储单元,直至找到所需数据为止。SAM非常适合作缓冲存储器之用,一般情况下,缓存中数据的存储顺序与调用顺序相同(显卡中的缓存就是个很好的例子)。而RAM则能以任意的顺序存取数据。

SRAM和DRAM的区别?

RAM的另一个特点是易失性(Volatile),虽然业界也有非易失(non-volatile)的RAM,例如,利用电池来维持RAM中的数据等方法。

RAM主要的两种类别是SRAM(Static RAM)和DRAM(Dynamic RAM)。

SRAM的S是Static的缩写,全称是静态随机存取存储器。而DRAM的D是Dynamic的缩写,全称是动态随机存取存储器。

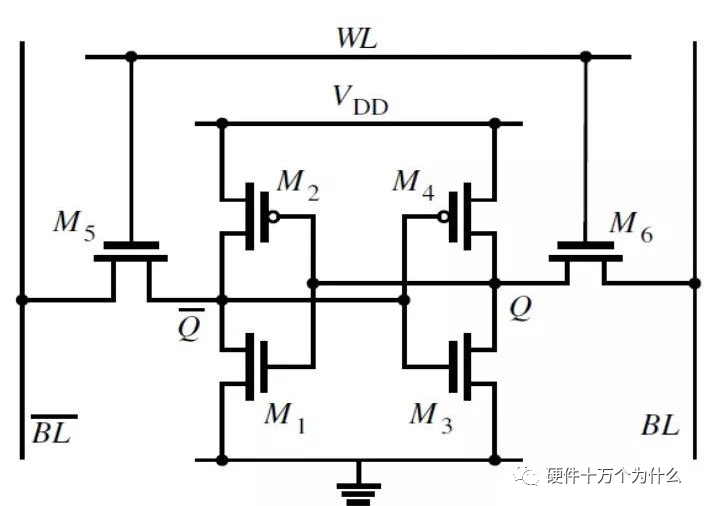

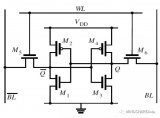

SRAM的结构,6场效应管组成一个存储bit单元的结构:

工作原理相对比较简单,我们先看写0和写1操作。 写0操作 写0的时候,首先将BL输入0电平,(~BL)输入1电平。 然后,相应的Word Line(WL)选通,则M5和M6将会被打开。 0电平输入到M1和M2的G极控制端 1电平输入到M3和M4的G极控制端 因为M2是P型管,高电平截止,低电平导通。而M1则相反,高电平导通,低电平截止。 所以在0电平的作用下,M1将截止,M2将打开。(~Q)点将会稳定在高电平。 同样,M3和M4的控制端将会输入高电平,因NP管不同,M3将会导通,而M4将会截止。Q点将会稳定在低电平0。 最后,关闭M5和M6,内部M1,M2,M3和M4处在稳定状态,一个bit为0的数据就被锁存住了。 此时,在外部VDD不断电的情况下,这个内容将会一直保持。

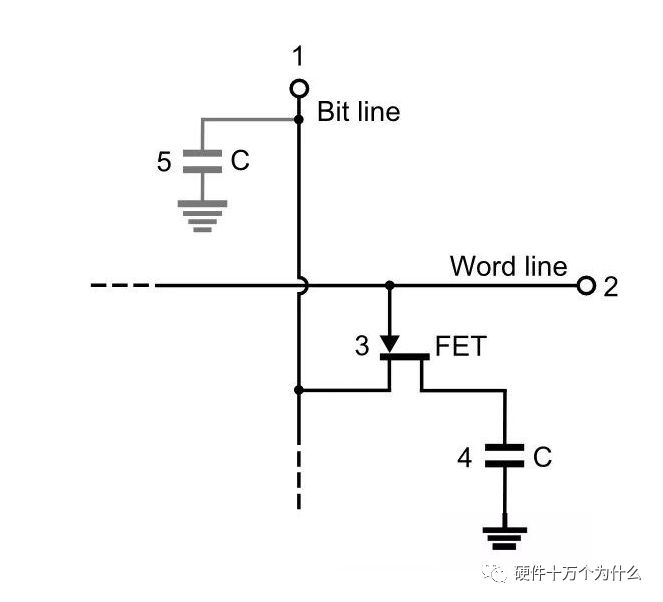

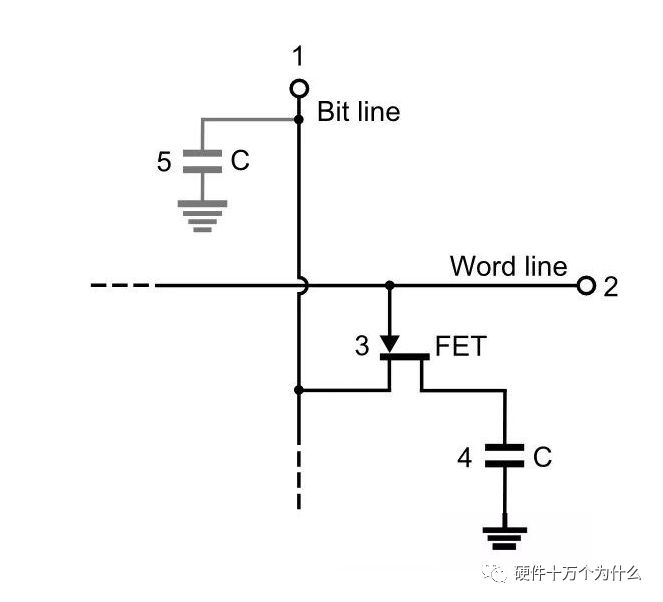

DRAM(Dynamic RAM)是指动态随机存取存储器。与SRAM最大的不同是,DRAM需要通过刷新操作来保持其存储的内容。让我们先来看看其一个bit存储单元(Cell)的结构:

其核心部件是4号位的电容C,这个电容大小在pF级别,用来存储0和1的内容。

由于电容会慢慢放电,其保存的电量将会随时间推移而慢慢漏电流漏掉。为了保证其内容的完整性,我们需要把里面的内容定期读出来再填写回去。这个操作称为刷新操作(Refresh)。

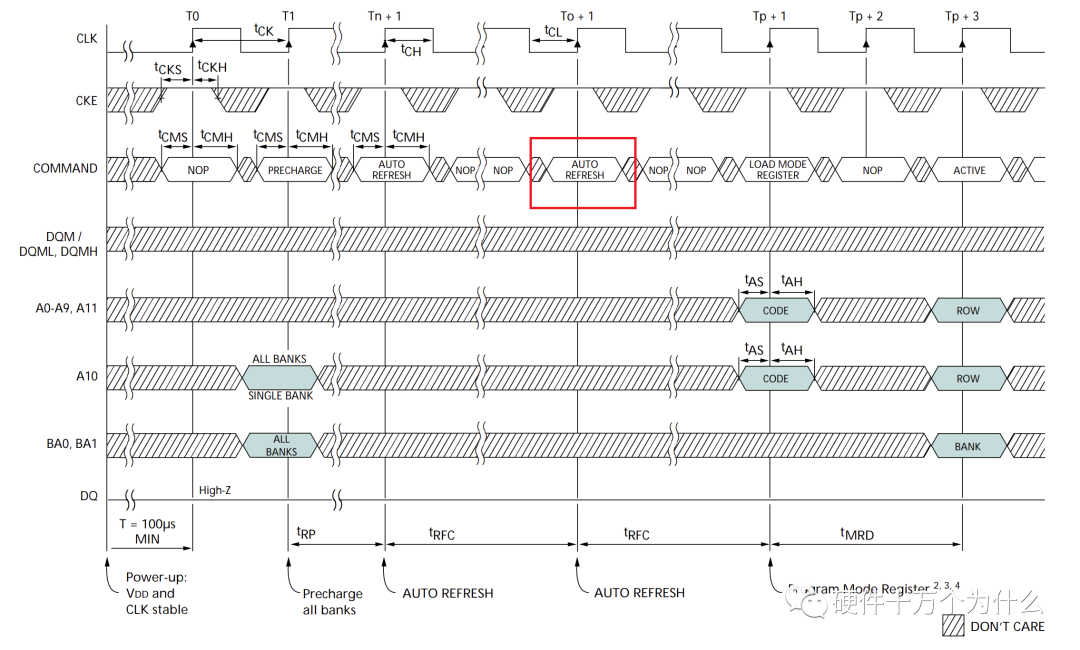

SDRAM 只有通过刷新命令(Refresh)操作才能保证数据的可靠性,SDRAM 的刷新操作是周期性的,在两次刷新的间隔可以进行数据的相关操作。我们在看SDRAM芯片参数时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表 这个芯片中每个Bank的行数。

刷新命令一次仅对一行有效,也就是说在64ms内这两种规格的 芯片分别需要完成4096次和8192次刷新操作。这4096操作可以平均15.625μs刷新一次,也可以一次全部刷新完,取决于你的数据读写时序。

当需要写1的时候,先将BL(Bit Line)输入高电平1,然后选中对应的Word Line(同一时间将只有一根WL被选中),打开相应的MOS管,如图中所示3号位。此时,外部驱动能力很强,通过一定的时间,4号位的电容将会被充满。此时,关闭3号位的MOS管。内容1将在一定时间内被保存在4号位的电容中。写0的操作与之相反,不同的是将4号位电容中的电荷通过Bit Line放光。然后关闭3号位的MOS管,锁存相应数据。

而读操作相对来说,较为复杂。4号位电容非常小,只有pF级别,而Bit Line往往都很长,上面挂了非常多个存储单元(cell),我们可以通过5号位的电容来表示。所以当我们直接把3号位的MOS管打开,Bit Line上将基本看不到什么变化。

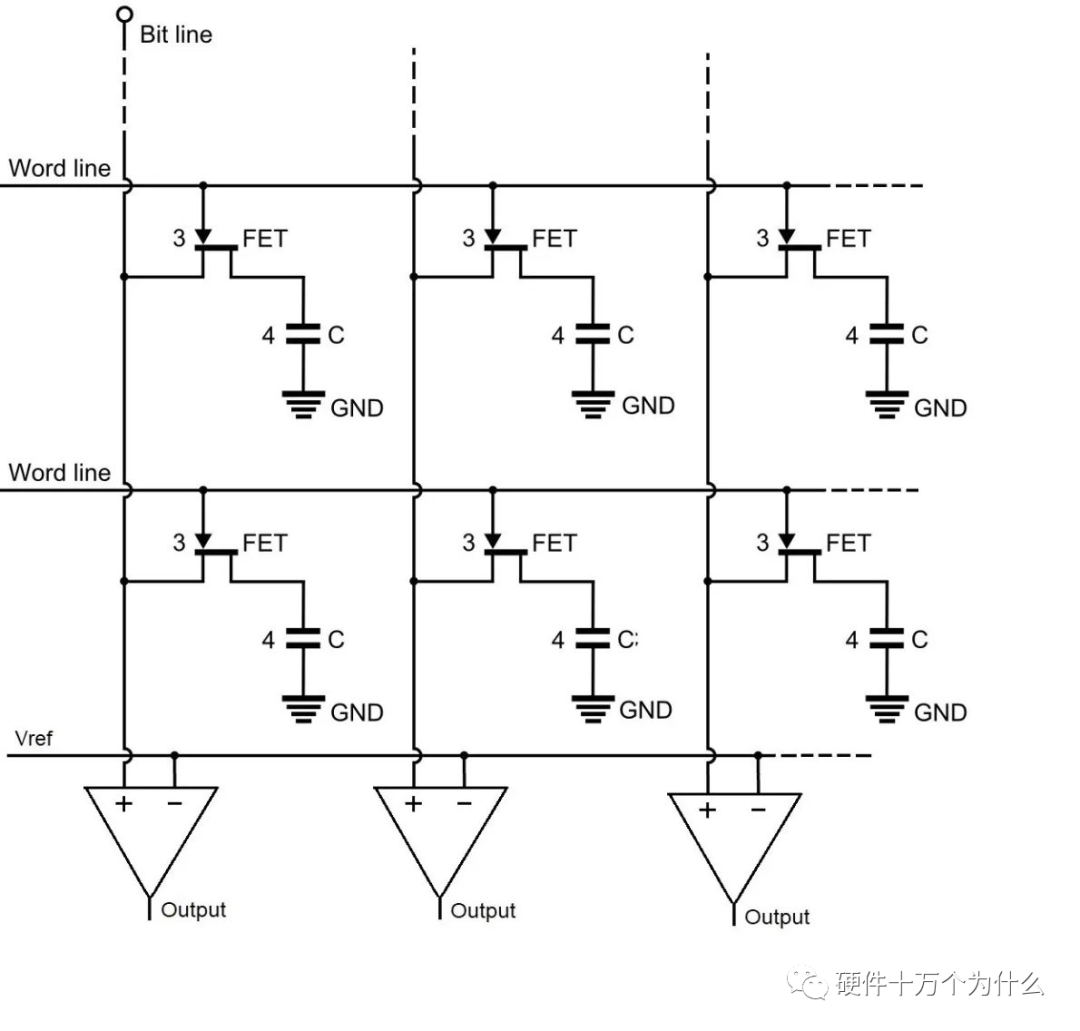

采用放大器来放大4号位电容的效果。结构图如下图所示:

我们可以定Vref为1/2的VDD电压,在读取电容里数据之前,我们先将所有Bit Line预充1/2 VDD的电压。然后,打开Word Line让选中的电容连接到Bit Line上面,如果原本的内容是1,则Bit line的总电压将会小幅攀升。否则,则会小幅下降。再通过差分放大器,将结果放大从而实现读操作。

这套方案是可以工作的,但Bit Line的数量不能太大。否则会导致距离Vref供电处较远的放大器Vref的值偏低,而导致差分放大器工作异常。同时,对于所谓的1/2 VDD预充,也存在不准的情况。

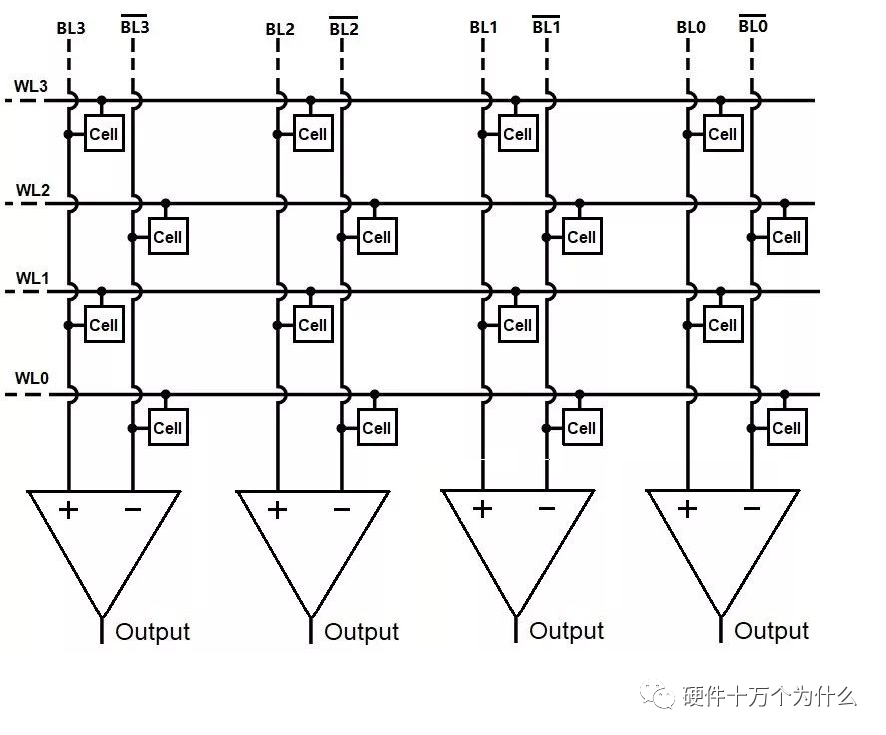

为了解决这个问题,有人提出,不如将原来的一根Bit Line设计成一对Bit Line,当其中一根Bit Line上的Cell被选中时,另一根Bit Line将不会有Cell被选中。从而没有Cell被选中的Bit Line可以充当放大器的Vref输入,其长度,负载以及寄生参数将会和另一根Bit Line十分一致,这样一来,放大器的工作就更加稳定了。结构图如下所示:

当读操作之前,我们先将1/2 VDD电压同时注入到BL和(~BL)上,这个动作被称为(pre-charge预充电)然后其中一根作为参考,来观察另一根Bit Line在某个Cell导通后的变化。

最后,我们总结一下区别:

成本对比:SRAM成本比较高(6个场效应管组成一个存储单元),DRAM成本较低(1个场效应管加一个电容)。另外随着DDR~DDR5的高速发展,SDRAM的发展更快,接口速率更高,生态更好,工艺更先进。所以SDRAM的成本原来越有优势。

存取速率:照道理来说,SRAM存取速度比较快,DRAM存取速度较慢(电容充放电时间)。

数据地址分开,SRAM不需要PreCharge,不需要Refresh。所以接口效率也越高。

但是随着DRAM发展更好,所以DRAM的接口速率发展越来越快。最终的综合表现还是DDR胜出。

-

DRAM

+关注

关注

41文章

2402浏览量

189553 -

存储器

+关注

关注

39文章

7755浏览量

172175 -

sram

+关注

关注

6文章

833浏览量

117716 -

磁盘

+关注

关注

1文章

401浏览量

26589

原文标题:SRAM与DRAM的区别

文章出处:【微信号:strongerHuang,微信公众号:strongerHuang】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DRAM,SRAM,SDRAM的关系与区别

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的区别.

SRAM和DRAM的区别

SRAM和DRAM的区别在哪

SRAM和DRAM的区别在哪

评论