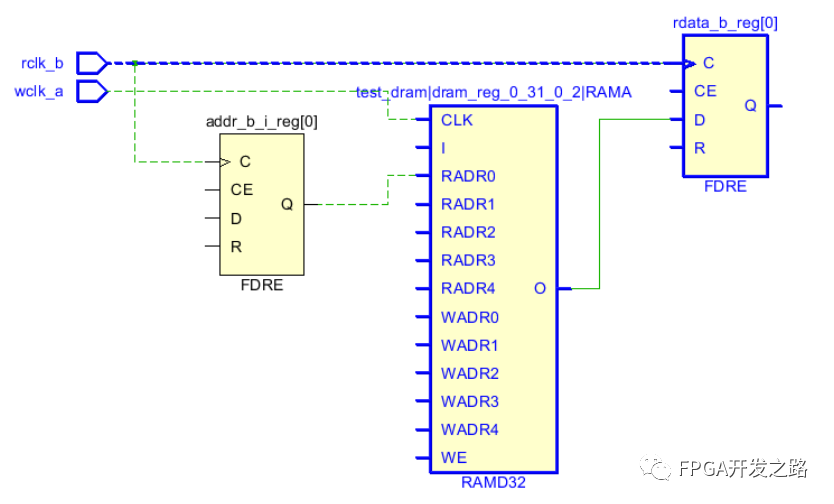

当 LUTRAM 读写使用不同的时钟,写时钟 wclk_a,读时钟 rclk_b。

总结

When the read and write addresses are different, there is no CDC path between the write and the read clocks.

However, when the write and read addresses are the same, then there is a CDC path between the write clock and the read clock.

原因

当读写地址不同时,读数据时数据不会发生写入,和写时钟无关,读出数据的delay是固定的,因此从 读地址寄存器到 输出寄存器 是一条同步路径。

当读写地址相同时,读数据时该地址同时正在被写入,读出数据的delay的是依赖于写时钟的,如果读写时钟靠的很近,输出寄存器就可能出现亚稳态。从 LUTRAM 到 输出寄存器 是一条异步路径。

Reference:

《Vivado Design Suite User Guide: Design Analysis and Closure Techniques》

-

寄存器

+关注

关注

31文章

5619浏览量

130410 -

数据

+关注

关注

8文章

7348浏览量

95017 -

时钟

+关注

关注

11文章

1999浏览量

135230

原文标题:LUTRAM 读写使用不同时钟的 CDC Path

文章出处:【微信号:FPGA开发之路,微信公众号:FPGA开发之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LUTRAM 读写使用不同时钟的CDC Path

LUTRAM 读写使用不同时钟的CDC Path

评论