“过去12年,中国集成电路建立了完整的芯片工业体系,并且保持了高速增长”,02专项技术总师、中国集成电路创新联盟副理事长兼秘书长叶甜春,在ICDIA 2022开幕式上,谈及中国集成电路的未来发展时,表示,“实行创新战略,路径创新、换道突围才是出路。其中,架构创新、电子设计工具(EDA)智能化、硬件开源化等技术创新将成为新焦点。”

近期,中国集成电路设计创新大会暨 IC 应用博览会(ICDIA 2022)在无锡太湖国际博览中心盛大举行。来自国内外近70家的集成电路企业在会上展示了各自最新的产品与技术。国家相关部委和地方领导、行业专家以及业界代表近1000人参加了会议。作为国内数字验证EDA领域头部企业,芯华章受邀参与IC设计创新论坛、人工智能与物联网创新论坛,围绕复杂芯片验证需求等话题,分享芯华章的创新思路。

方兴未艾 I AIoT带来验证挑战

在逐渐迈入智能社会的今天,AIoT技术逐渐深入落地到各种场景。AIoT技术带来的巨大市场价值也让人们有目共睹。艾瑞咨询数据预测, 2022年国内AIoT市场规模将超过7500亿元。

人工智能技术伴随着多场景应用,所需要的AI超大模型正快速演进,伴随而来的是对AI芯片需求的猛涨。AI芯片是AIoT产业中的核心一环,同时也是世界高科技产业竞争中绝对的焦点,而IC设计更是芯片产业链中举足轻重的存在。

“技术的发展与市场需求息息相关,人们对智能化的要求越高,就越是需要借助更高效的算力以获得更快的响应。值此背景下,比传统通用芯片在算力及功耗上更加具备优势的AIoT芯片就应运而生,也对数字验证提出了更高的要求。”芯华章科技产品与业务规划总监杨晔表示。

众所周知,AI类复杂SoC芯片处理流程有三个特点:数据复杂、计算复杂、模型复杂。这导致AI芯片的架构一般都特别复杂。多种通用和专用的计算单元、多种存储单元、硬件和软件都需要紧密交互,才能高效完成AI处理流程。这样的AI芯片架构,在实现AISoC原型验证时会有很多困难:设计复杂,多片分割困难;大容量SRAM在FPGA芯片上实现资源不够;软硬件集成验证要求更高;产品迭代周期短,要求设计验证周期缩短;多样化的传感器数据硬件接口需要在FPGA原型上物理验证等。

“基于FPGA硬件和拥有自主知识产权的全流程软件,芯华章自主研发的高性能FPGA原型验证系统桦捷(HuaPro-P1),可以有效解决以上痛点,帮助SoC/ASIC芯片客户实现设计原型的自动综合、分割、优化、布线和调试,从而有效减少用户人工投入,提升系统验证与软件开发效率,缩短芯片设计周期,给AI SoC芯片的验证带来完整、高效的解决方案。”杨晔表示。

返本还源 I 系统引领芯片创新

当从微观的技术应用回到更宏观的行业视角,我们会发现复杂SoC芯片面临的考验,远不止AI带来的算力与架构难关。一方面,长期作为半导体发展“金科玉律”的摩尔定律,正在受到物理极限与经济性的双重挑战,芯片创新向多维度发展;另一方面,新兴应用领域飞速发展,带来需求急剧分化的同时,创新周期却不断缩短,占据芯片设计过半时间的验证环节压力巨大。

“未来,系统应用将是芯片设计的核心驱动力。验证技术要面向电子系统,打造融合统一的底层基座,提供智能化融合解决方案,赋能芯片到系统的完整创新周期。”芯华章科技资深产品市场经理郭正给出了芯华章的解决方案。

秉承“高起点、厚积累、求创新”的发展战略,芯华章从终局思维出发,基于全新统一的底层框架,应用新的验证方法学,已发布五款自研数字验证EDA产品,基本建立完整的数字验证全流程,在多个领域实现技术创新。

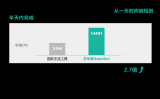

比如,传统的仿真器只能在Intel的X86服务器上运行,但芯华章的仿真器就能无缝移植到不同的处理器上;芯华章发布的数字调试产品昭晓Fusion Debug,采用完全自研的高性能数字波形格式,与主流商业波形格式相比,读写速度快至3倍。

加特兰微电子汽车产品总监刘洪泉曾表示,“经过测试,通过HuaPro-P1自动化工具的辅助,在P1上实现系统原型与传统产品相比节约了三倍以上的时间,并保持了良好性能与稳定的运行,帮助我们加快整体的芯片设计周期。”

目前,芯华章产品及服务已得到中科院半导体所、燧原科技、芯来、鲲云等数十家业内知名企业实际项目采用,为我国产业数字化升级带来了突破性的价值。

未来,芯华章将继续秉承产业发展需求,以需求带动技术创新,并以技术创新反哺产业发展,助力复杂SoC芯片验证效率提升,赋能数字化时代系统应用,打造自主可信赖的电子系统创新基石。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22502浏览量

639081 -

集成电路

+关注

关注

5464文章

12681浏览量

375672 -

soc

+关注

关注

40文章

4622浏览量

230156 -

芯华章

+关注

关注

0文章

195浏览量

12013

原文标题:创新引领 芯华章助力复杂SoC芯片验证破局

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

基于FPGA的DAQ系统|实现高性能数据采集的挑战

芯华章荣膺2026 IC风云榜年度AI优秀创新奖

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

芯华章GalaxEC HEC工具破解RISC-V验证难题

【喜报】芯神瞳原型验证解决方案荣膺工博会“集成电路创新成果奖”

芯华章与守正通信达成战略合作

芯华章RISC-V敏捷验证方案再升级

芯华章携手EDA国创中心推出数字芯片验证大模型ChatDV

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

芯华章高性能FPGA原型验证系统引领芯片创新

芯华章高性能FPGA原型验证系统引领芯片创新

评论