在流片前验证中如何测量功耗?

一般来说,功耗测量是在门级进行,通过由回归向量组成的验证平台执行 DUT,然后跟踪 DUT 的开关活动来完成。该方法有两个问题。

首先,测试发生在设计周期的晚期。虽然与实际芯片的差异在 5% 以内,但没有足够的灵活性来纠正设计中的问题。更好的折中方法是在 RTL 评估动态功耗,这会导致与芯片的偏差较大(在15% 范围内),但能提供更大的灵活性来支持设计修改。

其次,验证平台向量不能很好地代表设计将来的使用方式。为了实现准确的功耗估算,必须在运行实际工作负载和性能/功率基准测试的目标系统上尽可能准确地捕获开关活动。

执行功耗分析的步骤是什么?如何完成?

显然,RTL 仿真再也无法胜任这一要求苛刻的任务。需要一种层次化方法,从高级别的设计抽象开始,直到RTL 和门级。再也没有任何单一工具能够完成全部任务。相反,让各种特性实现最佳平衡的多种工具可以加速功耗估算和优化(表 1)。

第一步,整个 DUT 用 C/C++ 做高级抽象,根据硬件/软件规格进行快速验证,并非常粗略地估算功耗。

接下来,在一个混合设置中验证功耗,该混合设置包含高级别抽象描述的设计部分(通常包括处理内核和存储器,例如 Arm 快速模型))和 RTL 的其他设计部分。高级别抽象部分在主机服务器上运行,RTL 在硬件加速器上执行,二者通过基于事务的接口连接。

表 1. 需要采用一种层次化方法来加速功耗估算和分析过程。(信息来源:Lauro Rizzatti)

虽然硬件加速器以几 MHz 的速度运行,但混合配置可以实现 50 MHz 左右的速度,足以快速启动 Android、Linux 和其下的所有内核,以及执行基准测试和实际应用。

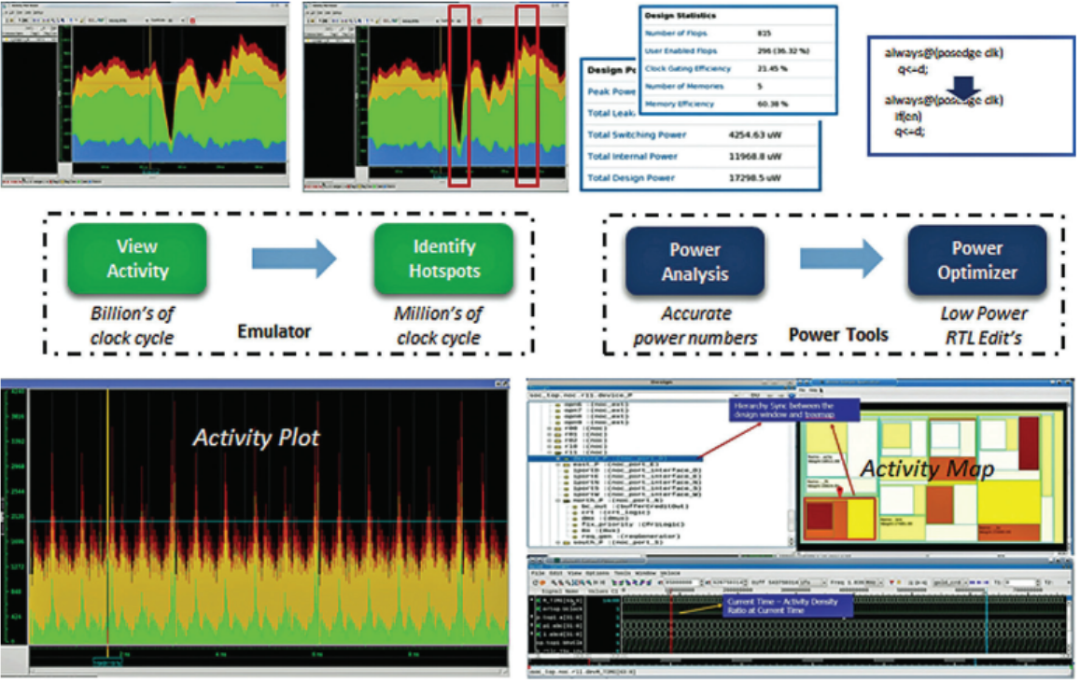

该设置提供了一个很好的基础,支持在相对较短的时间内对整个设计的功耗进行分析。通过在数十亿个时钟周期的长期运行中绘制开关活动,设计团队可以识别几百万时钟周期范围内的高功耗和低功耗热点。同样,通过在活动分布图中拼贴功耗区域,团队便可直观地识别高低功耗的设计部分。

一旦确定热点和关键区块,团队就可以切换到全 RTL,获得对各设计网络的准确详细可见性。通过将活动绘图与嵌入式软件代码相关联,并将活动分布图与RTL 代码相关联,团队可以迅速聚焦于有潜在功耗问题的区域。

捕获整个工作负载处理的完整设计活动,是非常重要的(图 2),避免仅仅是采样(通常利用 FPGA 平台完成,缺乏完全的内部可见性)。

图 2. 功耗工具可以利用活动分布图和活动绘图来跟踪功耗趋势分析。(信息来源:西门子 EDA)

审核编辑:汤梓红

-

西门子

+关注

关注

98文章

3372浏览量

120695 -

功耗

+关注

关注

1文章

844浏览量

33339 -

RTL

+关注

关注

1文章

395浏览量

62875 -

DUT

+关注

关注

0文章

194浏览量

13491

原文标题:白皮书下载 | 片上系统设计中利用硬件加速器进行功耗分析

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AD7785:高精度测量的低功耗利器

如何使用 R&S®ZNL 矢量网络分析仪设置并执行频谱分析测量

在流片前验证中如何测量功耗 执行功耗分析的步骤是什么

在流片前验证中如何测量功耗 执行功耗分析的步骤是什么

评论