电子发烧友网报道(文/周凯扬)对于近几年推出的HPC系统来说,高能效已经成了大家无法规避的话题,就连TOP500上的超算,比如排名第一的超级计算机,美国能源部下属国家实验室的Frontier系统,也凭借单机柜原型机在GREEN500能效榜上拿下第一,整个系统拿下了第二的成绩。与十多年前的那些HPC系统相比,现在的设计不仅是在性能上不可同日而语,连能效比也提升了百倍以上。

能做到如此高的能效,除了CPU、GPU本身的设计外,也要归功于先进的冷却系统和电源管理。对于已经走向多核异构时代的HPC系统而言,系统级别的电源与热管理尤为重要,而且还得做到精心调校、针对负载进行智能调整的动态电源管理。

已有的电源控制器方案

针对不同的CPU系统,市面上已经有了不少商用电源控制器,比如英特尔的CPU有用于C-States管理的电源控制单元(PCU),ARM有帮助应用处理器卸载电源与系统管理任务的系统控制处理器(SCP)和可管理控制处理器(MCP),AMD有采集传感数据进行快速调整的系统管理单元(SMU),IBM的Power处理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于单核心的MCU打造的,在面对单片核心数越来越多以及逐渐普及的Chiplet设计时,这些方案就因为缺乏扩展性而显得力不从心了。除此之外,主办的尺寸、布局和成本的因素,进一步限制了HPC处理器本身的片上电源管理。正因如此,在拥有庞大核心数量的HPC系统上,我们需要一个可扩展的控制器方案。

在这些要求下,瑞士苏黎世联邦理工学院(ETH)的集成系统实验室就基于开源的RISC-V架构,打造了这样一个拥有并行控制规则计算加速的电源控制器IP——ControlPULP。

可扩展的电源控制器

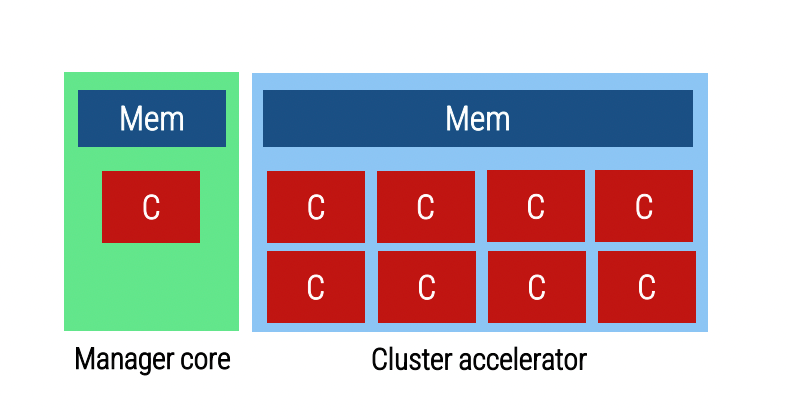

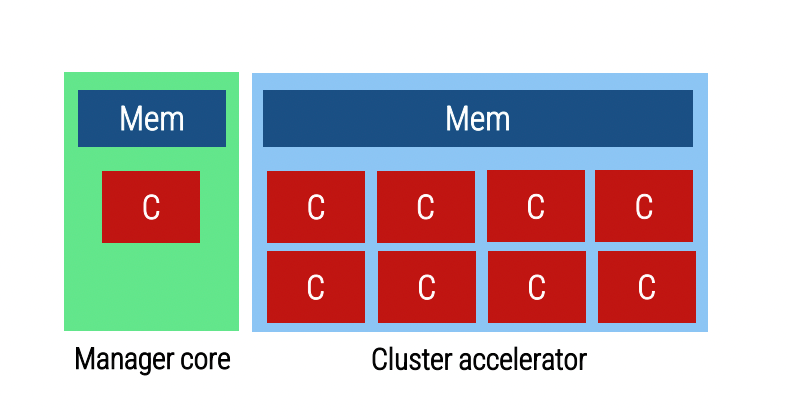

ControlPULP采用了九核的设计,一个单核管理器核心,和8核的加速器簇来加速电源控制固件的工作负载,而这九个核心全部基于CV32E40P,这是一个32位4级流水线的RISC-V开源核心,由瑞士苏黎世联邦理工学院和意大利博罗尼亚大学合作的PULP平台维护,他们也将CV32E40P捐献给了开放硬件联盟OpenHW。

ControlPULP架构 / 瑞士苏黎世联邦理工学院

此外,ControlPULP集成了一个直接内存访问引擎,用于获取片上传感器的数据,还有一个uDMA引擎,用于支持基于标准电源管理接口(比如电压调节总线AVSBUS/PMBUS)的片外外围设备以及通过I2C或MTCP协议的BMC通信。至于底层控制策略的调度,则靠PULP平台自己开发的开源FreeRTOS来实现。

在其电源控制策略中,ControlPULP主要负责两大主要控制任务,一个是定期控制任务,一个是电源控制任务。定期控制任务结合温度传感器、功耗传感器内的数据,以及目标频率、预期负载和总功耗预算等数据,来进行电源调度和热管理。电源控制任务则是通过PMBUS/AVSBUS获得的电压轨功耗和BMC通信来完成快速电源控制。

根据他们测试的结果,这种多核加速器簇的结构相较过去的单核方案来说,在控制策略的执行速度上快了5倍,而且集成在HPC处理器中并不会占用多大的面积。他们在格芯的GF22FDX工艺下得到的综合结果中,ControlPULP所占处理器面积甚至不到百分之一。

开源电源控制器的未来

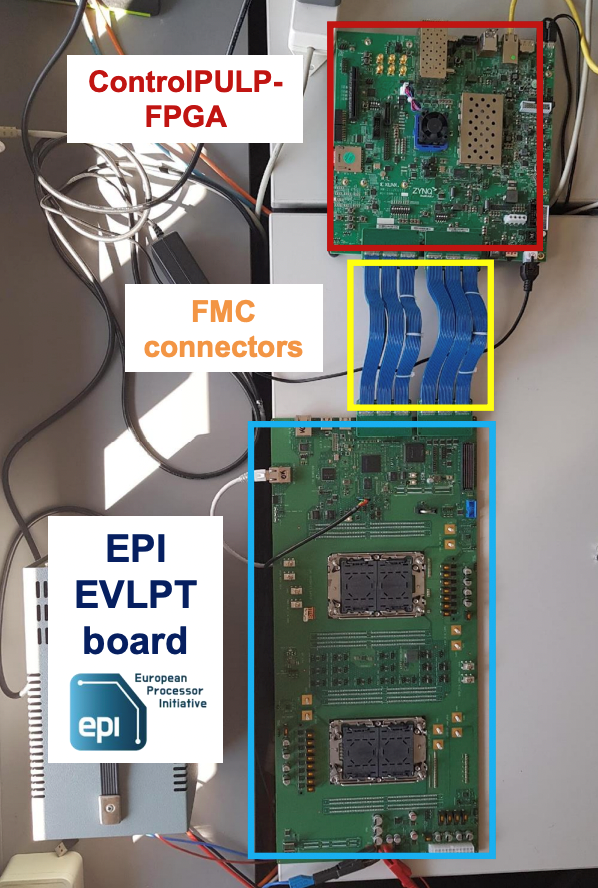

ControlPULP作为一个软硬件完全开源的集成IP方案,不少人担心是否真的会有人将其投入商用,事实上,这样的案例已经快要面世了。根据ETH透露,欧洲处理器计划(EPI)的先行者,法国企业SiPearl的E级HPC芯片,72核的Rhea处理器就将集成ControlPULP。

不过,这还只是ControlPULP迈出的第一步,未来PULP团队还计算完成65nm的流片来进一步开展硬件验证,并探索更先进的预测性电源控制策略。但不管怎么说,这都是首个RISC-V的HPC电源控制器方案,RISC-V在HPC市场也需要更多的亮相,而不仅仅只是作为加速器。

能做到如此高的能效,除了CPU、GPU本身的设计外,也要归功于先进的冷却系统和电源管理。对于已经走向多核异构时代的HPC系统而言,系统级别的电源与热管理尤为重要,而且还得做到精心调校、针对负载进行智能调整的动态电源管理。

已有的电源控制器方案

针对不同的CPU系统,市面上已经有了不少商用电源控制器,比如英特尔的CPU有用于C-States管理的电源控制单元(PCU),ARM有帮助应用处理器卸载电源与系统管理任务的系统控制处理器(SCP)和可管理控制处理器(MCP),AMD有采集传感数据进行快速调整的系统管理单元(SMU),IBM的Power处理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于单核心的MCU打造的,在面对单片核心数越来越多以及逐渐普及的Chiplet设计时,这些方案就因为缺乏扩展性而显得力不从心了。除此之外,主办的尺寸、布局和成本的因素,进一步限制了HPC处理器本身的片上电源管理。正因如此,在拥有庞大核心数量的HPC系统上,我们需要一个可扩展的控制器方案。

在这些要求下,瑞士苏黎世联邦理工学院(ETH)的集成系统实验室就基于开源的RISC-V架构,打造了这样一个拥有并行控制规则计算加速的电源控制器IP——ControlPULP。

可扩展的电源控制器

ControlPULP采用了九核的设计,一个单核管理器核心,和8核的加速器簇来加速电源控制固件的工作负载,而这九个核心全部基于CV32E40P,这是一个32位4级流水线的RISC-V开源核心,由瑞士苏黎世联邦理工学院和意大利博罗尼亚大学合作的PULP平台维护,他们也将CV32E40P捐献给了开放硬件联盟OpenHW。

ControlPULP架构 / 瑞士苏黎世联邦理工学院

此外,ControlPULP集成了一个直接内存访问引擎,用于获取片上传感器的数据,还有一个uDMA引擎,用于支持基于标准电源管理接口(比如电压调节总线AVSBUS/PMBUS)的片外外围设备以及通过I2C或MTCP协议的BMC通信。至于底层控制策略的调度,则靠PULP平台自己开发的开源FreeRTOS来实现。

在其电源控制策略中,ControlPULP主要负责两大主要控制任务,一个是定期控制任务,一个是电源控制任务。定期控制任务结合温度传感器、功耗传感器内的数据,以及目标频率、预期负载和总功耗预算等数据,来进行电源调度和热管理。电源控制任务则是通过PMBUS/AVSBUS获得的电压轨功耗和BMC通信来完成快速电源控制。

根据他们测试的结果,这种多核加速器簇的结构相较过去的单核方案来说,在控制策略的执行速度上快了5倍,而且集成在HPC处理器中并不会占用多大的面积。他们在格芯的GF22FDX工艺下得到的综合结果中,ControlPULP所占处理器面积甚至不到百分之一。

开源电源控制器的未来

ControlPULP作为一个软硬件完全开源的集成IP方案,不少人担心是否真的会有人将其投入商用,事实上,这样的案例已经快要面世了。根据ETH透露,欧洲处理器计划(EPI)的先行者,法国企业SiPearl的E级HPC芯片,72核的Rhea处理器就将集成ControlPULP。

不过,这还只是ControlPULP迈出的第一步,未来PULP团队还计算完成65nm的流片来进一步开展硬件验证,并探索更先进的预测性电源控制策略。但不管怎么说,这都是首个RISC-V的HPC电源控制器方案,RISC-V在HPC市场也需要更多的亮相,而不仅仅只是作为加速器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源控制器

+关注

关注

0文章

165浏览量

33830 -

HPC

+关注

关注

0文章

342浏览量

24829 -

RISC-V

+关注

关注

48文章

2802浏览量

51934

发布评论请先 登录

相关推荐

热点推荐

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

随着 RISC -V处理器在 FPGA 领域的广泛应用,易灵思 FPGA 的 Sapphire RISC-V 内核凭借软硬核的灵活支持,为开发者提供多样选择。本文深入探讨 Sapph

为什么RISC-V是嵌入式应用的最佳选择

最近RISC-V基金会在社交媒体上发文,文章说物联网和嵌入式系统正在迅速发展,需要更高的计算性能、更低的功耗和人工智能。RISC-V是为未来而建的,包括超高效的MCU到高性能应用处理器

提高RISC-V在Drystone测试中得分的方法

性能:内存的读写速度、延迟和带宽等都会影响到 Drystone 的性能。

指令集优化:对RISC-V指令集的优化也会影响性能。例如,对于特定的应用或计算任务,可以通过定制指令集来提高性能。

编译

发表于 10-21 13:58

RISC-V 发展态势与红帽系统适配进展

,硬件情况有了改善,红帽也成为最早支持 RISC-V 系统的企业之一,当时已能搭建支持桌面的系统,这在当时是很大的突

发表于 07-18 10:55

•3876次阅读

RISC-V International CEO:RISC-V 应用全面开花,2031 年渗透率将达 25.7%

and RISC-V Adoption in 2025》。 当前,RISC-V 的成功已从嵌入式计算领域加速向存储技术与高性能计算(HPC)领域渗透,展现出跨行业的颠覆性潜力。Andrea Gallo 分享了 The SH

发表于 07-17 10:28

•3566次阅读

【好书推荐】RT-Thread第18本相关书籍!RISC-V嵌入式系统设计 | 技术集结

内容简介《RISC-V嵌入式系统设计》是一本专为嵌入式系统初学者编写的实用入门教材,围绕当前热门的国产RISC-V微

FPGA与RISC-V浅谈

RISC-V处理器的SoC数量在2024年约为20亿颗,到2031年有望突破200亿颗。 RISC-V的概念与优势 RISC-V是一种全新的

发表于 04-11 13:53

•549次阅读

芯来科技携手芯芒科技发布RISC-V CPU系统仿真平台

专业RISC-V处理器IP及解决方案公司芯来科技与杭州芯芒科技深入合作,共同研发推出芯来全系列RISC-V CPU

芯来科技亮相RISC-V Day Tokyo 2025

RISC-V Day Tokyo 2025春季会议于日前在东京大学ITO国际研究中心顺利举行。The RISC-V Day Tokyo作为日本最大的RISC-V活动,汇集了众多优秀的RISC-

Arm与RISC-V架构的优劣势比较

和合作伙伴。

RISC-V

基于这类开放标准,企业能够设计和使用定制处理器,而无需支付高额的授权费用,也不会受到地域管辖的限制。除此之外,企业针对特定应用场景,还能修改指令集架构的扩展,以此获得更大

发表于 02-01 22:30

关于RISC-V芯片的应用学习总结

和模块化设计成为其显著优势。物联网设备通常需要长时间运行,且对体积和功耗有严格要求。RISC-V芯片通过精简指令集和优化设计,实现了低功耗的同时保持了高性能,非常适合用于传感器节点、智能家居控制器

发表于 01-29 08:38

RISC-V基础指令详解

也被称作U J型指令

另外RISC-V中预设的寄存器数量是32个,设计采用的通用原则:数量适量,少而快。寄存器编号从0到31,记为X0-X31,其中X0寄存

发表于 12-29 18:47

risc-v芯片在电机领域的应用展望

,电机控制系统的需求将不断增长。RISC-V芯片凭借其灵活性和可扩展性,将能够很好地适应这些领域的变化,为电机控制提供更高效、更可靠的解决方案。

同时,RISC-V芯片在电机

发表于 12-28 17:20

RISC-V架构及MRS开发环境回顾

的指令集使用模块化的方式进行组织,每一个模块使用一个英文字母来表示。RISC-V最基本也是唯一强 制要求实现的指令集部分是由I字母表示的基本

发表于 12-16 23:08

HPC系统的电源控制器,RISC-V也来插一脚?

HPC系统的电源控制器,RISC-V也来插一脚?

评论