外设IP核(Peripheral IP Core)统指系统芯片里面的除嵌入式CPU以外的外围专用功能IP核的总称,包括串行总线接口,存储器控制器等。外设一般通过总线核处理器连接,通常是总线的从设备。外设接收处理器的指令后,完成特定的功能。作为系统芯片的重要组成部分,外设协助处理器完成控制,计算等任务,提高了处理器的工作效率。

外设通常在处理器的控制下工作,处理器通过读/写外设的寄存器管理外设。外设寄存器一般包含两类:第一类是控制寄存器,处理器对这类寄存器写入配置实现对外设的控制;第二类寄存器是状态寄存器,处理器通过读取这类寄存器了解外设当前的工作状态。

按照功能分类,常见的外设有4类:1通用数据传输协议接口外设,如I2C,SPI,UART,MAC,USB等,这些外设按照数据传输协议进行数据的收/发;2通用控制外设,如通用I/O接口(GPIO),脉宽调制接口(PWM)等,这些外设可对引脚进行特殊化的操控;3加速器型外设,类似于协处理器,加速特定类型的运算,如图像编解码,高速加解密核卷积运算等;4系统功能外设,帮助处理器完成系统芯片的系统运行功能,确保应用正确执行,如定时器和中断控制器等。

按照速度分类,常见的外设分为高速外设和低速外设两类:高速外设的工作频率高,执行复杂的任务或者计算,如图像处理加速器,高速加解密引擎和高速通信接口等;低速外设的工作频率低,主要负责SoC与外界的低速通信,维护SoC系统功能,如I2C,INTC等。

随着外设种类的增加和性能的提高,为使外设与处理器之间的速度,时序和格式等匹配,外设逐渐发展为拥有独立的控制单元与接口电路。随着外设功能越来越多样化,性能要求越来越苛刻,如何设计出可靠性高,控制简单,智能化且易于扩展的外设称为未来的发展趋势。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

20333浏览量

255044 -

寄存器

+关注

关注

31文章

5620浏览量

130423 -

系统芯片

+关注

关注

0文章

39浏览量

18587

原文标题:系统芯片—外设IP核

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

海外静态IP和海外动态IP有哪些区别?怎么选择?

使用AXI4接口IP核进行DDR读写测试

Perforce IPLM产品简介:IP生命周期管理与协作,加速芯片设计

VDMA IP核简介

蜂鸟E203移植到FPGA开发板前的IP核例化工作

Vivado浮点数IP核的握手信号

Vivado浮点数IP核的一些设置注意点

ram ip核的使用

VIVADO自带Turbo译码器IP核怎么用?

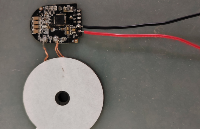

ip6826芯片参数:无线充电领域的高效兼容解决方案

系统芯片—外设IP核(Peripheral IP Core)

系统芯片—外设IP核(Peripheral IP Core)

评论