2019 年是极紫外 (EUV) 光刻技术的重要里程碑。当年,EUV图案化技术首次用于7nm技术一代逻辑芯片的量产。插入以图案化芯片后端 (BEOL) 的最关键层,它可以打印间距为 36-40nm 的金属线。

凭借 13.5nm 的极短波长,EUV 光刻已被引入以取代 193nm(浸入式)光刻——这是由瑞利方程决定的分辨率转换。根据这个方程式,可以通过在晶圆曝光期间使用波长较小的光来提高光刻工具的分辨率,从而提高其打印具有特定半间距或临界尺寸 (CD) 的特征的能力。此外,193nm 复杂且昂贵的多重图案化要求——包括将芯片图案分割成两个或更多更简单的掩模——可以再次移回单一图案化 EUV。

在开发方面,研究人员一直在不断尝试进一步推动当今最先进的 EUV 全场扫描仪,即 ASML NXE:3400B 的单次打印能力。例如,今年早些时候,imec 和 ASML 能够展示 28nm 间距的单次曝光图案化线/空间准备就绪,对应于 5nm 逻辑技术节点的关键 BEOL 金属层。这使当前的扫描仪接近其大批量制造的分辨率极限,约为 13 纳米(26 纳米间距)。随着逻辑的发展,存储器制造商越来越多地考虑使用 EUV 光刻技术来满足未来存储器的高密度要求——例如用于关键 DRAM 结构的图案化。

与此同时,正在探索多重图案 EUV 光刻选项,以将 EUV 推进到下一个节点。虽然这些“技巧”提供了更轻松的间距,但它们也有一个缺点:处理步骤数量增加,增加了图案化步骤的成本、复杂性和处理时间。

2023 年将标志着 EUV 光刻技术发展的新里程碑。届时,预计第一代新一代 EUV 光刻工具将进入现场:高 NA EUV 光刻扫描仪——预计以更少的图案化步骤打印 2nm(及以上)逻辑芯片的最关键特征。瑞利方程再次证明了向高 NA 光刻的过渡,它为提高分辨率提供了第二个旋钮:增加投影镜头的数值孔径 (NA)。NA 控制用于形成图像的光量(更准确地说是衍射级数),从而控制图像的质量。

之前已经应用过向更高 NA 成像设备的过渡,请记住从 193nm 干法到 193nm 浸没式光刻的转变。当时,用水代替透镜和晶圆之间的空气的光学技巧使 NA 增加了 45%。在 EUV 的情况下,ASML 将通过重新设计光刻系统中的光学器件,从当前的 0.33 NA 变为 0.55NA(即 NA 增加 67%)。0.55NA EUV 光刻有望最终实现 8nm 分辨率,对应于一次曝光中 16nm 间距的印刷线/间距。

雄心勃勃的时间表……

0.55NA EUV 光刻技术将把图案化推向比当前 0.33NA EUV 光刻系统更小的特征。但前进的道路是雄心勃勃的。EUV 光刻系统的开发可以追溯到 2000 年代,从安装第一台预生产的 EUV 扫描仪到最近在大批量制造中引入 EUV 光刻,有十年的时间跨度。对于高 NA,目标是将时间框架压缩到仅 3 年,预计 2023 年将推出第一个原型(EXE:5000)。

图 1:ASML 的 EXE:5000 高 NA EUV 光刻扫描仪渲染图(由 ASML 提供)

在第一个高数值孔径工具问世之前,专用实验室设备和当前一代的极紫外光刻工具和材料正被推向极限,以尽可能地准备和降低新的高数值孔径 EUV 光刻技术的风险。

同时,imec 正在与 ASML 合作开设一个联合高 NA 实验室,将在其中建造高 NA 系统,连接到涂层和开发轨道,并配备计量设备。他们将共同为行业创建生态系统以满足工艺要求,并建立与高NA工具开发相伴的基础设施——包括变形成像、新掩模技术、计量、抗蚀剂筛选和薄膜图案化材料开发等. 这些发展将在下面更详细地讨论。此外,客户将可以使用高 NA 实验室来开发他们的私有高 NA 用例。

解决过程和计量需求:共同努力

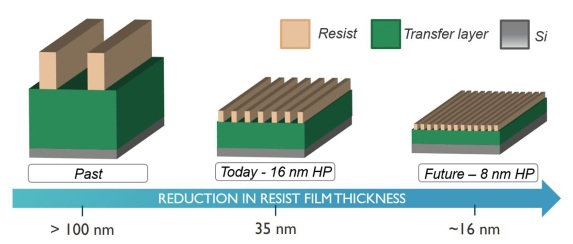

随着高 NA EUV 光刻技术的出现,抗蚀剂更薄的趋势将继续存在,其最终目标是印刷 16nm 间距的线/间距,对应于宽度小至 8nm 的印刷线。这需要厚度小于 20nm 的抗蚀剂薄膜以保持 2:1 的理想纵横比(定义为线的高度和宽度之间的比率)。使用较厚的抗蚀剂,纵横比会增加,随之而来的是线条崩塌的风险。高数值孔径 EUV 光刻技术带来了使用更薄抗蚀剂薄膜的第二个原因。根据第二个瑞利方程,焦深(DOF)——即(航空)图像焦点所在的抗蚀剂高度——按数值孔径的平方减小。模拟预测,相对于当前的 0.33NA 光刻,DOF 会有效降低 2-3 倍。

降低的抗蚀剂厚度要求为高 NA EUV 工艺带来了新的需求,包括图案转移。筛选(新)抗蚀剂、优化硬掩模和蚀刻工艺的选择性,以及评估超薄抗蚀剂时的图案化限制是imec与其材料供应商合作的主要任务。

但向更小特征和更薄抗蚀剂薄膜的过渡也对计量提出了挑战。比以往任何时候都强烈需要同时解决图案和计量机会——一个服务于另一个的需求。例如,当抗蚀剂变得超薄时,印刷线内的材料量会变得非常小,以至于很难用当前使用的计量工具“看到”。例如,对于广泛使用的 CD-SEM,使用更薄的抗蚀剂会导致图像对比度大大降低。最近的实验表明,底层的类型(即光刻胶膜下面的层)可以对 SEM 成像对比度产生积极影响。但是使用不同的底层来改进计量将反过来影响图案转移,需要优化蚀刻工艺。为了继续优化模式转移,

图 2:抗蚀剂膜厚度减少的演变(HP = 半间距)。

下面,我们将介绍最近在图案化和计量方面的一些见解。

评估模式转移的限制

作为对第一个高 NA EUV 原型制作系统的预期,imec 使用目前最先进的 0.33NA EUV 光刻系统 NXE:3400B 来预测更薄的抗蚀剂的性能——包括线路/空间和接触孔。早些时候,imec 和 ASML 能够使用这款 NXE:3400B 扫描仪打印最小间距(即 24nm 间距线/间距和 28nm 间距接触孔),从而实现高 NA EUV 光刻扫描仪所需的早期材料开发。

例如,通过使用该工具,该团队表明,线边缘和线宽粗糙度 (LER/LWR)——在图案化线/空间的最关键参数中——在使用更薄的抗蚀剂薄膜时往往会增加。在这些实验中,使用了化学放大抗蚀剂 (CAR),这是一种依赖于当 EUV 光子撞击表面时在抗蚀剂内形成的电子的化学放大的抗蚀剂。自 1990 年代初以来,这些 CAR 已在工业中大量使用,并已逐渐优化以获得更好的抗蚀剂性能。但对于高数值孔径光刻,该行业可能需要 CAR 以外的抗蚀剂,具有更好的分辨率。因此,我们看到了新型光刻胶材料的出现,例如金属氧化物抗蚀剂 (MOR)。我们的第一个实验似乎表明这些 MOR 对于更小的特征和更薄的抗蚀剂确实具有更好的图案转移能力。Imec 与多家材料供应商合作开发这些概念并评估诸如污染风险和工艺集成挑战等关键问题。

图 3:观察到缩小 EUV 抗蚀剂膜厚度会增加线宽粗糙度 (LWR)。

高 NA EUVL:计量的机会

如前所述,计量学的第一个主要挑战是需要应对目前使用的 CD-SEM 工具降低的图像对比度。Imec 看到了两种方法来解决这个问题,并继续测量用更薄的抗蚀剂印刷的非常小的线条。第一种方法是调整工具的设置。使用 CD-SEM 工具的某些旋钮(例如扫描速率)结果证明会对成像对比度产生积极影响——即使在薄膜厚度低至 15nm 时也能看到图案。第二种方法是与imec 的计量供应商密切合作,探索替代计量技术。在分辨率方面非常有前途的是例如低压 SEM、氦离子显微镜、散射仪……

图 4:减少抗蚀剂膜厚度(从 30nm 到 10nm)(上)对 CD SEM 图像对比度产生负面影响,但(中)可以通过使用 CD-SEM 计量旋钮或(下)使用不同的底层来改善。

除了例如 10nm 宽度的线之外,图案内还有更小的特征需要成像。随着缩放的继续,测量 LER 和覆盖性能(即一层与下一层的对齐程度)等参数变得更加困难——需要远低于 10nm 的图像分辨率。然后是缺陷,更具体地说,随机打印故障的出现:随机的、非重复的、孤立的缺陷,例如微桥、局部断线和缺失或合并的触点。它们被认为是由能量和波长之间的基本关系产生的。随着波长越来越短——EUV 光刻在 13.5nm 下运行——来自光源的能量分布在更少的光子上。因此,只有几个光子可以创建一个图案。

具有进一步提高的分辨率和减小的抗蚀剂厚度的高 NA EUV 光刻技术的出现将进一步推动这一发展。Imec 一直在开发方法来系统地量化 EUV 材料中的缺陷水平,并了解导致故障的许多因素。关键是传统上依赖光学技术的晶圆检测策略的发展和改进。最近,基于电子束的检测越来越受到关注。尽管它在发现小缺陷方面看起来很有希望,但它也有一个主要缺点:检查整个晶圆所需的时间急剧增加——需要解决方案来提高工具生产率和吞吐量。

此外,越来越多地设置金属化图案的电气测试,以寻找与通过光学和电子束检测技术获得的数据的相关性。这允许增加对随机模式失败的学习,并获得更多关于它们影响产量的方式的见解。通过这种方式,使用扫描电子显微镜、宽带等离子光学和电子束技术获得的缺陷检测数据已经可以成功地与从电气测量获得的数据相关联。电气测试是在允许测量电开路(以及因此抗蚀剂中的桥)的大面积钌金属化蛇形结构以及允许测量电学的金属化叉叉和尖端对尖端结构上进行的。短裤(因此抵抗中的关键断裂)。

掩模技术:充分利用高 NA EUV 光刻技术的另一个关键因素

光掩模是芯片制造的重要组成部分,因为它保存了用于最终设备的设计布局信息。理想情况下,该信息包含在掩模上的暗(即吸收)和亮(即反射)区域中。现在正在打印越来越小的特征,与理想掩模的偏差越来越多地影响最终的晶圆图案。因此,需要解决口罩的具体挑战。其中包括减少掩模 3D 效果、增强对掩模寿命及其对打印随机故障的贡献的理解。最重要的是,在高 NA EUVL 光学系统中引入畸变会给掩模行业带来额外的复杂性。在这一切中,imec 团队扮演着重要的角色。通过与 ASML 及其材料供应商的密切合作,imec 致力于设计优化和认证用于高 NA EUV 光刻的光掩模。下文将更详细地描述这项工作。

用于减少掩模 3D 效果的新型吸收材料

今天的 EUV 掩模由约 300nm 厚的反射多层堆叠组成,由 40 到 50 层交替的硅 (Si) 和钼 (Mo) 层组成,覆盖着一层薄的钌层。在这个堆栈上,由钽硼硝酸盐 (TaBN) 制成的吸收器带有图案。当 Mo 和 Si 的多层反射入射光时,吸收器阻挡反射,这种组合定义了晶片上的特征。

图 5:EUV 光掩模的卡通横截面

当前的基于 Ta 的吸收器的厚度通常约为 60-70nm,旨在吸收足够量的光。与光的 13.5nm 曝光波长相比,该厚度较大。因此,以特定入射角(在传统 EUV 光刻中以 6° 为中心)照射掩模并从多层反射的光对“厚”掩模的 3D 形貌敏感,例如经历多层和吸收体诱导相变形。这会扭曲空中图像——最终转移到光刻胶中的光图案——并降低其图像对比度。这些所谓的掩模 3D 效果还伴随着更多的与特征相关的放置变化和对晶圆的最佳聚焦。这对已经受到 DOF 预算减少的高 NA EUV 光刻提出了额外的挑战。

最初,应用源照明和掩模设计的创新来补偿掩模 3D 效果。近年来,注意力正转向改进掩模材料作为控制晶圆上掩模 3D 效应的参数,从而有助于提高高 NA DOF。

这推动了 imec 研究探索新的吸收材料,这些材料要么具有不同的 EUV 折射率(低 n 材料,如 RuTa 或 PtMo,允许衰减相移),要么具有高 EUV 消光系数(高 k 材料,如 PtTe 或Ni具有高吸收能力)。对于每种材料类型,都需要优化厚度以实现最佳成像权衡。Imec 正在进行材料筛选,以寻找这些材料中最有前途的材料。基于这些材料的新掩模架构预计将在今年年底前在 imec 的当前 EUV 扫描仪上进行测试。

图 6:EUV 掩模吸收材料空间与参考 TaBN

变形面具来了

高数值孔径 EUV 光刻技术对扫描仪内的光学器件进行了重大重新设计,允许具有更大入射角的光照射到晶圆上,从而使系统具有更高的分辨率。在相同的扫描仪放大倍率下,这会带来一个缺点。具有更高入射角的光也会照射到掩模上,如果不采取行动,这将大大恶化 3D 掩模效果。

克服这些额外阴影效应的一种方法是将掩模放大率从其历史的 4 倍增加到 8 倍,并结合使用更大的掩模空白。但放弃最初的 6 英寸 x 6 英寸面罩尺寸,同时保持较高的面罩质量将极大地影响面罩行业。为了尽量减少这种影响,ASML 和蔡司推出了变形镜头,一种在 x 和 y 方向(分别为 4x 和 8y(y 是扫描方向))具有不同放大倍率的镜头。保留了 6 英寸面罩,但其设计向一个方向拉伸。增加的放大倍率(在一个方向上)将图像场大小(即,在一个步骤中曝光的晶片部分)缩小到一半,因此扫描仪最终可能仅在设备的一部分上打印特征。对于具有较大裸片尺寸的芯片尤其如此,这对如何设计这些芯片施加了限制。对于这些芯片,芯片制造商必须采用一种称为缝合的技术。图案的一部分用一个蒙版曝光,下一部分用第二个蒙版曝光,两个蒙版缝合在一起。Imec 研究改进缝合的方法,例如通过减少两个面罩之间固有的所谓过渡区。在硬件方面,ASML 致力于加速掩模和晶圆阶段,以弥补半场成像造成的生产力损失。并将两个面具缝合在一起。Imec 研究改进缝合的方法,例如通过减少两个面罩之间固有的所谓过渡区。在硬件方面,ASML 致力于加速掩模和晶圆阶段,以弥补半场成像造成的生产力损失。并将两个面具缝合在一起。Imec 研究改进缝合的方法,例如通过减少两个面罩之间固有的所谓过渡区。在硬件方面,ASML 致力于加速掩模和晶圆阶段,以弥补半场成像造成的生产力损失。

图 7:掩模示意图,以及在 0.55NA 扫描仪上打印期间掩模和晶圆的主要方向(由 ASML 提供)

薄膜开发

在光刻技术中,光掩模通常与薄膜一起被提及——薄膜是用于在大批量半导体制造过程中保护掩模免受污染的薄膜。它安装在光掩模表面上方几毫米处,因此如果颗粒落在薄膜上,它们将离焦太远而无法打印。然而,开发 EUV 薄膜并不简单。所有 EUV 扫描仪都面临的一个主要挑战是使薄膜吸收尽可能少,以保持 EUV 光刻的吞吐量和经济性。此外,薄膜必须能够承受未来光刻工具不断增加的 EUV 功率,包括高 NA EUV 光刻工具——8 倍放大倍率带来了薄膜和掩模级别功率密度降低的好处。艾美克,与合作伙伴合作,开发了一种创新的基于 CNT 的薄膜解决方案,该解决方案有可能在超过 600 瓦的扫描仪功率下存活。CNT 薄膜的可行性已通过在 imec 的 EUV NXE:3300 扫描仪上的使用得到成功证明。该团队现在正在努力延长使用寿命,以实现适用于下一代 EUV 光刻工具(包括高 NA)的高生产率薄膜解决方案,其光罩加速度大大提高。

图 8:类似于 imec 的 NXE:3300B 中暴露的全尺寸 CNT 薄膜

从商品到关键部件……

该团队专注于其他特定于面具的机会,例如面具生命周期的理解。掩膜在储存时会发生碳生长,这会影响印在晶圆上的特征的关键尺寸。观察到该效果取决于存储条件,并且可以通过 EUV 曝光来逆转。该研究揭示了尽可能控制和最小化存储和寿命影响的重要性,以实现稳定的掩模印刷性能。另一个挑战与掩模缺陷对随机故障概率的贡献增加有关。观察到随着掩模老化而增加的掩模多层的表面粗糙化起着至关重要的作用。这推动了替代多层“镜面”材料的研究。此外,与以往相比,掩模上的小缺陷,例如边缘放置错误或 CD 错误,会转化为晶圆印刷后观察到的错误。现在情况变得更糟了,因为晶圆在覆盖、聚焦和边缘放置误差方面的预算已经变得非常小,这是缩放的直接后果。这促使需要大规模量化掩模对晶圆成像性能的贡献。此外,正在研究以更精确和更小分辨率写入掩模的其他方法,包括多光束掩模写入,它允许不同(所谓的曲线)掩模形状。所有这些都表明,掩模正从“简单”的商品演变为对晶圆成像性能越来越重要的复杂组件。现在情况变得更糟了,因为晶圆在覆盖、聚焦和边缘放置误差方面的预算已经变得非常小,这是缩放的直接后果。这促使需要大规模量化掩模对晶圆成像性能的贡献。此外,正在研究以更精确和更小分辨率写入掩模的其他方法,包括多光束掩模写入,它允许不同(所谓的曲线)掩模形状。所有这些都表明,掩模正从“简单”的商品演变为对晶圆成像性能越来越重要的复杂组件。现在情况变得更糟了,因为晶圆在覆盖、聚焦和边缘放置误差方面的预算已经变得非常小,这是缩放的直接后果。这促使需要大规模量化掩模对晶圆成像性能的贡献。此外,正在研究以更精确和更小分辨率写入掩模的其他方法,包括多光束掩模写入,它允许不同(所谓的曲线)掩模形状。所有这些都表明,掩模正从“简单”的商品演变为对晶圆成像性能越来越重要的复杂组件。这促使需要大规模量化掩模对晶圆成像性能的贡献。此外,正在研究以更精确和更小分辨率写入掩模的其他方法,包括多光束掩模写入,它允许不同(所谓的曲线)掩模形状。所有这些都表明,掩模正从“简单”的商品演变为对晶圆成像性能越来越重要的复杂组件。这促使需要大规模量化掩模对晶圆成像性能的贡献。此外,正在研究以更精确和更小分辨率写入掩模的其他方法,包括多光束掩模写入,它允许不同(所谓的曲线)掩模形状。所有这些都表明,掩模正从“简单”的商品演变为对晶圆成像性能越来越重要的复杂组件。

AttoLab:加速高NA图案化生态系统的发展

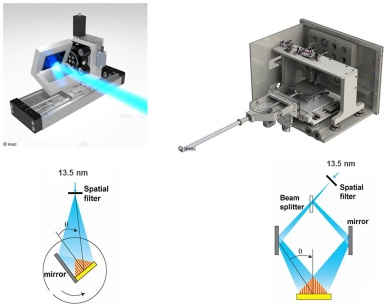

需要加快对薄光刻胶成像的学习是imec 决定投资与KMLabs 的联合项目AttoLab 的原因之一。该实验室使我们能够在 ASML 的第一个 0.55NA EXE:5000 原型面世之前探索高 NA EUV 光刻条件下光刻胶成像的基本动力学。实验室中的实验装置在 0.33NA EUV 光刻扫描仪已经获得的基础上提供了相应的见解。

在 AttoLab 中,13.5nm 的高 NA 曝光通过干涉型设置中的明亮、相干、高谐波 EUV 源进行模拟。最近,通过用于试样实验的基于劳埃德镜的干涉装置,20nm 节距线/空间首次可以在金属氧化物光刻胶中成功地在 imec 成像。在这种布置中,从镜子反射的光会与 13.5nm 高谐波发生源直接发射的光发生干涉,从而产生适合抗蚀剂成像的精细干涉图案。可以通过改变干涉光束之间的角度来调整成像的抗蚀剂图案的间距。此 Lloyd's-Mirror 设置为下一步提供了重要的学习信息:

基于干涉的 EUV 光源与 ASML 的高 NA EUV 激光器中使用的方法不同,后者将锡滴蒸发以产生 EUV 光。光子随后从扫描仪内的几个镜子反弹,从掩模反射,最后撞击晶片上的抗蚀剂。虽然 ASML 的扫描仪专为芯片的大规模生产而设计,但 AttoLab 中使用的干涉型工具永远无法达到所需的全场吞吐量。

但是对于这些 13.5nm 飞秒包络阿秒激光脉冲,imec 正在追求不同的目标:研究随后在光刻胶材料中引起的 EUV 光子吸收和超快辐射过程,并了解更多关于关键随机打印失败的信息。对于这些研究,光束线与时间分辨红外和光电子光谱等光谱技术相结合,并且正在建立相应的泵浦探针类型的实验。光束线设计用于在几秒钟内在高 NA 条件下筛选各种抗蚀剂材料,并支持开发适用于高 NA EUV 光刻的优化图案、蚀刻和计量技术。

图 9:用于高 NA EUV 干扰试样实验的(左)劳埃德镜设置示意图(未按比例);(右)用于全 300 毫米晶圆实验的干涉室

结论

从 0.33NA 到 0.55 高 NA EUV 光刻技术的转变为光刻行业提供了一个重要的机会,可以在很短的时间内共同应对挑战并为该工具的推出做好准备。imec 与 ASML 在联合的高 NA EUV 实验室中专注于与高 NA 扫描仪开发相关的基础设施准备工作。为此,imec依靠并邀请所有材料和设备供应商为建立完整的高NA生态系统做出贡献。所有这些努力的回报将是巨大的,因为 0.55NA EUV 光刻工具有望将摩尔定律推向 2nm 甚至更远的技术世代。

致谢

这项工作是imec 高级图案化团队与imec 的设备和材料供应商密切合作的结果。

审核编辑 黄昊宇

-

光刻机

+关注

关注

31文章

1201浏览量

49027

发布评论请先 登录

高数值孔径投影光刻中的偏振效应

嵌入式开发是否会成为下一个被看好的领域?

双色调显影-------光学光刻和极紫外光刻

光刻胶剥离工艺

【原创】TDMS设置下一个写入位置函数的摸索

AI玩具或成为下一个万亿新赛道

无人配送车卷至不到2万元,激光雷达下一个增量市场来了

改善光刻图形线宽变化的方法及白光干涉仪在光刻图形的测量

高NA EUVL:光刻的下一个主要步骤

高NA EUVL:光刻的下一个主要步骤

评论