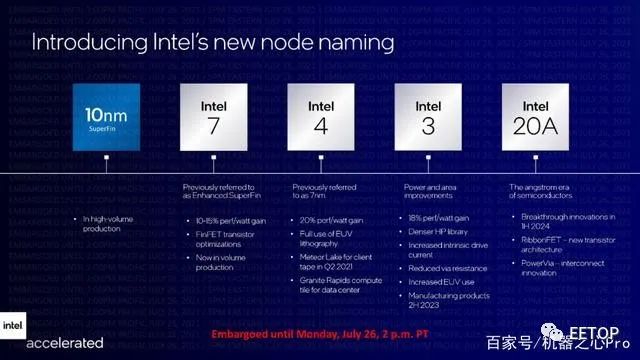

对于英特尔来说,Intel 4 是一个重要的里程碑,它既是英特尔第一个集成 EUV 的工艺,也是第一个跳出陷入困境的 10nm 节点的工艺。

本周举行的 IEEE 年度 VLSI 研讨会是业界披露和探讨新芯片制造技术的重大活动之一。今年最受期待的演讲之一莫过于英特尔介绍的 Intel 4 工艺的物理和性能特征,该工艺计划将用于 2023 年的产品中。

Intel 4 工艺对于英特尔来说是一个重要的里程碑,因为它是英特尔第一个集成 EUV 的工艺,也是第一个跨越陷入困境的 10nm 节点的工艺。对于英特尔而言,Intel 4 将助其重新夺回晶圆厂的霸主地位。

英特尔本来计划在当地时间周二发表题为「Intel 4 CMOS 技术,采用面向高密度和高性能计算的高级 FinFET 晶体管」的演讲。但在展会开始之前,英特尔重新发布了有关 Intel 4 的相关数据,让我们第一次看到了该工艺的更多信息。

Intel 4 即为以前的英特尔 7nm 工艺,是其第一次在芯片上采用 EUV 光刻技术。EUV 的使用保证了英特尔可以绘制出更先进制造节点所需的更小特征,同时使其通过多模式 DUV 技术减少制造步骤。

Intel 4 的研发对英特尔来说是一个关键节点,最终摆脱了 10nm 工艺。英特尔虽然已经竭力制造出适合 10nm 工艺节点的产品,尤其是最近的 10nm 增强 SuperFin 变体(我们熟悉的 Intel 7)。但英特尔试图通过 10nm 在缩放和大量新制造技术等方面一次实现太多事情,却导致其出现了倒退。

因而,英特尔在第一个 EUV 节点上可能不会采取太过激进的策略,总体采用更加模块化的开发方法,逐步实现新技术,并在必要时进行调试。

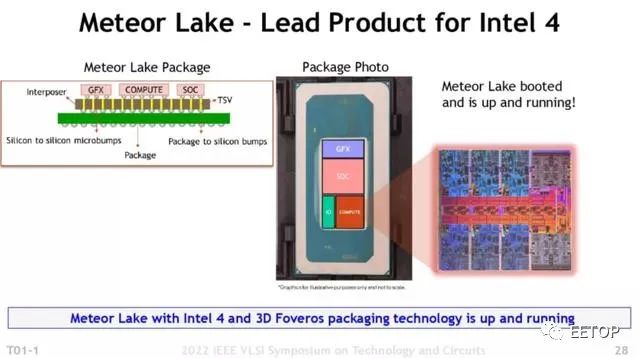

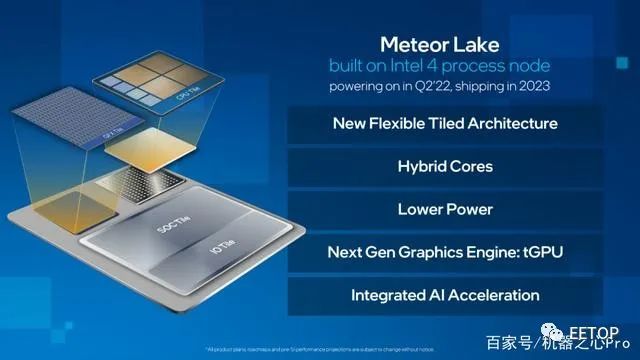

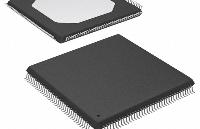

Intel 4 将首先用于英特尔即将推出的 Meteor Lake 客户端 SoC,该 SoC 有望成为英特尔 14 代酷睿处理器系列的基础。尽管要 2023 年出货,但英特尔已经在实验室中启动并运行了 Meteor Lake。

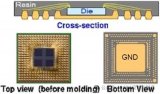

除了在工艺技术取得显著进步之外,Meteor Lake 还将成为英特尔首个基于 tile/chiplet 的客户端 CPU,它混合使用了 I/O、CPU 核心和 GPU 核心的 tile。

Intel 4 物理参数:密度是 Intel 7 的两倍,继续使用钴

对于 Intel 4 工艺,英特尔着手解决一些不同的问题。首先是密度,英特尔仍在努力保持摩尔定律的生命力,更高的晶体管密度可以在相同的硬件下提供更小的芯片,或者通过更新的设计集成更多的核心(或其他处理硬件)。

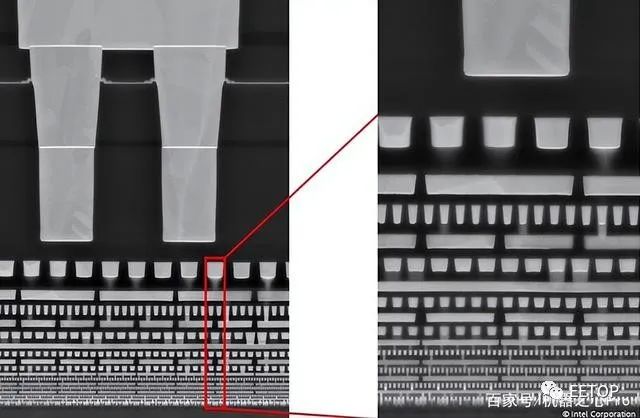

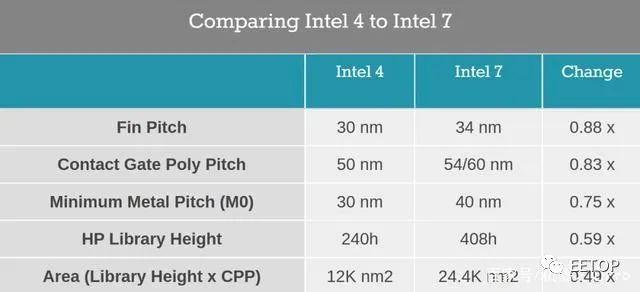

根据英特尔公布的数据,Intel 4 的鳍片间距降至 30nm,是 Intel 7 34nm 间距的 0.88 倍。同样,接触栅之间的间距也有之前的 60nm 降至了 50nm。最重要的是,最下层(M0)的最小金属间距也为 30nm,是 Intel 7 上 M0 间距大小的 0.75 倍。

此外,英特尔的 Library Height 也降低了,Intel 4 上高性能(HP)库的单元高度为 240nm,仅是 Intel 7 上单元高度的 0.59 倍。因此英特尔称 Intel 4 的密度比 Intel 7 增加了两倍,晶体管的尺寸减少了一半,这意味着传统的、全节点晶体管密度的改进。

由于芯片是 2D 结构,英特尔使用的度量标准是将 HP 单元高度乘以接触的多晶硅间距。在这种情况下,Intel 7 的单元面积为 24,408 nm^2,Intel 4 为 12,000 nm^2,后者是前者单元面积的 0.49 倍。

不过,Intel 4 上的 SRAM 单元大小仅为 Intel 7 上相同单元的 0.77 倍左右。因此,虽然标准化逻辑单元的密度翻了一番,但 SRAM 密度仅提升了 30% 左右。

此外,英特尔虽然也谈及了标准单元的密度,但并没有正式披露实际的晶体管密度数据。目前,英特尔给出的说法是,总体晶体管密度降为目前提供的 2x 倍。Intel 7 的 HP 库的密度为 8,000 万个晶体管 /nm^2,Intel 4 的 HP 库的密度大约为 60MTr/mm^2。

这些数字都是针对英特尔低密度高性能库,因此高密度库会成为后续明显的问题。传统上,这些数字会进一步压缩以换取时钟速度的降低。然而,英特尔不会为 Intel 4 开发高密度库。Intel 4 将是一个纯粹的高性能节点,高密度设计将伴随下一代 Intel 3 到来。

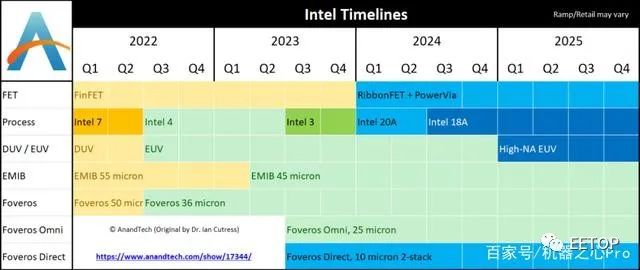

这种不寻常的研发策略来源于英特尔在工艺节点开发中的模块化努力。在接下来五年左右,英特尔基本上会采取稳健的节点开发策略,基于 EUV 或 High-NA 机器开发一个初始节点,然后在此基础上推出更加精炼或优化的继任者。就 Intel 4 而言,虽然它在英特尔的发展中为 EUV 做了重要的开创性工作,但该公司未来更希望 Intel 3 成为更长寿的 EUV 节点。

这一切都意味着不需要 Intel 4 的高密度库,英特尔计划在一年左右的时间里让功能更全面的 Intel 3 所取代。Intel 3 在设计上与 Intel 4 兼容,因此可以清楚地看到英特尔在时间允许的情况下推动自己的设计团队使用后者的流程。英特尔代工服务客户也将面临相似的情况,他们可以使用 Intel 4,但 IFS 需要更专注于提供对 Intel 3 的访问和设计帮助。

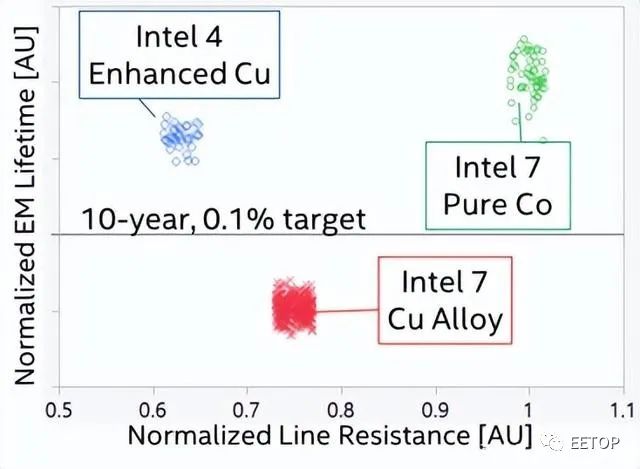

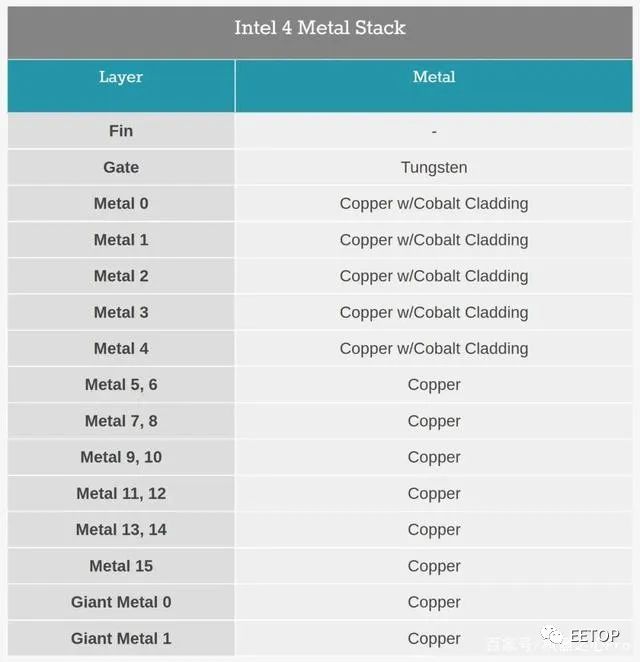

回到 Intel 4 本身,与英特尔的 10nm 工艺制程相比,新节点对金属层有了重大改变。英特尔在其 10nm 工艺制程的最底层用钴取代了铜,该公司认为这可以延长晶体管寿命。遗憾的是,从性能(时钟速度)来讲,钴的性能其实没有那么好,长期以来,人们一直怀疑,改用钴是英特尔 10nm 开发的主要障碍之一。

对于 Intel 4,该公司仍在生产过程中使用钴,但现在不再使用纯钴,而是使用所谓的增强型铜(Enhanced Copper,eCu),即铜包覆钴。eCu 将二者结合起来,这样既能保证掺杂铜金属化层的性能,又能获得钴的电迁移电阻优势。

虽然英特尔不再使用纯钴,但在某些方面,他们对钴的使用总体上在增加。英特尔的 10nm 工艺仅在接触栅极和前两层金属层中使用了钴,而 Intel 4 正在将 eCu 的使用扩展到前 5 层。因此,英特尔芯片中最低三分之一的完整金属层堆叠使用的是钴包铜。然而英特尔已经从栅极本身中移除了钴,现在是纯钨,而不是钨和钴的混合物。

总体来说,Intel 4 的金属层数量比 Intel 7 有所增加,后者有 15 个用于逻辑的金属层,而 Intel 4 有 16 层。

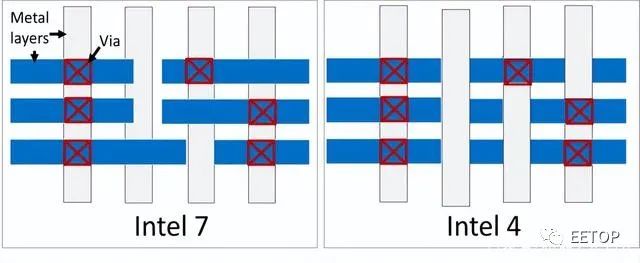

除了更加紧密的栅极和金属层 pitches,英特尔在改变互连设计方面也改进较大。在 Intel 4 中,英特尔已经转向网格互连设计。简而言之,Intel 4 只允许 Via 通过预先确定的网格在金属层之间,而此前 Via 可以放置在任何地方。

英特尔表示,网格的使用通过减少可变性以及优化设计提高了工艺的产量。这一改变还有一个额外好处,使英特尔不必为互联使用复杂、多模式的 EUV。

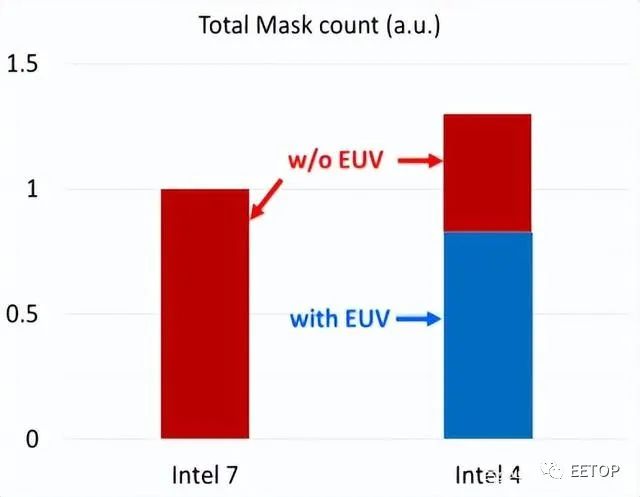

EUV 的使用使得英特尔减少了制造芯片所需的步骤和掩膜数量。虽然没有给出绝对数字,但 Intel 4 需要的掩膜数量比 Intel 7 减少了 20%。

此外,EUV 的使用也对英特尔产生了积极的影响,虽然该公司没有提供确切的数字。

Intel 4:频率提高 21.5%,功耗降低 40%

除了密度方面的改进,英特尔在频率和能效方面都取得了高于平均水平的提升。

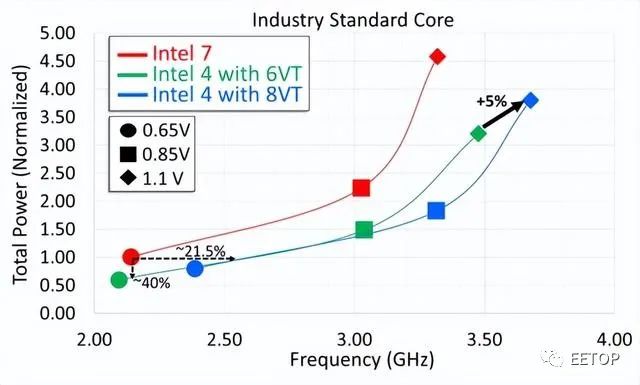

行业标准核心的电路分析显示,在匹配功率为 0.65V 时,Intel 4 性能比 Intel 7 提高了 21.5%;在高电压下,匹配功率 8VT 比 6VT 可获得 5% 的性能增益。

在等功率为 0.65v 的情况下,与 Intel 7 相比,Intel 4 的时钟速度提高了 21.5%。在 0.85v 及以上时,等功率增益接近 10%。

Intel 4 在电源效率方面收益更大,在等频即 2.1GHz 左右,Intel 4 的功耗降低了 40%。随着频率的增加,收益递减。

总而言之,英特尔是在不断提升产品性能,例如在去年夏天的工艺路线图更新中讨论的 Intel 4 的每瓦性能提升 20%,去年,英特尔一直在接近 Intel 4 开发的终点线,因此正如他们所预想的那样,英特尔似乎正在实现性能提升。

与此同时,英特尔也报告称从 Intel 7 到 Intel 4,他们在成本上取得了良好的发展,不过该公司没有提供具体数字。1 EUV 层确实比 1 DUV 层更贵,但由于 EUV 消除了一堆多重模式(a bunch of multi-patterning),这有助于通过减少总步骤数来降低总成本。改用 EUV 也减轻了英特尔的资金压力。

最后,英特尔希望在 2023 年推出 Meteor Lake 和第一代 Intel 4 产品,英特尔能够以多快的速度让其新工艺节点启动并付诸到大批量制造的标准,还有待观察。不过由于 Meteor Lake 样品已经在英特尔的实验室中,英特尔离最终进入 EUV 时代越来越近。但对于英特尔来说,要实现所有的目标,不仅意味着要扩大希尔斯伯勒工厂的产量,还意味着要将他们的工艺迁移到生产 Intel 4 的工厂。

审核编辑 :李倩

-

英特尔

+关注

关注

61文章

10324浏览量

181092 -

intel

+关注

关注

19文章

3511浏览量

191647 -

EUV

+关注

关注

8文章

615浏览量

88960

原文标题:Intel 4工艺细节曝光:较上代性能提升21%、功耗降低40%

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

onsemi FDMS4D4N08C N-Channel MOSFET:高性能与可靠性的完美结合

探索 onsemi FDP4D5N10C 和 FDPF4D5N10C MOSFET:高性能与可靠性的完美结合

深入解析AD7323:高性能4通道12位ADC的特性、原理与应用

晶圆工艺制程清洗方法

探索PE42641:UltraCMOS®工艺下的高性能SP4T RF开关

进程概念和特征

暂降的波形特征在判断电网问题和装置误判时有多大的参考价值?

德承新款工控机P2302系列全面搭载新一代 Intel® Meteor Lake-PS Core™ Ultra 7/5/3 处理器

Intel OCP 3.0用E610-IT4以太网网络适配器数据手册

aQFN封装芯片SMT工艺研究

Simcenter STAR-CCM+多物理场解决方案:支持在设计早期对实际性能进行预测

Intel 4工艺的物理和性能特征

Intel 4工艺的物理和性能特征

评论