引言:我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

Xilinx 7系列FPGA管脚是如何定义的

原理图设计时如何下载FPGA管脚文件(Pinout文件)

1.Xilinx7系列FPGA管脚定义

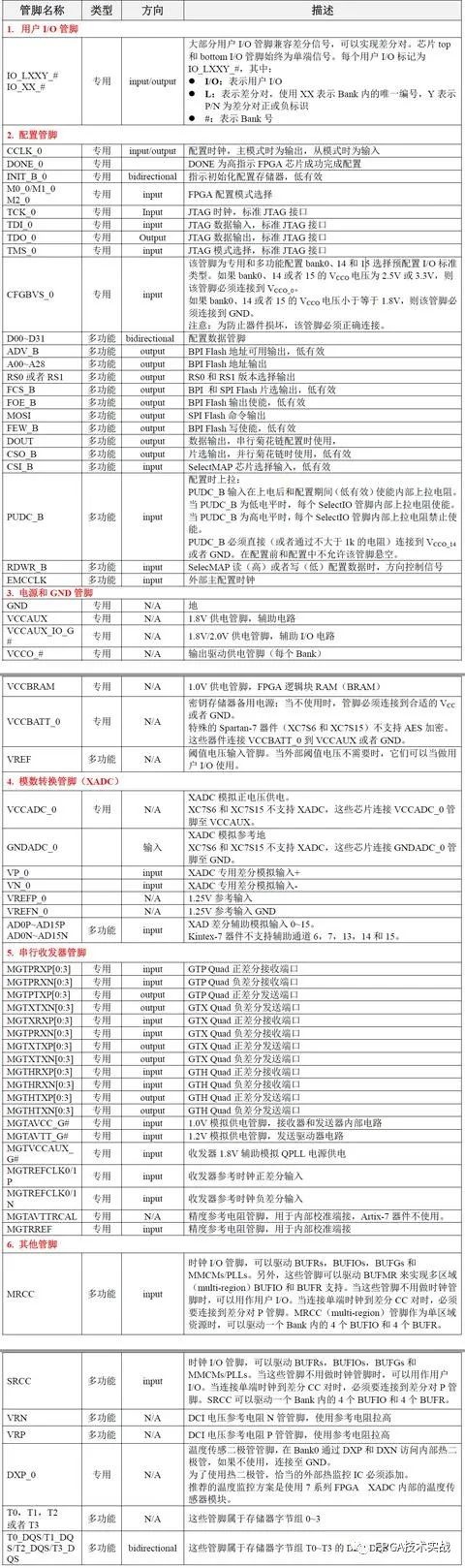

表1-1列出了7系列FPGA封装中的管脚定义。注意:表1-12有单独列出的专用通用用户I/O,也有标记IO_LXXY_ZZZ#或者I/O_XX_ZZZ_#标识的多功能I/O,其中ZZZ代表一种或几种附加的功能。如果多功能I/O不用做特殊用途,它们可以当作普通I/O使用,这一点我们在硬件设计时要注意。

表1-1、Xilinx 7系列FPGA管脚定义

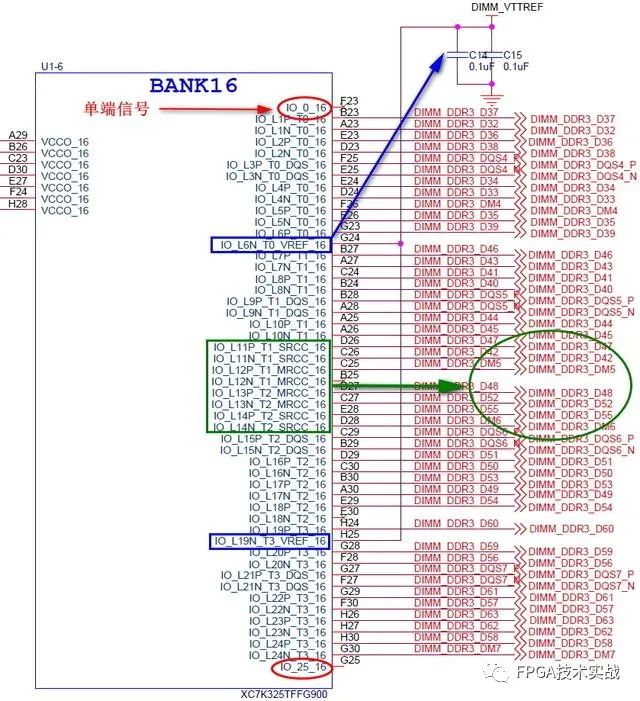

FPGA的器件管脚按照Bank进行划分,每个Bank独立供电,以使FPGA I/O适应不用电压标准,增强I/O设计的灵活性。每个用户Bank包括50个I/O管脚或者24对差分对管脚(48个差分信号),Top和Bottom各一个单端管脚。图1给出了K325T芯片用户Bank IO原理图举例。

图1、K325T芯片用户Bank IO原理图

在图中,我们可以看到红色圈住的两个单端信号,绿色线条圈住的_CC时钟管脚不用作时钟输入时可以作为用户I/O来使用,另外,还可以看到蓝色标记的VREF管脚,当该BANK I/O用作DDR内存接口时,需要提供伪差分所需的阈值电压,此时_VREF_管脚需要接DDR外设要求的参考电压。其他I/O管脚分析,可以参考表1-1管脚定义说明。

2.Xilinx7系列FPGA管脚Pinout文件下载

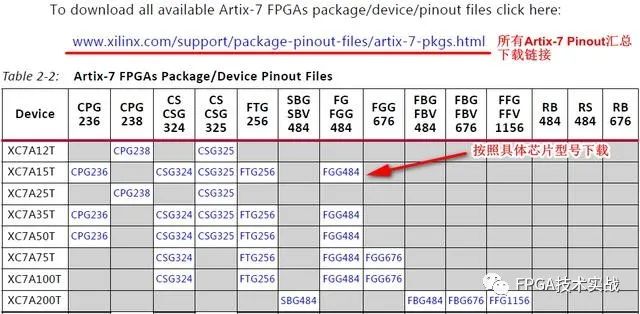

我们在进行原理图库设计时,如何获得FPGA每个管脚定义呢?在UG475官方文档第二章7 Series FPGAs Package Files的ASCII Pinout Files子节中,按照FPGA器件家族和器件封装分类,给出了7系列所有器件Pinout定义链接地址。官网给出CSV和TXT两种格式Pinout文件,我们可以灵活选择。

图2、FPGA Pinout下载链接

图3、Xilinx官网下载Pinout

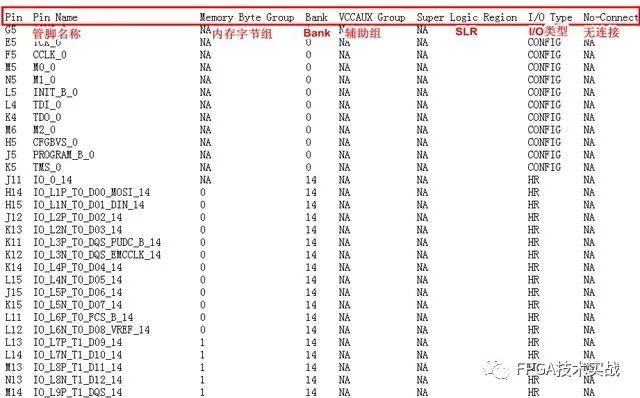

我们打开一个.TXT形式的Pinout,如图4所示。可以看到,文件分为8列,包含所有设计原理图所需的关键信息:管脚编号、管脚名称、管脚DDR内存分组、管脚BANK编号、辅助组(VCCAUX)、超级逻辑域(SLR)、I/O管脚类型(配置、HR、HP、收发器管脚等)以及与器件Pin-to-Pin兼容相关的NC管脚信息。

图4、Pinout文件内容举例

审核编辑 :李倩

-

FPGA

+关注

关注

1664文章

22504浏览量

639300 -

pcb

+关注

关注

4417文章

23967浏览量

426180 -

Xilinx

+关注

关注

73文章

2208浏览量

131908

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

Xilinx FPGA输入延迟原语介绍

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

使用Xilinx 7系列FPGA的四位乘法器设计

Xilinx FPGA串行通信协议介绍

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

一文详解xilinx 7系列FPGA配置技巧

Xilinx 7系列FPGA管脚是如何定义的

Xilinx 7系列FPGA管脚是如何定义的

评论