过去十年,AI算法和芯片架构的不断创新,以及AI市场应用规模范围的不断扩大,两者互相促进,给算法、架构、软硬件集成、芯片设计都带来了令人激动的新机遇。据麦肯锡研究报告预测,到2025年全球AI芯片市场预计将达到100亿美元的规模。同时,算法和架构创新也给EDA流程中的芯片设计和验证带来了新的挑战,需要新一代的EDA流程和工具的支持。

AI芯片设计与验证挑战

燧原科技资深架构师鲍敏祺表示:

“AI芯片往往具备超大的设计规模,同时,AI算法和应用的迭代周期短,因此在计算子系统、调度控制子系统、存储子系统、高速通信子系统等多个领域,都提出了更高的设计要求。面对复杂的设计需求,AI芯片在验证策略选择上,也往往需要引入多种验证手段,提前通过仿真、形式化验证、FPGA原型验证等一系列验证手段发现问题,确保芯片在功能、功耗、调度性能等方面达到设计期望。”

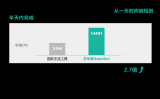

AI芯片设计结构复杂,不同子系统往往具备差异化的验证重点,也就需要不同的验证工具组合,实现验证效果的最大化。然而业内人士普遍认为,当前验证环节点工具各自为政带来的高门槛和低效率,特别是“工具缺乏兼容性、数据碎片化、工具缺乏创新”等痛点,已成为目前芯片设计追求更快、更强、更简单的三大阻碍。有数据显示,每种工具在验证中的激励移植、重复编译、碎片化调试所浪费的时间通常占到总体验证时间的30%以上。

AI芯片高效验证之道

芯华章科技验证工程副总裁朱洪辰表示:

“面对这些挑战,去年芯华章正式推出了从底层框架全新构建的智V验证平台,具备‘协同、易用、高效’三大优势,能让工具带来1+1》2的验证效益,有效地解决产业正面临的兼容性挑战,以及数据碎片化导致的验证效率挑战。”

基于智V验证平台,芯华章目前已经推出了多款数字验证工具,涵盖FPGA原型验证、逻辑仿真、形式验证、智能场景验证、系统调试等领域。

芯华章科技验证工程总监高世超介绍:

“为了提高AI芯片验证效率,芯华章提供了融合高效的AI芯片验证调试解决方案。我们的形式化验证工具GalaxFV可与仿真技术结合,加速AI验证覆盖率收敛;智能场景验证工具GalaxPSS,能够利用场景建模自动生成跨平台、可复用、智能化自回归的测试激励;数字验证调试系统Fusion Debug则贯穿所有工具,提供了跨平台的高效调试解决方案。”

芯华章科技验证工程总监刘勤一表示:

“FPGA原型验证对于提升超大规模的AI芯片设计效率,具备得天独厚的技术解决优势。基于FPGA硬件和拥有自主知识产权的全流程软件,芯华章自主研发的高性能FPGA原型验证系统桦捷(HuaPro-P1),可以帮助SoC/ASIC芯片客户实现设计原型的自动综合、分割、优化、布线和调试,从而有效减少用户人工投入,提升系统验证与软件开发效率,缩短芯片设计周期。”

原文标题:对话燧原科技 | 芯华章带来AI芯片高效验证之道

文章出处:【微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22502浏览量

639133 -

AI

+关注

关注

91文章

41073浏览量

302573 -

验证系统

+关注

关注

0文章

28浏览量

10487 -

芯华章

+关注

关注

0文章

195浏览量

12013

原文标题:对话燧原科技 | 芯华章带来AI芯片高效验证之道

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

基于FPGA的DAQ系统|实现高性能数据采集的挑战

是德科技与联发科技联合完成一项工作原型验证

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

FPGA原型验证实战:如何应对外设连接问题

【喜报】芯神瞳原型验证解决方案荣膺工博会“集成电路创新成果奖”

芯华章与守正通信达成战略合作

西门子桌面级原型验证系统Veloce proFPGA介绍

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

芯华章高性能FPGA原型验证系统实现设计原型自动综合、布线和调试

芯华章高性能FPGA原型验证系统实现设计原型自动综合、布线和调试

评论