很难相信自 PCI 特别兴趣小组 (PCI-SIG) 发布 PCI Express Base Specification Revision 2.0 以来已经过去了两年。通常称为 PCIe Gen 2,升级到流行且广泛使用的 PCIe 协议后,PCIe Gen 1 支持的带宽翻了一番,达到 5.0 Gbps。但这并不是新规范的全部可能。

虽然第 2 代的市场采用正在顺利进行,但一些设计师仍然在他们的产品中依赖第 1 代,并且还没有准备好迁移到第 2 代。这些设计师可能没有意识到第 2 代正在带来更多的东西而不仅仅是额外的带宽。

开关成熟度

PCIe 开关是 PCIe 系统的标准构建块。由于芯片组提供有限数量的原生 PCIe 端口,因此交换机通常用于创建额外的 PCIe 端口。使用交换机允许芯片组扇出更多的 PCIe 端点或 I/O。

随着 PCIe 协议的成熟,它的实现也越来越成熟。芯片组过去带有一个 PCIe 端口,但现在通常支持多个 PCIe 端口。几年前,设计人员很难找到支持 PCIe 的嵌入式处理器。如今,支持两个甚至三个 PCIe 端口的嵌入式处理器很常见。

下一代功能

PCIe 交换机同样已经成熟。第 1 代交换机最初只是提供扇出功能,而第 2 代交换机则支持特定于应用程序的性能增强功能,例如读取步调和双播。

阅读节奏

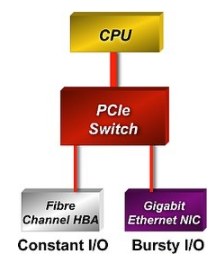

当今的服务器和存储系统混合使用通过连接到 PCIe 的适配器实现的恒定和突发 I/O 的情况并不少见。光纤通道主机总线适配器 (FC HBA) 是一个恒定的、需要大量数据的端点的示例,它大部分时间都在向主机发送大量读取请求。另一方面,千兆以太网网络接口卡 (GE NIC) 是一个本质上是突发性的端点,会根据需要向主机发送少量、不频繁的读取请求。

在标准 PCIe 系统中,如果 GE NIC 在 FC HBA 已经发出大约 8 个读取请求之后发送一个小的读取请求,则 GE NIC 必须等待 CPU 处理完所有 8 个 FC HBA 读取请求,然后再处理一个GE 网卡读取请求。因此,GE NIC 性能会受到影响,因为它要花费几个周期来等待接收其请求的数据。FC HBA 读取请求往往比 GE NIC 的请求更大且更频繁,这一事实只会加剧 GE NIC 性能下降。这个问题是 PCIe 协议和 CPU 用于处理传入读取请求的先进先出 (FIFO) 方案的副产品。

读取步调通过在处理读取请求时公平分配 CPU 带宽来解决这个难题。在图 1 中,读取步调允许 GE NIC 跳到待处理的 FC HBA 读取请求之前,从而显着减少 GE NIC 的最坏情况等待时间。PCIe 交换机无需等待所有排队的 FC HBA 读取请求得到服务,而是允许 GE NIC 读取请求在队列中向前跳转。

图1

虽然突发 I/O 性能可以体验 5 倍或更高的性能提升,但恒定 I/O 性能不会受到影响。read pacing 使用的算法考虑了恒定的 I/O 性能,并确保其性能不会下降。基于此算法,读取步调支持其自己的默认设置集合。但是,想要自定义读取步调功能的设计人员可以根据需要对自己的阈值进行编程。

双铸

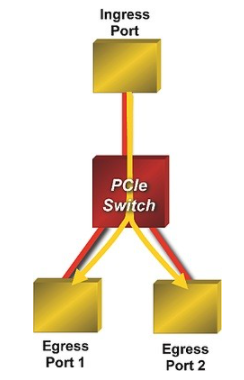

双播功能允许将一个入口数据包同时复制到两个出口端口——一个数据包输入,两个数据包输出。入口端口和两个出口端口是用户可编程的。每当数据包从选定的入口端口写入选定出口端口中的指定地址范围时,交换机都会自动生成出口数据包的副本并将该副本发送到第二个指定的出口端口。

在冗余和故障转移应用程序中,CPU 通常会将数据包的副本发送到冗余端点或辅助系统,以确保在系统崩溃时可以使用数据的备份副本。借助双重投射(如图 2 所示),PCIe 交换机减轻了 CPU 管理冗余流量的负担,将 CPU 需要执行的写入次数减少了一半。

图 2

调试和诊断链接

除了这些特定于应用的性能特性之外,最新的 PCIe Gen 2 交换机还提供了许多可以加速系统启动的集成调试和诊断特性。

PCIe 数据包生成器

内置的 PCIe 数据包发生器允许设计人员以全线速 (5.0 Gbps) 运行 PCIe 交换机的外部链路。这款可编程发生器使设计人员能够创建自己的流量模式,其强大功能足以使 x16 Gen 2 链路饱和。数据包生成器在系统调试和启动期间非常有用,允许设计人员针对可定制的高密度流量测试他们的系统。

性能监控

集成的实时性能监视器允许设计人员通过使用 PCIe 交换机的 GUI 设计工具查看每个端口上的入口和出口性能,因为流量通过交换机。性能监控是完全被动的,因此对整体系统性能没有影响。内部计数器为流量和数据包类型提供了广泛的粒度。此外,设计人员可以修改示例应用程序代码以允许进一步定制,例如流量过滤。此功能对于暴露性能瓶颈、识别未充分利用的链路以及优化系统性能非常有用。

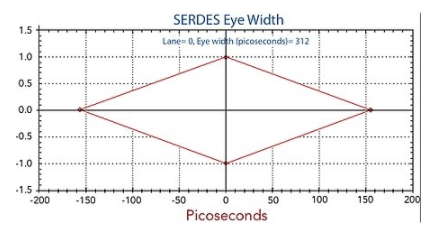

SERDES 眼图捕捉

设计人员可以使用开关的 SERDES 眼图捕捉功能在物理层评估系统的信号完整性,如图 3 所示。再次使用开关的软件工具,设计人员可以查看开关上任何通道的接收器眼图。此功能对于发现严重的信号完整性错误很有用,设计人员可以通过修改 SERDES 设置并查看调整对接收器眼图的影响来识别这些错误。

图 3

错误注入

错误注入允许设计人员将格式错误的数据包和/或致命错误注入他们的系统,从而使他们能够评估系统检测此类错误并从中恢复的能力。

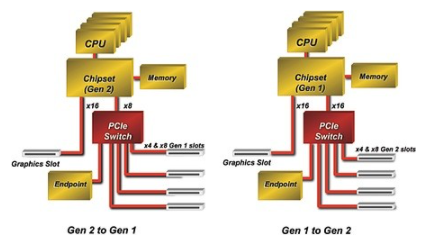

缩小差距

除了没有理解 PCIe Gen 2 除了额外带宽之外的好处之外,一些设计人员还没有意识到从 Gen 1 到 Gen 2 的过渡比看起来要简单得多。根据 PCI Express 基本规范修订版 2.0 的要求,PCIe Gen 2 向后兼容 Gen 1。因此,包括交换机在内的所有 PCIe Gen 2 设备都与所有 Gen 1 设备相连。如图 4 所示,第 2 代交换机可用作第 1 代到第 2 代的桥接器。

图 4

例如,使用传统 PCIe Gen 1 芯片组的设计人员可以使用 Gen 2 交换机连接到 Gen 1 端点。使用 Gen 2 交换机不仅提供各种性能和调试功能,还允许 Gen 2 端点之间的点对点流量以 5 Gbps 的速度运行,使 Gen 1 交换机提供的点对点性能翻倍。

相反,使用 Gen 2 芯片组的设计人员可以利用 Gen 2 交换机扇出到 Gen 1 端点。通过使用 Gen 2 交换机,设计人员可以利用 Gen 2 交换机内置的上述性能和调试功能,同时随着设计的发展获得连接到 Gen 2 端点的灵活性。

PCIe Gen 2 现在和现在

随着 PCIe 市场的不断扩大,PCIe 交换机的创新也在不断扩大。当今的第 2 代交换机提供高性能、集成的特定应用性能增强功能以及内置调试和诊断功能。插入第 2 代交换机是设计人员将其传统的第 1 代系统升级为支持第 2 代的最简单方法,从而使他们的系统在这个快速发展的市场中面向未来。

是呢环保局:郭婷

-

芯片

+关注

关注

463文章

54375浏览量

468986 -

交换机

+关注

关注

23文章

2926浏览量

104800 -

PCIe

+关注

关注

16文章

1474浏览量

88895

发布评论请先 登录

不仅仅是尺寸差异:工控场景下BNC与TNC连接器的抗振性能实战分析

深入剖析IDT5V41066:PCIe Gen1/2时钟合成器的卓越之选

DS 3.6.3 不包括完整的 MSYS2吗?

9FGL699:PCIe Gen2 6输出低功耗差分合成器深度解析

如何在 VF2 上编译东西?

浅谈PCIe交换机的拓扑结构和核心功能

INDEMIND助力会畅科技旗下OLLOBOT机器人OlloNi亮相CES 2026

Amphenol ICC的PCIe® M.2 Gen 5卡边缘连接器:高性能连接新选择

Amphenol HD Express®:满足PCIe® Gen 6需求的高性能互连系统

壹连科技CCS产品全球累计出货量突破一亿片

PCIe Gen 5 CEM连接器技术解析与选型指南

为FreeRTOS增加新的设备驱动程序

CYT2B93CAE怎样才能接收特定 ID 的中断?

晶体管架构的演变过程

PCIe Gen 2带来的东西不仅仅是额外的带宽

PCIe Gen 2带来的东西不仅仅是额外的带宽

评论