芯片的复杂度在日益增加,尤其是无人驾驶、医疗设备、航空航天等关键且重要的领域,芯片的设计规模和复杂度都在以指数级攀升。芯片是否能成功上市,验证非常关键,而故障仿真又是这一类芯片验证中极为重要的步骤。

那么开发者在做故障仿真时都会面临哪些挑战?为什么故障仿真要考虑功能安全?为什么说统一的验证方法是一大进步?在今天的文章中,我们会对这几个问题进行讨论。

故障仿真必不可少

故障仿真就是排查设计中的所有潜在故障,并确定这些故障是否都可以被检测出来。这一步骤通常是在设计完成即将流片时进行的,但开发者们都希望能将这一过程左移,因为如果真的有什么大问题需要修改,对设计进度将是巨大的影响。

有效的故障仿真会涵盖芯片生命周期的以下三个主要阶段:

芯片开发阶段:在这一阶段,故障仿真应该用于证明和记录设计与验证流程的鲁棒性。也就是说,故障仿真可以确保实现工具和流程不会引入设计缺陷(系统故障),且验证工具和流程能够准确报告所有设计缺陷,让开发者们能够针对漏洞进行修复。所以说,故障仿真还确保了设计验证方法拥有足够的鲁棒性,为零缺陷设计目标提供高可信度。

芯片制造阶段:在这一阶段,故障仿真可以通过监测DFT的功能测试向量,帮助减少随机故障导致的不良率(DPPM)。

实际运行阶段:故障仿真能证明并记录安全机制是否正常运行。安全机制会在出现故障时(且应当只在出现故障)被触发,他们能够有效的让设计进入安全状态。

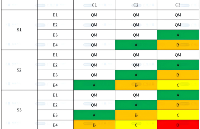

故障仿真的故障目标覆盖率(即诊断覆盖率)与安全关键程度息息相关。对安全性要求越高的应用,对故障仿真的目标覆盖率要求也会越高。比如说,与无线耳机的芯片相比,自动驾驶辅助系统芯片要求故障仿真的故障目标覆盖率要高达99%。但如果只能实现97%,开发者们应该怎么办呢?如何去收敛覆盖率差距呢?

在确定是否能够检测到设计中所有故障的同时,实现高诊断覆盖率对开发者来说也是一项非常艰巨的任务。在这个过程中需要用大量的测试平台和刺激测试激励,对芯片设计在各种场景下进行测试。但由于没有一个明确的方法来评估每个测试平台和激励对错误覆盖率的价值,往往无法确定这些测试序列是否足够。

而且,随着芯片设计变得越来越复杂,仿真运行需要花费的时间越来越长。对某些安全关键型应用的SoC设计来说,为了测量诊断覆盖率,需要对多达数百万个故障进行仿真以确保其功能安全合规性。毫不夸张地说,这一过程将给整个功能验证增加30%的工作量。

但无论如何,故障仿真是必不可少的。

故障仿真与功能验证

如何协同工作

功能验证,是对芯片设计中的各种功能模块进行测试,从而验证芯片设计是否符合预期。

故障仿真,即如果在设计中注入了会导致芯片设计失败的错误,这个错误能否被检测出来?或者更进一步地说,设计是否有足够的能力仍然可以正常运行?

功能验证和故障仿真都有自己的覆盖率指标。然而,为了提高效率,开发者通常会考虑如何利用功能验证中的测试机制进行故障仿真。功能验证和故障仿真都可以运行几乎无限数量的测试来对设计进行彻底验证。当然,“无限”并不能真正支持上市时间目标,因为手动编写软件测试库会耗费大量人力。因此,任何能将功能验证和故障仿真自动化的技术都可以极大地提高设计效率。

功能安全合规性也是一个需要讨论的重点问题。

安全关键型汽车应用需要符合ISO 26262功能安全标准。ISO 26262描述了一种被称为汽车安全完整性等级(ASIL)的风险分类系统,其目的是减轻电气和电子(E/E)系统故障行为产生的潜在危险。ASIL D代表最高风险等级,适用于ADAS等汽车应用。从故障仿真的角度来看,验证开发者需要进行稳健的诊断测试,以验证安全机制是否符合ISO 26262以及IEC 61508工业安全标准的要求。对于较高的风险等级(如ASIL D),覆盖率要求也更高,相关的安全机制应更具弹性、更可靠。

通过自动化加速故障仿真的

解决方案

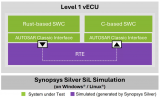

验证开发者们始终都面临着加快周转时间的压力,因此急需关键技术来减少故障注入的工作量。新思科技的统一功能安全验证平台,可以将自动化能力从功能验证拓展到故障仿真,从而为开发者提供有效的解决方案:

新思科技的VC Z01X™并行故障仿真解决方案,可将故障注入整个数字汽车设备,对故障的影响进行仿真,以促进稳健诊断测试的开发,并验证安全机制是否符合ISO 26262和IEC 61508的故障注入要求。新思科技 VC Z01X解决方案配备了各种报告机制,可帮助开发者了解设计中覆盖率低的原因和位置。有了这种洞察力,开发者可以更好地了解是需要编写新的测试模式还是需要进行对设计进行更改。

新思科技VC Functional Safety Manager,是一种可扩展、自动化、全面的功能安全失效模式后果分析(FMEA)和失效模式后果诊断分析(FMEDA)解决方案。

新思科技VC Formal™功能安全应用程序,能够提供全面的分析和调试。使用新思科技的Verdi®自动调试系统可查看示意图并注释发生故障的位置,快速确定根本原因,从而大大提高调试过程的效率。

新思科技TestMAX FuSa功能安全分析解决方案,能够在RTL或门级网表的设计流程早期执行分析,从而改进ISO 26262功能安全指标。

新思科技下一代电路仿真技术PrimeSim™ Continuum统一工作流程,具备仿真故障注入功能。

新思科技ZeBu®仿真系统,可加速故障仿真进程。

新思科技统一功能安全验证平台

通过使用该平台的VC Z01X组件,开发者可以将功能验证测试平台复用于故障仿真,因此无需再单独进行逻辑仿真。新思科技的VC Z01X解决方案除了能够加快覆盖率收敛的速度外,还可提供一个涵盖仿真、形式化和硬件加速的统一故障环境。

新思科技的统一功能安全验证平台让验证测试平台更智能。举个例子,假设现在有100个测试用例,在对测试平台和电路活动进行分析之后,平台可能会确定只有少部分用例提供了有价值的故障覆盖,而其他用例实际上都是在浪费仿真周期。

对于功能安全合规性,集成解决方案可以帮助开发者验证其ASIL目标是否已达成。

下一代故障仿真技术

会是怎样的发展?

故障仿真技术经过多年的发展,已经从以过程加速为目的的单元优化进化到更有效的内存仿真。新思科技采用了基于故障模型注入的技术,随着芯片尺寸的不断缩小,故障模型出现了一种新趋势,新的模型将会有新的体验,比如慢通孔、桥接和电磁干扰等。

日益复杂化的芯片设计将需要不断优化的新方法来缩短仿真时间。新思科技的统一功能安全验证平台为新方法的构建提供了基础。故障仿真固然重要,但其本身并不能解决一切问题,尤其是在功能安全方面。未来,开发者们需要一个从架构到综合再到布局的完整解决方案,既要利用故障仿真,也要利用所有其他类型的验证和调试功能,从而更好地帮助开发者缩短芯片开发周期,加速产品上市。

-

芯片

+关注

关注

463文章

54441浏览量

469421 -

SoC设计

+关注

关注

1文章

151浏览量

19603 -

新思科技

+关注

关注

5文章

979浏览量

52990 -

应用程序

+关注

关注

38文章

3346浏览量

60421

发布评论请先 登录

ISO 26262功能安全落地全流程解析

汽车零部件功能安全ASIL等级确定方法(二)

新思科技发布全新软件定义硬件辅助验证解决方案

RDMA设计35:基于 SV 的验证平台

探秘 CYSBSYSKIT - DEV - 01 快速物联网连接开发者套件

2025开放原子开发者大会AtomGit开源实践交流分论坛成功举办

2025新思科技开发者大会精彩回顾

NVIDIA DRIVE AGX Thor开发者套件重磅发布

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

推动硬件辅助验证平台增长的关键因素

新思科技VSO.ai如何颠覆芯片验证

新思科技统一功能安全验证平台可帮助开发者验证ASIL目标

新思科技统一功能安全验证平台可帮助开发者验证ASIL目标

评论