芯片行业对于流片都不陌生。所谓流片,就是像流水线一样通过一系列工艺步骤制造芯片,该环节处于芯片设计和芯片量产的中间阶段,是芯片制造的关键环节。简单来说就是将设计好的方案,交给芯片制造厂,先生产几片几十片样品,检测一下设计的芯片能不能用,然后进行优化。如果测试通过,就按照这样开始大规模生产了。所以为了测试集成电路设计是否成功,必须进行流片。这也是芯片设计企业一般都在前期需要投入很大成本的重要原因。一颗芯片从设计到量产,流片属于非常关键的环节。当芯片完全设计出来以后需要按照图纸在晶圆上进行蚀刻,采用什么样的制程工艺,多大尺寸的晶圆,芯片的复杂程度都会影响这颗芯片的流片成功率和成本,而且许多芯片都不是一次就能流片成功的,往往需要进行多次流片才能获得较为理想的效果。

流片为什么这么贵?

那芯片流片的价格为什么这么贵?这就要提到芯片的制造原理了。芯片制造要在很小的芯片里放上亿个晶体管,制造工艺已经到了纳米级,只能用光刻来完成。光刻就是用光刻出想要的图形,光刻需要用到掩膜版(又称光罩,Mask),掩膜版就是把设计好的电路图雕刻在上面,让光通过后,在晶圆上刻出图形。流片贵,一方面是因为刚开始有许多工艺需要验证,从一个电路图到一块芯片,检验每一个工艺步骤是否可行,检验电路是否具备所要的性能和功能。芯片流片过程至少持续三个月(包括原料准备、光刻、掺杂、电镀、封装测试),一般要经过1000多道工艺,生产周期较长,因此也是芯片制造中最重要最耗钱的环节。如果流片成功,就可以据此大规模地制造芯片;反之,就需要找出其中的原因,并进行相应的优化设计。其中,芯片流片贵,主要贵在掩膜版和晶圆,这两项价格不菲且都是消耗品,其中掩膜版最贵,一套中端工艺制程的掩膜版价格大约在50万美元左右,而一片晶圆的价额也在数千美元。

掩膜贵还是晶圆贵?

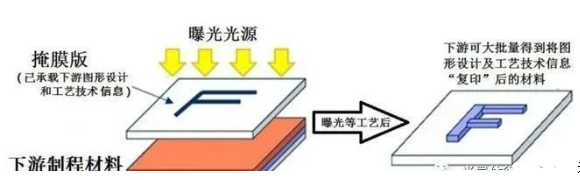

掩膜版是一种由石英为材料制成的,是微电子制造过程中的图形转移工具或母版,其功能类似于传统照相机的“底片”,根据客户所需要的图形,通过光刻制版工艺,将微米级和纳米级的精细图案刻制于掩膜版基板上,是承载图形设计和工艺技术等内容的载体。然后把这种从掩膜版的图形转换到晶圆上的过程,想象成印钞机的工作流程。把光刻机想象成印钞机,晶圆相当于印钞纸,掩膜就是印版,把钞票母版的图形印到纸张上的过程,就像光刻机把掩膜版上的芯片图形印到晶圆上一样。光刻需要用到掩膜版,掩膜版就是把设计好的电路图雕刻在上面,让光通过后,在晶圆上刻出图形。

光刻工作原理

掩膜版的质量会直接影响光刻的质量,掩膜版上的制造缺陷和误差也会伴随着光刻工艺被引入到芯片制造中。因此,掩膜版是下游产品精度和质量的决定因素之一。掩膜版的价格主要取决于芯片所选用的“工艺节点”,工艺节点越高、流片价格就越贵。这是因为越先进的工艺节点,所需要使用的掩膜版层数就越多。据了解,在14nm工艺制程上,大约需要60张掩膜版,7nm可能需要80张甚至上百张掩膜版。掩膜版层数多了,不仅仅是因为掩膜板的价格贵,还因为每多出一层 “掩膜板”,就要多进行一次“光刻”,就要再多涂抹一次 “光刻胶”,就要再多一次 “曝光”,然后再来一次 “显影” 。。。,整个流程下来耗费的成本就大大增加了。

如何降低流片成本?

1.对Foundry体系不了解,缺乏工艺选型的经验和Foundry打交道的经验;

2.主流Foundry准入门槛高,新兴玩家难以申请预期的工艺或支持,沟通成本高;

3.缺乏系统的供应链管理能力,尤其在量产产能爬坡阶段,对产能、交期、质量过于乐观;

4.产能紧缺情况下,缺乏备货机制,恐慌性下单或有了订单再下单导致产能跟不上市场需求。此外,交期的变化、产能的波动都会大大增加初创公司与晶圆代工厂的沟通成本,降低效率。

写在最后

一个芯片开发项目,需要经历从产品定义、设计、验证仿真一直到最终流片的漫长过程,对此,芯片设计企业、制造商以及相关的行业服务平台和机构应紧密合作,优势互补,携手解决困扰开发者的“流片难题”。

-

芯片制造

+关注

关注

11文章

713浏览量

30331 -

光刻机

+关注

关注

31文章

1196浏览量

48738 -

流片

+关注

关注

0文章

31浏览量

10000

发布评论请先 登录

全链条补贴!厦门:芯片流片补60%、EDA补30%、IP补30%

芯驰科技高端车规MCU E3620P成功流片并开启送样

新思科技LPDDR6 IP已在台积公司N2P工艺成功流片

英伟达下一代Rubin芯片已流片

今日看点丨优必选获得2.5亿大单;象帝先新一代“伏羲”架构芯片完成流片验证

微流控芯片的封合工艺有哪些

芯片流片首次成功率仅14%?合科泰解析三大破局技术

人工合成石墨片与天然石墨片的差别

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

芯片流片失败都有哪些原因

恒流方案大全

把3片的16位总线全部并联了,3片的16位总线直接黏在一起可以吗?

芯片流片的基础知识

PI发热片制作流程(上)

流片为什么这么贵?如何降低流片成本?

流片为什么这么贵?如何降低流片成本?

评论